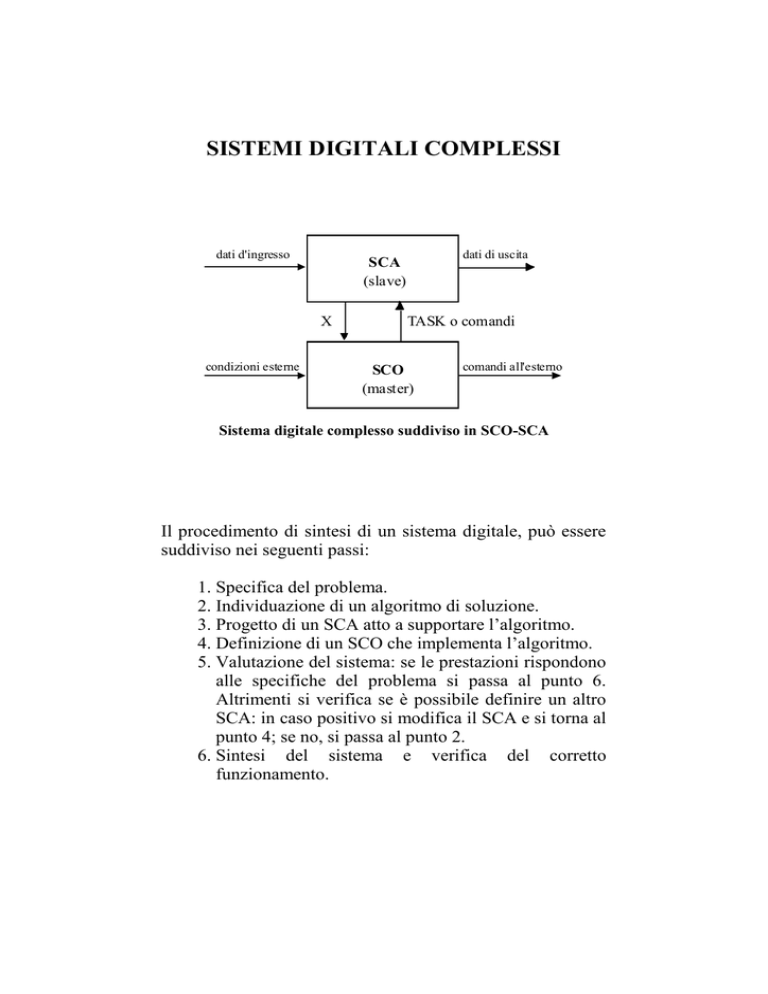

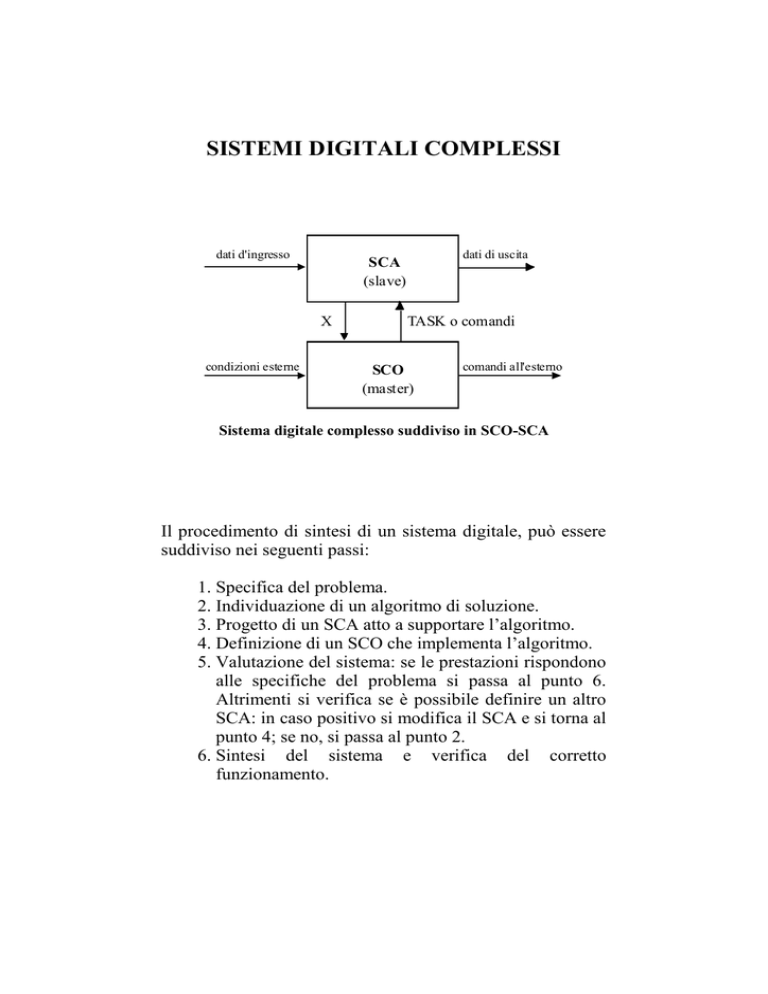

SISTEMI DIGITALI COMPLESSI

dati d'ingresso

X

condizioni esterne

dati di uscita

SCA

(slave)

TASK o comandi

SCO

(master)

comandi all'esterno

Sistema digitale complesso suddiviso in SCO-SCA

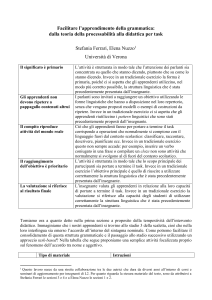

Il procedimento di sintesi di un sistema digitale, può essere

suddiviso nei seguenti passi:

1. Specifica del problema.

2. Individuazione di un algoritmo di soluzione.

3. Progetto di un SCA atto a supportare l’algoritmo.

4. Definizione di un SCO che implementa l’algoritmo.

5. Valutazione del sistema: se le prestazioni rispondono

alle specifiche del problema si passa al punto 6.

Altrimenti si verifica se è possibile definire un altro

SCA: in caso positivo si modifica il SCA e si torna al

punto 4; se no, si passa al punto 2.

6. Sintesi del sistema e verifica del corretto

funzionamento.

Sottosistema di Calcolo (SCA)

Registri, segnali e operazioni

D

Q

CK

EN

Cella di un registro

Un registro viene indicato con R, il suo contenuto con (R).

an-1

a0

b n-1

b0

A

B

Trasferimento dati tra due registri

en

ck

Operazioni tra dati contenuti in registri

OR :

(A) (B) = Y

somma logica bit a bit

esempio:

(0110) (1100) = 1110

AND :

(A) (B) = Y

prodotto logico bit a bit

esempio:

(0110) (1100) = 0100

NOT A:

(A) = Y

complementazione dei bit

esempio:

(0110) = 1001

EXOR : (A) (B) = Y

or esclusivo bit a bit

esempio:

(0110) (1100) = 1010

ADD :

(A) + (B) = Y

somma aritmetica

esempio:

(0110) + (1100) = 0010

SUB :

(A) - (B) = Y

sottrazione

esempio:

(0110) - (1100) = 1010

SR A, k:

shift right (scalamento a destra) di k posizioni

ai ai-k

i = n-1, ..., k

0 ah

h = n-1, ..., k

SL A, k:

ai ai+k

0 ah

shift left (scalamento a sinistra) di k posizioni

i = 0, 1, ..., n-k

h = 0, 1, ..., n-k

RR A, k:

rotate right (rotazione a destra) di k posizioni

ai ai-k

i = n-1, ..., k

ah an-k+h

h =0, 1,...., k-1

RL A, k:

rotate left (rotazione a sinistra) di k posizioni

ai a(i+k)mod n

i = 0, 1, ..., n

INC A, k:

(A) + k A

DEC A, k:

(A) - k A

EXCH A, B: (B) A

(A) B

Interconnessione registri-circuiti di calcolo

R1

R2

MUX

MUX

R3

R4

MUX

A

MUX

S

MUX

L

Esempio di interconnessione tra registri e circuiti di calcolo

dall'esterno

MUX

MUX

R1

MUX

R2

MUX

MUX

A

MUX

R3

MUX

R4

MUX

S

Interconnessione tra registri e circuiti di calcolo

MUX

L

Wt1

B1

B1

B2

B2

...

Wt2

Bn

Bn

TEMP2

TEMP1

R1

R2

W1

...

Rn

W2

ALU

shif ter

B

B

Wn

BA

SR

singola linea

linee multiple

Interconnessione tra registri e circuiti di calcolo tramite bus

BS

R0

AND

AND

R1

.

.

.

.

.

.

decoder

AND

AND

R7

AND

AND

RM

W

M

Organizzazione vettoriale dei registri

ld

R1

op

d

e

c address

o

d

e

r

R2

R3

R4

en

ld

ALU

op

en

S

TEMP

TEMP

ld

Interconnessione a bus tra registri e circuiti di calcolo

Esempio di interconnessione con tre bus

Sottosistema di Controllo (SCO)

La microprogrammazione

X

Z

Y

Y'

CK

Rappresentazione Algorithm State Machine

}

Implementazione di e tramite ROM

= microprogrammazione

Modello di Mealy

s

i1

case

im

T1

Tm

d1

dm

Modulo elementare della rappresentazione ASM per macchine di tipo

Mealy

La corrispondente microistruzione ha un formato del tipo:

i : C1(T1,i1), C2(T2,i2), . . . , Cm(Tm,im)

dove

C1, C2, . . . , Cm (m 2k , k = n) sono le condizioni derivanti

dalle variabili di decisione x1, x2, . . . , xn;

T1, T2,..., Tm sono le corrispondenti azioni da effettuare;

i1, i2,...,im le microistruzioni successive a i.

X

Z

Y

Y'

CK

Modello strutturale standard

SS

TASK

Struttura della parola di ROM

Se

- n è il numero delle variabili di ingresso

- m è il numero delle variabili di stato

allora

numero di parole = 2n+m

p.e., se

- n =20

-m=4

allora

numero di parole = 224

(16 Mega)

ECCESSIVO!!!!!

registro SEL

X

circuito

di

selezione

ck

R

X'

SEL

TASK

ROM

Y' (SS)

R

ck

Y (stato attuale)

registro di stato

Struttura del SCO nel caso di modello di Mealy

SEL

SS

TASK

Struttura della parola di ROM nel caso di modello di Mealy con

selezione

X4

X3

X2

X1

X2'

X1'

Esempio di circuito di mascheramento non codificato

Modello di Moore

s/T

case

i1

d1 / T1

im

dm / Tm

Modulo elementare della rappresentazione ASM per macchine di tipo

Moore

La corrispondente microistruzione ha un formato del tipo:

i : Ti; C1(i1), C2(i2),..., Cm(im)

dove

C1, C2,..., Cm (m 2k , k = n) sono le condizioni derivanti

dalle variabili di decisione x1,..., xn;

Ti è l’azione da effettuare;

i1,.., im le microistruzioni successive a i.

X

Y’

Y

ck

Task

Modello strutturale di Moore standard

TASK

ROM

SS1

SS2 . . . . . . SSm

multiplexer

'

X

Y'

ck

R

Y

Modello strutturale di Moore modificato

TASK

ROM

SEL

SS1

SS2 . . . . . . SS m

X'

multiplexer

circuito di

selezione

Y'

ck

R

Y

Struttura del SCO nel caso di modello di Moore con circuito di

selezione

SS1

SS2

..........

SSm

SEL

TASK

Parola di ROM nel caso di modello di Moore con circuito di

selezione

X

Sistemi multifase

0

X1

1

i

T ASKi

i+1

T ASKi+1

1

X2

0

j

T ASKj

j+1

T ASKj+1

1

X3

0

Frammento di sequenza di controllo

0

X1

1

i

TASK i

TASKi+1

1

X2

0

j

TASK j

1

TASKj+1

X3

0

Compressione del frammento di sequenza di controllo

T11

T12

SCO

Tk1

SCA

Tk2

Temporizzazione di due task per microistruzione

Controllo per strutture Pipeline.

TASK1

X1

TASK2

TASKN

X2

X3

X

Y

N

ck

Sistemi di calcolo a task fisso nel tempo

TASK1 (KT) TASK2 ((K-1)T)

X1

X2

X3

TASKN (K-N+1)T)

X

N

ck

Sistemi di calcolo a task variabile nel tempo

Y

ck

X

X

X

1

TASK1-1

TASK1-2 TASK1-3

2

TASK2-1 TASK2-2

3

TASK3-1

Xj

X

N

Y

Temporizzazione di una catena pipeline

TASK1(K)

TASK1(K-1)

TASK2(K)

TASK2(K-1)

TASK3(K)

TASK3(K-1)

TASK2(K-2)

SCO

TASK3(K-2)

TASK3(K-3)

CK

Architettura SCO per generare TASK sfasati nel tempo

Sistemi con molti microprogrammi

stato iniziale

sequenza

comune

OPCODE1

OPCODEN

OPCODE2

microprg.

1

microprg.

2

microprg.

N

Diagramma di flusso con più microprogrammi

LOAD

base

RESET

ROM

sel

spostamento

OPCODE

TASK

SEL

MUX

ck

X

Schema di SCO con molti microprogrammi (modello di Mealy)

RESET

base

LOAD

OP CODE

TASK

spostamento

ROM

SEL

SS1

SS2 . . . . . SSm

ck

multiplexer

X'

circuito di

selezione

X

Y'

Schema di SCO con molti microprogrammi (modello di Moore)

Comunicazione tra due sistemi digitali

UTx

URx

RDY1

Dato pronto

RDY2

FF1

FF2

ck1

RRx

Len2

RTx

Len1

ck2

ck1

ack1

ck2

ack2

FF3

ck1

Dato letto

FF4

ck2

Sincronizzazione di due unità in comunicazione

UTx

1: datoRTx, 1FF1;

2: if ack1=0, then vai a 2;

3: 0FF1;

4: if ack1=1, then vai a 4;

5: i+1i;

6: if iN, vai a 1

URx

1: 0FF4;

2: if RDY2=0, then vai a 2;

3: RTxRRx, 1FF4;

4: if RDY2=1, vai a 4 ;

5: i+1i;

6: if iN, vai a 1

Sequenze di microistruzioni eseguite da UTx e URx durante il

protocollo di comunicazione

1 d1ato

ACK =1

1

SI

2 0

i+1

i=N

SI

0

FF4

2 RTx

RRx

FF4

1

NO

i

NO

RDY=0

2

SI

3

NO

NO

RDY=1

2

SI

NO

FF1

ACK=0

1

SI

3

1

RTx

FF1

i+1

i=N

SI

i

NO

UTx

ack1

D

FF1

URx

Q

ck1

S

Q

sem

R

D

ck2

RDY2

FF2

Len2

RRx

RTx

Len1

ck2

ck1

Sincronizzazione tra due unità in comunicazione mediante flip-flop di

semaforo

1 Attesa sul sem

1 dato

RTx

Set sem

NO

RDY=1

2

SI

2 Attesa sul sem

ACK=0

1

SI

3

i+1

i=N

SI

2 RTx

RRx

Reset sem

NO

i

3

NO

i+1

i=N

SI

i

NO

Sequenze di microistruzioni eseguite da UTx e URx durante il

protocollo di comunicazione

UTx

1: datoRTx, set sem;

2: if ack1=0 vai a 2;

3: i+1i;

4: if iN, vai a 1;

URx

1: if RDY2=0, vai a 1;

2: RTxRRx, reset sem;

3: i+1i;

4: if iN, vai a 1;