UNIVERSITA’ DEGLI STUDI DI PARMA

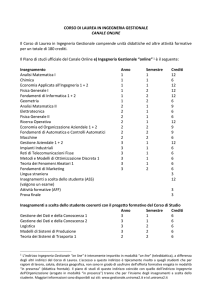

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Architettura dei calcolatori

elettronici

Prof. Michele Amoretti

Fondamenti di Informatica

a.a. 2007/2008

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Sommario

Architettura vs Organizzazione

Modelli architetturali

CPU

Memoria

Sottosistema di I/O

Strutture di interconnessione

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Architettura di un sistema di elaborazione

Riguarda le caratteristiche del sistema che sono visibili al

programmatore.

Fanno parte dell’architettura i seguenti aspetti:

• il numero di bit utilizzato per rappresentare i dati (numerici e

testuali)

• il numero di registri della CPU

• le modalità di indirizzamento

• il repertorio delle istruzioni

Con il termine modello di programmazione ci si riferisce a ciò che

vede il programmatore assembly, ovvero all’insieme dei registri

che egli può manipolare e al repertorio di istruzioni assembly.

In pratica il modello di programmazione è la traduzione in termini

di programmazione dell’architettura.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Organizzazione di un sistema di elaborazione

Riguarda le relazioni strutturali tra le unità funzionali e il modo in

cui esse realizzano una data architettura.

L’organizzazione di un calcolatore è tendenzialmente non visibile al

programmatore. Di essa fanno parte aspetti quali:

•

•

•

•

•

la tecnologia impiegata

la struttura interna di certi moduli funzionali

la frequenza di clock

il modo in cui viene eseguita una data istruzione

il modo in cui vengono trasferiti i dati da una unità funzionale

all’altra

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Perché distinguere i due concetti?

Mantenendo la stessa architettura si può passare da un modello di

calcolatore meno potente a uno più potente mantenendo inalterato

il software (sia quello di sistema che quello applicativo).

La compatibilità architetturale è stata una delle chiavi del successo

dei sistemi Intel.

Con il microprocessore 8086, introdotto nel 1978, è stata definita

un’architettura (x86) che, seppure con aggiunte e miglioramenti, è

arrivata ai giorni nostri e a quella che oggi viene chiamata IA32.

Lungo questo percorso sono state impiegate nuove tecnologie

microelettroniche e nuove strategie organizzative, ma è stata

mantenuta la compatibilità (programmi eseguibili su un 8086 sono

eseguibili anche su un Pentium 4).

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Modelli architetturali

Un sistema di elaborazione, in generale, è una macchina che accetta

in ingresso informazioni codificate in forma digitale, le elabora e

produce informazioni in uscita.

I

-

blocchi funzionali che lo compongono sono:

CPU (central processing unit - in italiano processore)

memoria

sistema di ingresso/uscita

Un computer, rispetto a una macchina calcolatrice convenzionale, ha

in più il concetto di programma memorizzato.

Dati e istruzioni nella stessa memoria: modello di Von Neumann.

Dati e istruzioni in memorie separate: modello Harvard.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Modello di Von Neumann

Lo schema si basa su cinque componenti fondamentali:

1.

2.

3.

4.

5.

CPU, che si divide a sua volta in

1. Unità operativa, nella quale uno dei sottosistemi più rilevanti è

l'ALU (Arithmetic Logic Unit)

2. Unità di controllo

Unità di memoria, intesa come memoria principale (la RAM) che

contiene sia i dati da elaborare che le istruzioni da eseguire

(programma)

Unità di input, tramite la quale i dati

vengono inseriti nel calcolatore per

essere elaborati

Unità di output, necessaria affinché

i dati elaborati possano essere restituiti

all'operatore

Bus, un canale che collega tutti i

componenti fra loro

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Schema architetturale di un PC moderno

CPU2

CPU1

Bus host

Bus AGP

Memoria

principale

North bridge

Slot PCI

Bus PCI

EIDE

USB

Slot ISA

South bridge

Bios

Architettura dei calcolatori elettronici

Bus ISA

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

CPU

La figura rappresenta lo schema più semplice di CPU, a livello RTL,

secondo il modello di Von Neumann.

Vi sono 5 registri principali: DR, AR, PC, IR, ACC.

Vi è anche una ALU che esegue le operazioni aritmetico-logiche.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

CPU

DR (Data Register) - Memorizza i dati provenienti e diretti alla

memoria.

AR (Address Register) - Memorizza gli indirizzi da comunicare alla

memoria.

PC (Program Counter o Contatore di Programma) - Memorizza

l'indirizzo della istruzione da eseguire.

IR (Instruction Register) - Memorizza il codice dell'istruzione da

eseguire.

ACC (Accumulator) – Immagazzina dati in ingresso e in uscita

dalla ALU.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Ciclo base

Per una qualsiasi istruzione:

• FETCH:

• ESECUZIONE:

Lettura dell'istruzione in memoria.

Lettura dei dati necessari.

Svolgimento dell'operazione.

La fase di FETCH consente l'acquisizione della nuova istruzione.

La fase di ESECUZIONE consente lo svolgimento della operazione.

La fase di FETCH è eguale per tutte le istruzioni che ovviamente si

differenziano nella fase di ESECUZIONE.

Al termine della fase di ESECUZIONE viene eseguita la fase di

FETCH della istruzione successiva.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Ciclo base

Ogni istruzione contiene in modo esplicito o implicito l’indicazione

dell’istruzione successiva.

Modo esplicito: il codice dell’istruzione contiene l’indirizzo della

cella di memoria dove è contenuta l’istruzione successiva.

Modo implicito: l’indirizzo della istruzione successiva è contenuto

in un registro interno alla CPU.

La sequenza delle istruzioni è definita dal programma.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Ciclo base

Con riferimento alla figura, la fase di FETCH consiste nelle

seguenti operazioni di trasferimento dati tra registri:

AR PC

DR M(AR)

IR DR

; lettura in memoria dell’istruzione

; codice di istruzione all’unità di controllo

Prima di iniziare la fase di esecuzione,

si aggiorna il PC con l’indirizzo

dell’istruzione successiva.

Attenzione! l’istruzione successiva

non è per forza nella successiva

cella di memoria (vedi salti e chiamate

a sottoprogrammi).

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Lo stack

Lo stack (pila) è una struttura dati gestita secondo una politica LIFO

(last in – first out).

La possibilità di gestire uno stack in memoria è comune a molte

architetture. In tal caso il repertorio delle istruzioni prevede le

operazioni

PUSH – inserimento di un dato nello stack

POP – prelievo di un dato dallo stack

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Lo stack

Per la gestione dello stack servono due registri:

BP (Base Pointer) – punta entro lo stack come se si trattasse di una

normale area di memoria

Es. LOAD R,[BP+8]

carica in R il contenuto della cella dello stack

il cui indirizzo è dato dalla somma del

contenuto di BP con 8

SP (Stack Pointer) – punta sempre alla testa dello stack e viene

aggiornato ad ogni esecuzione di una operazione PUSH o POP; non può

essere impiegato come indicato sopra per BP

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Lo stack

Lo stack viene utilizzato per:

- salvare temporaneamente il contenuto dei registri prima

dell’esecuzione di un sottoprogramma (procedura)

- depositare i parametri passati a un sottoprogramma

Es. una istruzione di alto livello del tipo

y = f(x1, x2, …, xn);

viene tradotta dal compilatore in una sequenza di PUSH dei parametri, a

partire dall’ultimo, seguita dall’istruzione di chiamata a f; il valore y

viene reso attraverso un registro predefinito (sempre lo stesso, per una

data architettura).

Per accedere ai parametri nello stack, il sottoprogramma usa il BP.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Interruzioni

•

•

•

Eventi infrequenti ed eccezionali.

Generati internamente o esternamente.

Causano il trasferimento del controllo dal programma corrente a un

programma specifico di servizio dell'evento.

Classificazione:

1. Interruzioni esterne (external interrupt o device interrupt): in

genere usate per gestire le operazioni di I/O, si verificano in modo

asincrono rispetto all’esecuzione del programma.

2. Eccezioni (exception conditions): causate da situazioni anomale

rilevate durante l’esecuzione del programma, si verificano in modo

sincrono; esempio: divisione per zero.

3. Trappole (traps): generate da apposite istruzioni presenti nel

programma (es. istruzione INT del processore 8086), si verificano in

modo sincrono e sono predicibili – in pratica sono particolari

operazioni di salto.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Interruzioni

• La presenza di un interrupt è segnalata alla CPU da una linea

proveniente dall'esterno (o da un segnale interno).

• Il segnale è testato dalla CPU alla fine di ogni ciclo di istruzione.

• La CPU risponde trasferendo il controllo a un altro programma.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Interruzioni

Ancora sulle azioni della CPU in risposta alla richiesta di interruzione:

• Lo stato complessivo della CPU viene memorizzato nello stack a cura

del programma di gestione.

• Nel PC viene immagazzinato l'indirizzo del sottoprogramma di

gestione.

• L'esecuzione del sottoprogramma continua fino all'istruzione di

RETURN che riporta il controllo al programma interrotto.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

La codifica delle istruzioni a basso livello

Un possibile formato per la codifica di istruzioni su parole di 32 bit:

0

31

OP

Es.

R

Indirizzo

LOAD R,Var

LOAD è il codice mnemonico per l’operazione di trasferimento dati

dalla memoria. R è il registro destinazione. Var è il nome simbolico

di una posizione di memoria (indirizzo). Quindi l’istruzione equivale

all’istruzione RTL

R M[Var]

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

La codifica delle istruzioni a basso livello

Un altro possibile formato per la codifica di istruzioni su parole di 32 bit:

0

31

OP

Es.

Ra

Rb

Rc

ADD R1,R2,R3

ADD è il codice mnemonico per l’operazione di somma. R1 è il registro

destinazione. R2 e R3 sono i registri che contengono gli addendi. Quindi

l’istruzione equivale all’istruzione RTL

R1 R2+R3

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Unità di controllo

Le connessioni non sono attive tutte contemporaneamente.

L’unità di controllo seleziona i cammini che risultano attivi in un

determinato istante.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Caratteristiche di un set di istruzioni

COMPLETEZZA:

• Deve essere possibile valutare qualunque funzione che sia

calcolabile con una disponibilità ragionevole di memoria.

EFFICIENZA:

• Istruzioni usate frequentemente devono essere eseguite

rapidamente.

• Il controllo sull'efficienza deve essere misurato sul codice

generato da compilatori.

• Fornire primitive, non soluzioni.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Caratteristiche di un set di istruzioni

REGOLARITA’:

• Le istruzioni devono comportarsi in modo omogeneo rispetto

ai modi di indirizzamento.

• Quando ogni istruzione consente tutti i modi di

indirizzamento possibili su tutti gli operandi: ORTOGONALITA'

COMPATIBILITA’:

• Compatibilità sorgente: sono compatibili i codici mnemonici

del linguaggio assembler.

• Compatibilità binaria: sono compatibili i codici macchina.

• Il codice macchina deve essere eseguibile su processori

successivi della stessa famiglia.

• 8080 8086 80186 ... Pentium ...

• PDP11 VAX

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Tipi di istruzioni

TRASFERIMENTO DATI

MOVE

Trasferisce dati tra registri

LOAD

Trasf. dati dalla memoria

STORE

Trasf. dati alla memoria

EXCHANGE

Scambia dati

SET/RESET

Pone ad 1/0

PUSH/POP

Gestione stack

OPERAZIONI

ADD/SUB

MULT/DIV

ABS

NEG

INC/DEC

ARITMETICHE

Somma/differenza

Moltiplicazione/divisione

Valore assoluto

Cambio segno

Incrementa/decrementa

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Tipi di istruzioni

OPERAZIONI LOGICHE

AND

OR

NOT

XOR

OPERAZIONI PER LA MANIPOLAZIONE DEI BIT

SHIFT

traslazione

ROTATE

rotazione

CONTROLLO

JUMP

JUMP COND

CALL (COND)

RET (COND)

DEL FLUSSO

salto incondizionato

salto condizionato

salto a sottoprogramma

uscita da sottoprogramma

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Tipi di istruzioni

CONTROLLO CPU

HALT

blocco operazioni

WAIT/HOLD

blocco operazioni con ripresa condizionata

NOP

non svolge operazioni

INGRESSO E USCITA

INPUT (READ)

trasferimento dati da I/O verso memoria o

registro

OUTPUT (WRITE)

trasferimento dati verso porta di I/O

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Repertorio stile CISC

CISC = Complex Instruction Set Computers

Criteri di progettazione:

• le istruzioni non hanno dimensione fissa

• il campo del codice di operazione può occupare più o meno bit

• numero ampio di formati: il codice di operazione non identifica

univocamente il formato delle istruzioni, e da un formato all’altro i campi

che identificano uguali entità possono occupare differenti posizioni

Esempi di processori CISC:

Intel x86, Zylog Z80, Motorola 68000

Il mondo dei PC desktop e laptop è dominato dalla famiglia Intel x86 che

continua ad adottare lo stile CISC per mantenere la compatibilità con le

applicazioni.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Repertorio stile RISC

RISC = Reduced Instruction Set Computers

Criteri di progettazione:

• le istruzioni hanno tutte la stessa dimensione (es. 32 bit)

• il campo del codice di operazione occupa uno spazio predefinito

• numero molto limitato di formati: il codice di operazione identifica

univocamente il formato dell’istruzione, e nel passare da un formato

all’altro i campi che identificano uguali entità occupano sempre la

stessa posizione

Esempi di processori RISC:

IBM PowerPC, Intel i880 e i960, AMD 29000, Sun SPARC

Utilizzati per: telefoni cellulari, palmari, automobili, console.

Inoltre i processori RISC, dagli anni 90, sono i dominatori

incontrastati dei server ad alte prestazioni.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

CISC o RISC?

Prima degli anni 80 si riteneva che repertori estesi di istruzioni

fossero preferibili, per facilitare la costruzione di compilatori.

L’uso efficiente della memoria centrale (allora costosa e poco

performante) era il primo obiettivo di qualunque soluzione

architettonica. Repertorio esteso significa programmi più corti che

occupano meno memoria ma che richiedono una unità di controllo

più complessa. La memoria di controllo era più veloce di quella

centrale, per cui portare funzionalità nella prima avrebbe comunque

migliorato le prestazioni della macchina.

Con l’avvento delle memorie a semiconduttore (che rimpiazzarono

quelle a nuclei magnetici) e delle memorie cache, e la constatazione

che l’80% delle istruzioni eseguite corrisponde al solo 20% del

repertorio esteso, presero piede i microprocessori RISC.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Storia dei microprocessori

Il termine microprocessore venne usato per la prima volta da Intel

nel 1971, quando introdusse un computer microprogrammabile su

un unico chip, la CPU Intel 4004 era completa di:

- sommatore parallelo a 4 bit

- 16 registri a 4 bit

- un accumulatore

- uno stack

Frequenza massima di clock: 740KHz.

Con l’aggiunta di memorie di tipo RAM e ROM, la CPU 4004

costituiva il sistema MCS-4.

Realizzata con la stessa tecnologia, nel 1972 uscì la CPU

Intel 8008, la prima in grado di operare a 8 bit.

Frequenza massim di clock: 800KHz.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Storia dei microprocessori

I microprocessori a 8 bit sono detti di prima generazione.

La grande diffusione di questi dispositivi inizio nel 1974, con

l’introduzione della CPU Intel 8080, con frequenza di clock

massima di 2MHz.

I concorrenti erano il Motorola MC6800 (prodotto a basso costo

perchè fu il primo ad avere alimentazione singola), e lo Zilog Z80

(che incorporava il repertorio di istruzioni dell’8080 e quindi aveva

piena compatibilità con i programmi scritti per quella CPU).

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Storia dei microprocessori

Fu l’Intel 8086, messo sul mercato nel giugno 1978, a inaugurare

la seconda generazione di microprocessori, capaci di operare su

16 bit alla volta.

L’8086 indirizzava 1MB di memoria e lavorava alla frequenza di

5MHz, per una capacità media elaborativa di 0,33 MIPS (milioni di

istruzioni per secondo).

L’8086 definì le basi dell’architettura x86.

L’Intel 8088 (un 8086 con bus esterno a 8 bit) venne adottato a

IBM per costruire il suo PC (Personal Computer), che ebbe un

successo enorme anche grazie al software Microsoft.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Storia dei microprocessori

Il principale concorrente dei processori Intel

8086/88 era il Motorola MC68000.

Pur avendo caratteristiche leggermente superiori all’8086, il

ritardo di due anni con cui il 68000 arrivò sul mercato pregiudicò

la loro affermazione.

Il 68000 ebbe comunque ottima accoglienza nel mercato delle

cosiddette workstation, per i quali il sistema operativo Unix era la

norma. Sun Microsystems e HP (i più accreditati costruttori di

workstation) per anni adottarono il 68000.

Il declino del 68000 iniziò con con l’ingresso delle architetture

RISC nel mercato delle workstation. Sun, in particolare,

abbandonò Motorola e sviluppò una propria architettura (SPARC).

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Storia dei microprocessori

A un certo punto, le CPU a 16 bit entrarono in una fase di grande

crescita, e apparvero componenti di corredo avanzati come gestori

di memoria (MMU), unità aritmetiche in virgola mobile (FPU),

controllori di accesso alla memoria (DMA).

1984:

1985:

1987:

1989:

1990:

MC68020

Intel 80386

MC68030

MC68040

Intel 80486

www.intel.com/pressroom/kits/quickreffam.htm

Dal 1991: PowerPC di IBM, Apple e Motorola (AIM)

Dal 1993: Intel Pentium e compatibili (es. AMD)

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

La legge di Moore

Nel 1965 Gordon Moore (che con Robert Noyce e Andy Groove

fonderà Intel nel 1968) in un articolo sulla rivista Electronics

ipotizzò che l’aumento della capacità elaborativa (intesa come

numero di transistori nel singolo chip) sarebbe continuato, per

tutti gli anni ’70, al ritmo di un raddoppio ogni 12 mesi.

Nel 1975 Moore fece una

prima correzione: raddoppio

ogni 2 anni.

A fine anni ’80 si corresse

ancora e diede la stima che

tutt’oggi è il metro di misura

e l’obiettivo per le aziende

che operano nel settore:

raddoppio ogni 18 mesi.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria

Parametri di valutazione:

Dimensione (nel senso di capacità) – data in bit o byte; spesso la dimensione

viene riportata in modo da descrivere l’organizzazione interna.

es. 64K x 8 bit indica una memoria di 65536 celle di 8 bit ciascuna.

Velocità – indicata come tempo di accesso (intervallo di tempo tra la richiesta del

dato e il momento in cui viene reso disponibile).

Potenza – questo parametro indica la potenza media assorbita.

Costo – il parametro più aleatorio, dipende anche dal volume di acquisto.

Integrazione – maggiore l’integrazione, minore l’ingombro e il consumo e i costi

di assemblaggio delle parti, dell’alimentazione e dello smaltimento del calore.

Idealmente un calcolatore dovrebbe avere quanta più memoria possibile,

ad alta velocità, basso consumo, basso ingombro e minimo costo.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria

La tecnologia consente di realizzare CPU sempre più veloci. Nel 2006

sono stati messi sul mercato processori con frequenza di clock

superiore ai 3GHz.

Purtroppo le memorie non sono così veloci, cioè non hanno tempi di

accesso paragonabili al periodo di clock delle CPU attuali.

ns

200

Le prestazioni delle CPU non

devono essere troppo

negativamente influenzate dal

tempo di accesso alle memorie.

Tempo di accesso

memoria

100

Tempo di ciclo

CPU

1980

1990

2000

Architettura dei calcolatori elettronici

In aiuto al progettista viene la

proprietà di località spaziale e

temporale esibita dai

programmi.

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Principio di località

La modalità di accesso ai dati è in genere prevedibile, cioè vale il

principio per cui

se al tempo t si accede all'indirizzo X è

"molto probabile" che l'indirizzo X+X

sia richiesto fra t e t+ t.

Questo significa che nel breve periodo gli indirizzi generati da un

programma sono confinati in regioni limitate.

La distribuzione degli accessi alla memoria

in un dato intervallo può essere misurato

direttamente su un sistema.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Gerarchie di memoria

Idealmente un calcolatore dovrebbe avere quanta più memoria

possibile, ad alta velocità, basso consumo, basso ingombro e

minimo costo.

Non è possibile avere un’unica memoria con tutte queste

caratteristiche, ma il principio di località suggerisce di realizzare

una gerarchia:

- memorie piccole e veloci (e costose) ai livelli alti, vicino alla CPU;

- memorie ampie, più lente (e meno costose) ai livelli più bassi.

CPU

Memoria

M1

Architettura dei calcolatori elettronici

Memoria

M2

…

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Gerarchie di memoria

Memoria

M2

Memoria

M1

CPU

…

A diversi livelli, le memorie sono realizzate con tecnologie diverse.

Costo per bit: c1 > c2 > …

Tempi di accesso: tA1 < tA2 < …

Dimensioni: S1 < S2 < …

Un tipico sistema di memoria è il seguente:

• memoria interna alla CPU

•

•

•

•

memoria

memoria

memoria

memoria

ROM

cache

principale

secondaria

Architettura dei calcolatori elettronici

c

tA

S

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Gerarchie di memoria

I criteri di gestione si rifanno al principio di località:

• I dati utilizzati più spesso vanno posti in memorie facilmente

accessibili.

• I dati utilizzati più raramente sono posti in memorie con tempi di

accesso elevato.

• Allocazione dinamica per utilizzare gli spazi disponibili con la

massima efficienza.

• Spostamento automatico dei dati tra i livelli.

• Canali di comunicazione veloci fra i livelli.

Questa politica di gestione tende a mimare una memoria che abbia:

• i tempi di accesso della più veloce,

• le dimensioni della maggiore,

• i costi della più economica.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria virtuale

All’inizio dell’era informatica le memorie erano costose e poco capienti.

I programmatori impiegavano molto tempo nel tentativo di

assottigliare i programmi perché entrassero in memorie minuscole.

Quando il programma era troppo grande, veniva messo nella memoria

secondaria diviso in pezzi, ciascuno dei quali poteva entrare in

memoria principale. I pezzi venivano portati nella memoria principale

ed eseguiti uno alla volta.

La gestione di questo procedimento era interamente nelle mani dei

programmatori.

Nel 1968 un gruppo di ricercatori propose di automatizzare questo

processo separando i concetti di spazio degli indirizzi e di locazioni di

memoria.

Questo metodo è oggi chiamato MEMORIA VIRTUALE.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria virtuale

Ad es. una CPU a 16 bit vede uno spazio degli indirizzi che va da 0 a

65535 (216 parole di memoria virtuale). La memoria principale può

avere comunque, fisicamente, meno di 65536 locazioni (supponiamo

4096).

Indirizzi utilizzabili dal programma: indirizzi virtuali (o logici).

Indirizzi effettivi della memoria principale: indirizzi fisici.

Esiste una corrispondenza (se necessaria) tra indirizzo logico e

indirizzo fisico.

La corrispondenza prende il nome di allocazione, ed è una funzione f

tale che:

indirizzo fisico = f(indirizzo logico)

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria interna alla CPU

Registri interni alla CPU:

- visibili o no al programmatore

- memorizzano temporaneamente dati e istruzioni

- dimensione: qualche byte

- tempo di accesso: qualche ns

In tempi recenti si è iniziato a collocare sullo stesso chip della CPU

anche memorie di tipo cache.

Nelle CPU più recenti cresce la quantità di risorse dedicate alla

memoria:

– 1980: processori senza cache (I386)

– 1995: Alpha 21164 55% dei transistor

– 2000: Merced (Intel-HP) 85% dei transistor

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria ROM

- memoria elettronica (è una matrice logica)

- ad accesso casuale (il tempo di accesso a una cella è indipendente

dalla sua posizione)

- a sola lettura

Impiegata per contenere i programmi che inizializzano la macchina

all’atto dell’accensione e il nucleo di base del sistema operativo.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria cache

La cache è una memoria veloce e di piccole dimensioni posta fra la

CPU e la memoria principale.

La cache e la memoria principale formano una gerarchia di memoria.

CPU

Memoria

Cache

Memoria

Principale

I tre livelli di memoria:

Cache - Memoria principale - Memoria secondaria

sono gestiti come due gerarchie a due livelli:

• Memoria principale - Memoria secondaria.

• Cache - Memoria principale.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria cache

Le prestazioni della memoria cache dipendono anche dalla sua

posizione rispetto alla CPU:

• cache su scheda

• cache su chip

La presenza di una memoria cache sullo stesso chip del processore

rappresenta la soluzione che garantisce la maggiore efficienza.

Nei sistemi più recenti sono presenti entrambe le soluzioni.

CPU

Cache

L1

CHIP

Architettura dei calcolatori elettronici

Cache

Cache

L2

L3

Memoria

Principale

SCHEDA

MADRE

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria cache

Ciclo delle operazioni:

Un indirizzo fisico viene inviato dalla CPU.

La cache confronta la parte rilevante dell'indirizzo.

Se vi è {hit} viene completato il ciclo.

In caso di {miss} la cache inizia la lettura da memoria principale di

dati che comprendono quello richiesto.

Politiche di sostituzione come per la memoria virtuale.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria principale

- memoria elettronica

- ad accesso casuale

- in lettura/scrittura

Contiene i programmi che la CPU esegue e i dati cui la stessa CPU può

accedere direttamente.

L’informazione scompare se viene meno la tensione di alimentazione.

E’ veloce e di grande capacità (decine-centinaia di Mbyte).

Genericamente parlando, viene indicata come RAM (Random Access

Memory). Viene divisa in SRAM e DRAM a seconda della modalità

(statica o dinamica) in cui l’informazione viene memorizzata.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria principale

Schematizazione dello spazio di memoria diviso in blocchi contigui di

dimensione C (celle) e realizzazione circuitale.

I due bit più significativi dell’indirizzo vengono decodificati per selezionare

l’integrato corrispondente a uno dei blocchi di dimensione C.

Le restanti log2C linee del bus degli indirizzi vengono collegate ai piedini

corrispondenti sugli integrati.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria principale

Struttura interna di ciascun

blocco di dimensione C=2N

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria principale

Schema di principio di un bit di memoria RAM statica (SRAM):

Il singolo flip-flop si realizza con 4 o 6 transistor, quindi su piccola o

media scala con tempi di accesso piuttosto bassi (da qualche nsec a un

centinaio).

L’assorbimento di potenza non è trascurabile, specialmente per i tipi

più veloci, per cui le memorie SRAM sono utilizzate per realizzare i

registri della CPU e memorie di piccole dimensioni come la cache.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria principale

Nelle memorie RAM dinamiche (DRAM) l’informazione è rappresentata

attraverso la carica immagazzinata in un condensatore integrato MOS.

E’ richiesto un solo transistore per bit;

la capacità viene ricavata sulla struttura

del transistore stesso, ottimizzando lo

spazio occupato.

Linea indirizzi

Linea dati

50pC

Condensatore carico: 1

Condensatore scarico: 0

La carica si esaurisce in pochi millisecondi, per cui deve esserci

un’operazione periodica di rinfresco (lettura e riscrittura) eseguita da

un circuito interno alla memoria stessa.

Questo comporta un certo dispendio di energia e rendono più lenta la

memoria (in fase di refresh l’accesso è negato).

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria principale

Ancora sulle memorie DRAM:

anno

1980

1983

1986

1989

1992

1995

2000

2002

2006

dimensioni

64 Kbit

256 Kbit

1 Mbit

4 Mbit

16 Mbit

64 Mbit

512 Mbit

1 Gbit

4 Gbit

t di ciclo

250 ns

220 ns

190 ns

165 ns

140 ns

120 ns

100 ns

70 ns

50 ns

Nel 2006: 0,1 $ per MB

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria secondaria

- memoria magnetica o ottica o a stato solido

- ad accesso seriale o semi-casuale o casuale

- in lettura/scrittura

Dispositivi quali nastri magnetici, floppy, dischi rigidi, CD-ROM,

memorie flash rapresentano memorie non volatili, con tempi di accesso

decisamente maggiori rispetto alla memoria principale.

Lo scopo delle memorie ausiliarie è quello di conservare in modo

persistente grandi quantità di dati.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria secondaria

NASTRI MAGNETICI, DISCHI MAGNETICI E OTTICI

• Condividono il sistema (o testina) di lettura e scrittura tra diverse

locazioni di memoria.

• La sequenza di locazioni che condivide la stessa testina si chiama

traccia.

• L'accesso alla locazione di memoria avviene spostando la testina o la

traccia.

• La traccia o parte di essa deve essere letta completamente per

accedere al singolo dato.

• Le memorie ad accesso seriale hanno raggiunto con la tecnologia

magnetica e ottica costi per bit estremamente bassi.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria secondaria

Un disco rigido consiste di un certo numero di piatti di alluminio

ricoperti da materiale magnetico. Attualmente il diametro dei piatti

varia da 3 a 12 cm, e un disco rigido ospita da 1 a 20 piatti.

I piatti sono in perenne rotazione (tra 3600 e 7200 giri/min, ma ci

sono anche dischi che vanno a 15000 giri/min).

I dati sulla superfice del disco sono scritti in cerchi concentrici che sono

denominate tracce.

Ogni traccia è divisa in settori (da 512 byte, ma anche 1024 e 2048

byte), ciascuno contenente un gruppo di dati con le informazioni per

correggere eventuali errori e un preambolo per la sincronizzazione.

L’insieme delle tracce che stanno su di un cerchio di dato raggio

costituisce un cilindro.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria secondaria

Le testine di lettura/scrittura sono solidali tra loro, ma solo una alla

volta legge/scrive in un certo istante.

L’accesso è semi-casuale perché per poter effettuare una operazione di

lettura/scrittura occorre prima portare la testina sulla traccia e poi

attendere che il settore cercato passi sotto di essa.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria secondaria

Le memorie seriali hanno tempi di accesso elevati perché:

•

•

•

•

Occorre tempo per posizionare la testina di lettura.

La traccia si muove a velocità ridotta.

Il trasferimento dati è seriale.

La testina di lettura è condivisa fra più tracce.

- seek time (tseek): tempo necessario a portare la testina sulla traccia

- latency time o latenza di rotazione (tlat): è il tempo medio speso

nell’attesa che il settore passi sotto l’unità di lettura/scrittura

- velocità di rotazione del disco (r): si misura in giri al secondo (rps)

- tempo di trasferimento (ttrasf): è il tempo richiesto per trasferire un

settore (valori usuali sono compresi tra 2 e 15 MB/s)

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria secondaria

Si noti che:

tlat = (2r)-1

Il tempo di accesso viene definito come:

tacc = tseek + tlat + ttrasf

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria secondaria

Un CD-ROM è un disco di policarbonato con una superficie di alluminio

riflettente protetta da un film di resina.

Le informazioni sono memorizzate come successioni di "buchi" (pits) e

"terre"(lands) nel policarbonato, letti per mezzo di un laser. I dati su di

un CD sono memorizzati a spirale.

La velocità di scansione è di 1,2 m/s costante con una velocità di

rotazione che varia da 500 (settori esterni) a 200 giri/min (settori

interni).

I dati sono memorizzati in settori che contengono:

Preambolo (16 byte) – Dati (2048 byte) – ECC (288 byte)

La velocità di lettura 1x è di circa 75 settori/s che corrispondono a

circa 150 Kbyte/s. Velocità massima di lettura: 52x.

Un CD contiene fino a 800MB di dati (80 minuti di musica).

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Memoria secondaria

Le memorie flash sono dispositivi a stato solido (non hanno parti in

movimento) non volatili (mantengono l’informazione anche se non

sono alimentate) che stanno prendendo il posto dei dischi.

• Velocità di lettura ~ 20 MB/s

di scrittura ~ 10 MB/s

• Latenza

~ 25 μs per iniziare a leggere,

~ 100 μs per leggere 2KB

~ 200 μs per scrivere 2KB

In futuro sostituiranno i dischi rigidi.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Sottosistema di I/O

Il sottosistema di I/O è la parte attraverso la quale si esplica la

comunicazione tra il calcolatore e il mondo esterno.

Ne fanno parte:

- dispositivi per la comunicazione uomo-macchina

(video, stampanti, mouse, ecc.)

- dispositivi di memoria secondaria

(unità a dischi, a nastri magnetici, ecc.)

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Sottosistema di I/O

Ogni dispositivo di I/O è collegato al bus di sistema attraverso una

interfaccia (o controllore), che realizza l’adattamento logico e fisico tra

le periferiche e il calcolatore.

Dal punto di vista logico, l’interfaccia deve:

• fornire porte di ingresso per i dati che devono essere inviati alla CPU,

e porte di uscita per i dati che devono essere trasferiti alla periferica (in

entrambi i casi è coinvolto il data bus);

• essere in grado di decodificare istruzioni e indirizzi delle porte da

utilizzare (le istruzioni viaggiano sul control bus, gli indirizzi sull’address

bus);

• fornire eventuali registri o buffer di appoggio per i comandi alla

periferica;

• tenere traccia dello stato della periferica e delle eventuali condizioni

di malfunzionamento o di errore, consentendone la lettura (segnali di

stato – es. BUSY e READY).

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Sottosistema di I/O

Il processore può comunicare con uno o più dispositivi esterni

secondo schemi temporali imprevedibili che dipendono dalle

richieste di I/O del programma.

I periferici sono normalmente più lenti a paragone della velocità di

esecuzione delle istruzioni di una CPU. Inoltre essi procedono in

modo autonomo e quindi si rende necessario introdurre qualche

meccanismo di sincronizzazione.

Le tecniche fondamentali sono:

- gestione a controllo di programma

- gestione sotto controllo di interruzione

- gestione tramite accesso diretto alla memoria (DMA)

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Gestione a controllo di programma

Si realizzano più sottoprogrammi di gestione per ogni periferica,

richiamabili dal programma principale.

Il grosso limite della gestione a controllo di programma: si va alla velocità

della periferica (che in genere è molto più lenta della CPU).

La maggior parte del tempo di CPU è sprecato nell’osservare lo stato della

periferica in attesa che sia pronta per un nuovo trasferimento.

Es.

la CPU esegue 100 M istr./sec

la stampante stampa 100 car/sec, cioè 1 carattere ogni 10 msec

tra carattere e carattere la CPU avrebbe tempo per eseguire 106 istr.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Gestione sotto controllo di interruzione

Ricordiamo cosa sono le interruzioni:

• eventi infrequenti ed eccezionali

• generati internamente o esternamente

• causano il trasferimento del controllo dal programma corrente a

un programma specifico di servizio dell'evento

In questo contesto, ci interessano le interruzioni esterne (external

interupt o device interrupt): in genere usate per gestire le

operazioni di I/O, si verificano in modo asincrono rispetto

all’esecuzione del programma.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Gestione sotto controllo di interruzione

La CPU non deve verificare con continuità lo stato dei dispositivi di

I/O. Devono essere questi ultimi a richiamare l'attenzione della

CPU.

Accesso diretto e rapido alla CPU per:

• richiesta inizio operazione.

• segnalazione di fine operazione.

E’ necessario assegnare urgenze

o priorità diverse alle varie

richieste di intervento se

contemporanee.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Accesso diretto alla memoria (DMA)

Se la periferica è molto veloce, è possibile che la frequenza delle

interruzioni sia così alta da non lasciare, tra interruzione e

interruzione, il tempo necessario all’intera esecuzione della routine

di servizio.

E’ il caso delle unità a disco, la cui velocità di trasferimento può

superare il milione di caratteri per secondo (stesso ordine di

grandezza della velocità di esecuzione delle istruzioni in una CPU

di prestazioni medie).

Tecnica più efficiente: un dispositivo gestisce il trasferimento

diretto dei dati tra periferiche e memoria, senza coinvolgere la

CPU (a cui ruba cicli di bus – cycle stealing). Tale dispositivo

prende il nome di Direct Memory Access Controller (DMAC).

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Strutture di interconnessione

Le strutture di interconnessione collegano i moduli che devono

scambiarsi informazioni.

In un sistema di calcolo le prestazioni, l’affidabilità e il costo delle

interconnessioni hanno un ruolo fondamentale.

Tipo: la connessione può essere di tipo serie (una sola

connessione fisica) o parallelo (più connessioni fisiche).

Prestazioni: si misurano in (M,K)Bytes o (M,K)bit al secondo

trasferiti.

Affidabiltà: dipende principalmente dal connettore.

Costo: legato al tipo di connessione e alla standardizzazione.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Bus di sistema

Internamente ad un sistema digitale la principale struttura di

interconnessione è il bus.

Il bus è un insieme di conduttori che trasferiscono le informazioni da

un elemento sorgente a un elemento destinazione.

• bus dedicato: collega in modo esclusivo due moduli

• bus condiviso: collega tra loro più moduli (collegamenti fra

elementi diversi avvengono in tempi diversi - time multiplexing)

Il bus di sistema,

sotto-bus:

• bus

• bus

• bus

anche se condiviso, in genere si compone di tre

dei controlli

degli indirizzi

dei dati

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Bus di sistema

Usando bus dedicati, per collegare N moduli ne servono N(N-1).

Questa soluzione consente di effettuare contemporaneamente più

operazioni di trasferimento dati.

L'uso di una struttura di interconnessione condivisa e

standardizzata consente di ridurre i costi e di ottenere una

struttura modulare scalabile, a scapito delle prestazioni. Questa

soluzione è comunque la più utilizzata nei moderni sistemi di

elaborazione.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Bus di sistema

ISA (Industrial Standard Architecture)

Ci sono due versioni del bus ISA: quella a 8 bit con una frequenza di clock di 4.77

MHz e quella a 16 bit, con frequenza pari a 8.3 MHz.

Il throughput varia dai 4 ai 5 MB/s.

EISA (Extended Industry Standard Architecture)

Prima evoluzione di questo standard usata sui computer IBM dal 1988. EISA aumentò

il Bus ISA da 16 a 32 Bit e permise a più di una CPU di usare questo Bus in

contemporanea. Venne usata principalmente come interfaccia per schede SCSI.

Questo slot fu abbandonato con l'arrivo del VESA e del successivo PCI.

VESA Local Bus

Successore dell'EISA, fu usato prevalentemente nei computer basati sul processore

Intel 80486 e fu studiato per eliminare il problema della bassa larghezza di banda

dello slot ISA. Lavorava sul Bus ISA ma, a differenza di quest'ultimo, aveva un

accesso diretto alla memoria di sistema che lo rendeva molto più veloce. Per

controparte aveva però alcune importanti limitazioni (compatibilità, limite al numero di

slot, corruzione dei dati).

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Bus di sistema

PCI (Peripheral Component Interconnect)

Sviluppato dalla Intel nel 1992 (in sostituzione del bus ISA). Diverse versioni: PCI,

PCI 2.0, PCI 2.1, PCI 2.2, PCI 3.0, PCI-X. Linee dati-indirizzi (sovrapposte)

(multiplexed). Clock a 33 – 66 – 133 – 266 MHz. Alimentazione 5 – 3,3 Volt. Il

trasferimento che avviene attraverso un bus PCI è un "burst", composto da una fase

di indirizzamento e da una o più fasi di dato. Bassa latenza ed elevato throughput.

PCI Express (PCIe)

Il PCI Express è il successore (seriale) del bus di espansione PCI (parallelo) e sarà

destinato a sostituire il bus AGP fino ad ora in uso per le schede grafiche.

L'architettura è completamente differente dal bus PCI classico.

La sua caratteristica seriale aiuta a semplificare il layout delle schede madri ed è

costituito da una serie di canali. Tali canali possono essere aggregati secondo le

esigenze rendendo di fatto il sistema molto flessibile. La banda a disposizione di

ciascun canale (FULL DUPLEX) è dedicata e quindi non condivisa con gli altri.

Un canale PCIe (detto x1) ha una banda disponibile di 266 MByte/sec. Pertanto, nelle

moderne schede video che utilizzano 16 canali PCIe la banda a disposizione è di

circa 4 GByte/sec (il doppio del bus AGP 8x).

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Bus di sistema

ATA (Advanced Technology Attachment)

Consiste in un'interfaccia standard per la connessione di dispositivi di

memorizzazione quali hard disk e unità CD-ROM all'interno dei personal computer.

Sono molti i termini utilizzati per designare tale standard, comprese abbreviazioni e

acronimi quali IDE, EIDE, ATAPI, UDMA ed il più recente PATA (Parallel-ATA) per

differenziarsi dal SATA (Serial-ATA) che è altra cosa. Gli standard ATA permettono

collegamenti con lunghezze di cavo comprese tra 45 e 90 cm, quindi l'utilizzo

prevalente per tale tecnologia è per le memorie di massa all'interno dei personal

computer.

I cavi Parallel ATA permettono il trasferimento di dati con 16 o 32 bit per volta.

UDMA0 16.7 MB/s

UDMA1 25 MB/s

UDMA2 33.3 MB/s

UDMA3 44.4 MB/s

UDMA4 66.7 MB/s

UDMA5 100 MB/s

UDMA6 133 MB/s

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Bus di sistema

SCSI (Small Computer System Interface)

L'interfaccia SCSI viene per lo più usata per la comunicazione con unità hard disk e

unità nastro di memorizzazione di massa, ma anche per connettere una vasta gamma

di dispositivi, come scanner d'immagini, lettori e scrittori di CD (CD-R e CD-RW),

lettori DVD. In effetti lo standard SCSI è stato ideato per favorire l'intercambiabiltà e la

compatibilità dei dispositivi (tutti, almeno in teoria). Esistono anche stampanti SCSI.

In passato l'interfaccia SCSI era molto diffusa in ogni tipologia di computer, mentre

attualmente trova un vasto impiego solamente in workstation, server e periferiche di

fascia alta (cioè con elevate prestazioni). I computer desktop e portatili sono invece di

solito equipaggiati con l'interfaccia ATA/IDE (acronimi rispettivamente di Advanced

Technology Attachment e Integrated Drive Electronics) per gli hard disk e con

l'interfaccia USB (Universal Serial Bus) per altre periferiche di uso comune.

Architettura dei calcolatori elettronici

Prof. M. Amoretti

UNIVERSITA’ DEGLI STUDI DI PARMA

Corso di Laurea in Ingegneria Gestionale

Fondamenti di Informatica

Bus di sistema

USB (Universal Serial Bus)

Standard di comunicazione seriale per il collegamento di periferiche (lente).

Consiste in un singolo gestore e molte periferiche collegate da una struttura simile ad

un albero attraverso dei dispositivi chiamati hub (concentratori). Supporta fino ad un

massimo di 127 periferiche per gestore, nel computo vanno inclusi anche gli hub e il

gestore stesso quindi in realtà il numero totale di dispositivi collegabili è sensibilmente

inferiore.

Le porte USB sono dotate del supporto del Plug and Play e supportano i dispositivi

hot swap quindi se il sistema operativo lo consente supportano la rimozione a caldo e

il reinserimento delle periferiche senza dover riavviare il computer.

All'interno del computer, l'USB non ha rimpiazzato lo standard ATA o SCSI per via

della sua lentezza. Il nuovo standard serial ATA per esempio consente trasferimenti

dell'ordine di 150 Mbyte per secondo, una velocità molto più elevata dello standard

USB, che nella versione 2.0 raggiunge un massimo di 60 Mbyte per secondo (480

Mbits/s). L'USB viene molto usato negli hard disk esterni dove si preferisce

privilegiare la praticità di poter collegare e scollegare a caldo il componente rispetto

alla velocità di una connessione tipo ATA.

Architettura dei calcolatori elettronici

Prof. M. Amoretti