Storia e tecnologia del Silicio

L’era dell’elettronica

Corso di formazione di Scienza dei Materiali

Montelibretti (Roma), Marzo 2003

Breve storia del Silicio

•

Il nome silicio deriva dal latino silex, selce

•

Il silicio è il secondo elemento più diffuso, dopo l’ossigeno, sulla crosta

terrestre (25%)

•

Il silicio fu isolato per la prima volta nel 1824 dal chimico svedese

Berzelius, che aveva proseguito il lavoro del grande chimico francese

Lavoisier il quale, avendo studiato il quarzo, affermò che questo era

composto da un elemento molto comune.

•

Il silicio non ha trovato alcun utilizzo fino alla fine del secolo scorso

quando venne scoperto che, se unito al ferro, sviluppava proprietà

magnetiche. Utilizzo prevalente per elettromagneti e trasformatori

•

Inizio della produzione industriale agli inizi del secolo in una forma

ragionevolmente pura (circa 98%)

IIIA

5

IVA

6

B

13

31

49

Al

Ga

In

14

32

50

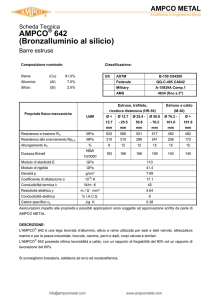

Proprietà chimiche

VA

7

N

C

Si

Ge

Sn

15

33

51

P

As

Sb

•

Semiconduttori classici

•

Semiconduttori compositi III-V

•

Droganti di tipo p per il Silicio

•

Droganti di tipo n per il Silicio

Proprietà chimiche

Due reticoli

cubici a facce

centrate

compenetrati e

traslati

•

Struttura cubica a facce centrate FCC (diamante)

•

•

Massa atomica 28.0855

•

•

•

Numero atomico 14

Densità 2.33 g/cm3

Temperatura di fusione 1414 °C

Gap tra Banda di conduzione e di valenza: 1.12 eV (Tamb)

Proprietà

semiconduttive

Conduzione elettrica nei materiali

Energia

Isolante

Banda di conduzione, EC

Banda proibita, EG

Banda di valenza, EV

•

Semiconduttore

Banda di conduzione, EC

Banda proibita, EG

Banda di valenza, EV

Metallo

Banda di conduzione, EC

Banda di valenza, EV

Isolanti

•

•

Banda di conduzione e di valenza separate da una banda proibita troppo elevata

improbabile la conduzione elettrica

Semiconduttori

•

Banda di conduzione e di valenza separate da un’energia di gap (stati energeticamente

non permessi)

•

La banda proibita è piccola e può essere superata tramite l’assistenza della temperatura

•

Conducibilità elettrica crescente con la temperatura

•

Metalli

•

Banda di conduzione e di valenza sovrapposte

nube di elettroni liberi

•

Conducibilità elettrica decrescente con la temperatura (scattering fra elettroni)

Silicio intrinseco (puro)

Impurità droganti

•

Il silicio (4 elettroni di valenza) presenta una struttura

tetraedrica in cui ogni atomo è legato ad altri 4 atomi

Gli elettroni presenti sono solo quelli di legame, non liberi di

poter condurre corrente elettrica

Silicio estrinseco n

•

L’introduzione di un atomo con valenza superiore a

quella del silicio (5 elettroni) causa un aumento degli

elettroni liberi per la conduzione

Silicio estrinseco di tipo n (conduzione di carica negativa)

Silicio estrinseco p

•

L’introduzione di un atomo con valenza inferiore (3

elettroni) a quella del silicio causa un aumento delle

mancanze di elettroni di legame (lacune)

Silicio estrinseco di tipo p (conduzione di carica positiva)

Silicio estrinseco n

Perturbazione

Impurità droganti

Silicio estrinseco p

Perturbazione

L’introduzione di questo tipo di impurità (drogaggio) provoca

un aumento della conducibilità del semiconduttore

Le basi dell’elettronica si fondano sulla possibilità di introdurre in modo

controllato questi due tipi di impurità in modo da modificare la conducibilità

elettrica ed il tipo di conduzione del materiale semiconduttore

•

•

Limite superiore di concentrazione di

drogante: limite di solubilità del

drogante nel silicio

Limite inferiore: impossibilità

tecnologica di disporre di un

materiale del tutto privo di impurità

(<1 parte per miliardo)

Sono impurità droganti

elettricamente attive solo

quelle impurità sostituzionali

ad atomi di silicio e non in

posizione interstiziale

Sviluppo dell’elettronica moderna

Base Emettitore

n

p

•

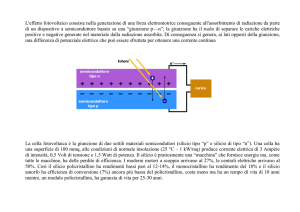

Rivoluzione del XX secolo: scoperta del

transistor nel 1948 ad opera di Schockley,

Bardeen e Brattain

•

Da TRANSfer reSISTOR, dispositivo a

trasferimento di resistenza

•

Dispositivo a 3 terminali (base, emettitore,

collettore) formato dalla combinazione n-p-n

o p-n-p di materiale semiconduttore

•

L’effetto transistor consiste nell’iniezione

modulata di portatori dall’emettitore al

collettore (elettroni nel transistor npn e

lacune nel pnp)

•

Il transistor pnp ha prestazioni inferiori

rispetto a quello npn a causa della differente

iniezione di carica

n

Collettore

Emettitore

Collettore

Substrato

di germanio

Base

Importanza dell’elettronica dello stato solido

•

Funzioni fondamentali del transistor:

•

Amplificazione di corrente

•

Inverter logico

Elettronica digitale

Amplificazione

Transistor

1

0

Transistor

Inverter logico

0

1

•

Tempo di vita, dimensioni,

integrazione, frequenza di

lavoro i vantaggi nei confronti

delle valvole

Stato dell’arte dei Circuiti Integrati: microprocessori

•

Nel 1959 nasce il circuito integrato dall’idea di realizzare tutti i componenti di un circuito

elettronico su uno stesso substrato composto da un unico materiale semiconduttore

Intel 8086 (1979)

•

10 MHz

•

Transistors: 29000

•

Tecnologia: 3 m

Intel 4004 (1971)

•

108 kHz

•

Transistors: 2300

•

Tecnologia: 10 m

Intel 80286 (1982)

•

12 MHz

•

Transistors: 134000

•

Tecnologia: 1.5 m

Intel 80386 (1985)

•

33 MHz

•

Transistors: 275000

•

Tecnologia: 1.0 m

Microprocessori

Intel 80486 (1989)

•

50 MHz

•

Transistors: 1.2 milioni

•

Tecnologia: 1.0 m

Intel Pentium (1993)

•

200 MHz

•

Transistors: 3.1 milioni

•

Tecnologia: 0.35 m

Intel Pentium Pro (1995)

•

266 MHz

•

Transistors: 5.5 milioni

•

Tecnologia: 0.35 m

Oggi

Intel Pentium IV (2002)

•3060 MHz

•55 milioni transistors

•Tecnologia: 0.13 m

AMD Athlon XP (2002)

•2167 MHz

•54.3 milioni transistors

•Tecnologia: 0.13 m

9

10

8

10

Pentium IV

1000

7

10

100

Pentium

80486

80386

6

10

10

5

10

1

80286

8086

4

10

0,1

Frequenza di lavoro (MHz)

Transistors per chip

Integrazione elettronica:

leggi di Moore (1965)

4

10

•

Il miglioramento tecnologico

elettronico è dovuto ad un aumento

esponenziale dell’integrazione

•

Il numero di transistor in un chip e

la sua frequenza massima di

funzionamento raddoppiano ogni

circa 2 anni (attualmente 55 milioni

e 3.06 GHz)

•

La dimensione della regione attiva

di un transistor in un circuito

integrato diminuisce del 30% ogni

3 anni

•

LSI: Large Scale Integration

•

VLSI: Very Large Scale Integration

•

ULSI: Ultra Large Scale Integration

4004

1000

1970

1975

1980

1985

1990

1995

2000

2005

0,01

2010

Dimensione transistor (m)

10

LSI

VLSI

ULSI

1

0,1

1970 1975 1980 1985 1990 1995 2000 2005 2010

Vantaggi della tecnologia del silicio

La tecnologia del silicio è divenuta la tecnologia dominante per l’elettronica a causa di:

•

Disponibilità praticamente illimitata del materiale

•

Relativa facilità di realizzazione di cristalli con bassa densità di difetti

•

Buone proprietà ottiche ed elettriche che lo rendono adatto alla realizzazione di un

amplissimo set di dispositivi

•

Un ossido SiO2 (banda proibita pari a 8 eV) dalle eccellenti proprietà:

•

Ottimo isolante elettrico

•

Ottimo passivante nei confronti del silicio

•

Barriera contro le impurità

•

Processi di realizzazione ad elevata controllabilità

Tecnologia di purificazione

SiO2 (quarzite)

Si grado elettronico

monocristallino

Tornitura

e taglio

Processo di purificazione

(Siemens 1951)

Si grado elettronico

policristallino

Czochralski

Fetta di Si

monocristallino

Macinatura

Monocristallino

Policristallino

Lappatura e

lucidatura

Fetta di silicio

(wafer)

Tecnologia di purificazione

Fornace

Quarzite,

SiO2

Silicio di grado metallurgico

MGS (98%)

HCl

Triclorosilano, SiHCl3

Distillazione

frazionata

Silicio policristallino di grado

elettronico EGS (99.99999%)

H2 + SiHCl3

Processo Czochralski

•

Introdotto dalla Texas Instruments nel 1952, permette la

realizzazione di un monocristallo di silicio (1 impurità su 1

miliardo di atomi) da silicio policristallino di grado elettronico

Processo Czochralski

Fusione del policristallo nel crogiolo realizzato in

grafite rivestita in quarzo SiO2

Aggiunta di drogante: Boro (p-Si); Fosforo o

Arsenico (n-Si)

Accrescimento controllato del seme preorientato

Barra di monocristallo di 6-12 pollici (15-30 cm) di

diametro e circa 100cm di lunghezza

•

Temperatura di fusione Si

1414 °C

•

Controllo del gradiente di

temperatura lungo il fuso

•

Processo in atmosfera di

gas inerte

•

Crogiolo realizzato con

elementi elettricamente

inattivi nel silicio

•

Elevato controllo della

rotazione e della trazione

del lingotto

Seme cristallino

Monocristallo

Crogiolo in quarzo

Camera

Schermo termico

Riscaldatore

Crogiolo in grafite

Supporto

Basamento

Elettrodo

Reattore in dettaglio

Parametri fondamentali di processo

•

•

Velocità di rotazione

•

Velocità di trazione

Controllo della temperatura

Processo Czochralski

Processi meccanici

Controllo dell’orientazione

cristallografica tramite

diffrazione da raggi X

Decappaggio delle estremità

100

111

Rettificazione del lingotto

Lucidatura per via

chimica (soda

caustica) di una

faccia

Lappatura meccanica

di una faccia

Taglio del lingotto tramite seghe

circolari o a filo in dischi (wafers)

dello spessore di 200-450 m

Notazione dell’orientazione

Direzione (100)

Piano (100)

Tipo n {111}

Tipo p {111}

45°

180°

Tipo n {100}

90°

Tipo p {100}

Direzione (111)

Piano (111)

La tecnologia elettronica odierna si fonda su una

metodologia di tipo planare

Realizzazione dei

dispositivi su un’unica faccia del wafer

wafer

Progetto CAD

Maschere di

produzione

Tecnologia planare

•

•

Fotolitografia

Esposizione + rimozione selettiva

•

Ossidazione termica

•

Crescita epitassiale

•

Impiantazione ionica

•

Diffusione termica

•

Metallizzazione

Testing su wafer

Testing su chip

Packaging

Fotolitografia

•

Tecnica per la realizzazione di microstrutture sul substrato semiconduttore

attraverso maschere

1.

Deposizione resist chimicamente fotosensibile (PMMA)

2.

Esposizione del fotoresist attraverso la maschera a

luce UV (153 nm)

3.

Sviluppo del resist esposto

4.

Attacco chimico selettivo

•

Con l’applicazione in sequenza con maschere tra loro allineate si realizza il Circuito

Integrato

•

La risoluzione dell’ottica nel processo di fotolitografia è il processo limitante della

dimensione minima dei dispositivi (attualmente la tecnologia si attesta su 0.13 m)

Fotolitografia: esposizione UV

•

Tre tecniche di esposizione:

•

Esposizione per contatto (danneggiamento maschere)

•

Esposizione per prossimità (ingrandimento 1:1 del circuito)

•

Esposizione attraverso stepper (ottica di esposizione)

Radiazione UV

Radiazione UV

Maschera N:1

Quarzo

Ossido di silicio

Ottica

Cromo

Fotoresist

Immagine

Wafer con resist

Wafer di silicio

Esposizione per prossimità

Esposizione attraverso stepper

Fotolitografia: sviluppo

•

Due tipi di fotoresist

•

Resist positivo: solubile il volume illuminato dalla radiazione

•

Resist negativo: solubile il volume non illuminato dalla radiazione

Resist positivo

Fotoresist

Ossido di silicio

Sviluppo

Wafer di silicio

Attacco chimico

Rimozione fotoresist (solventi)

Resist negativo

Attacco chimico

•

Attacco chimico per via umida (reagenti chimici)

•

Attacco chimico per via secca (anisotropo, Reactive Ion Etching)

Resist

Ossido di silicio

Silicio

Via umida, isotropo

• L’attacco laterale è circa il

75% di quello in profondità

• Solvente per SiO2: HF

• Solvente per Si: HNO3 + HF (il

primo ossida, il secondo

rimuove l’ossido)

Via secca, anisotropo

• Plasma di ossigeno,

idrogeno e gas Freon (CF4)

produce un continuo

bombardamento della

zona processata

Crescita epitassiale

•

Dal greco epi (sopra) + taxis (struttura ordinata)

•

Crescita di un semiconduttore monocristallino (intrinseco o drogato) su di un

substrato semiconduttore

Omoepitassia

Eteroepitassia

(stesso semiconduttore)

(semiconduttore differente)

Wafer di silicio

N2

Bobine a radiofrequenza

H2

•

Epitassia da fase vapore (VPE)

•

Epitassia da fase liquida (LPE)

Drogante+H2 •

HCl SiCl4+H2

Epitassia da fasci molecolari (MBE)

Ossidazione

Miscelatore

F

F

F

H2O

N2

O2

•

Trattamento ad alta temperatura (900-1200 °C)

per la crescita di sottili strati di ossido di silicio su

silicio

•

Il silicio, a contatto con l’aria, si ossida quasi

istantaneamente per uno spessore pari a 30 A°

(ossido nativo)

•

Due tecniche:

O2

•

Ossidazione a secco (dry), minore velocità

di crescita ma maggiore qualità dell’ossido

prodotto (strati isolanti)

Si + O2 SiO2

•

Ossidazione da vapore acqueo (wet),

maggiore velocità, minore qualità

dell’ossido (strati passivanti)

Si + 2H2O SiO2 + 2H2

Tecniche di drogaggio: diffusione

Sorgenti gassose:

PH3, AsH3, B2H6

F

F

F

H2O + sorgenti liquide:

POCl3, BBr3

N2

O2

O2

•

Atomi droganti vengono a contatto della superficie del wafer attraverso

un processo di deposizione chimica ad alta temperatura (900-1000 °C)

•

Atomi diffondono nel substrato con un coefficiente di diffusività variabile

da specie a specie e dipendente in modo crescente dalla temperatura e

dalle dimensioni dell’atomo drogante

Profilo di drogaggio in profondità poco flessibile e controllabile

Trattamento ad alta temperatura

Tecniche di drogaggio: impiantazione ionica

Deflessione orizzontale

e verticale

Spettrometro di massa

Wafer di Si

Fascio di ioni

Misura della corrente

(ioni impiantati/sec)

Acceleratore (5-200 keV)

• Fascio di atomi droganti impiantati ad alta energia nel wafer di silicio

Sorgente di ioni • Controllo accurato della dose impiantata

• Parametri fondamentali:

• Energia di accelerazione (dipendenza crescente della profondità)

• Massa dello ione incidente (dipendenza decrescente della profondità)

• Massa dell’atomo bersaglio

Vuoto

Silicio

ione

Energia (eV)

Penetrazione media

Varianza

laterale

Varianza di profondità

Impiantazione ionica: channeling

•

•

7° di

disallineamento

Se il bersaglio non è disallineato, gli

ioni potrebbero seguire percorsi

preferenziali e non interagire col

reticolo cristallino: channeling

Il fenomeno del channeling può essere

evitato in due modi:

•

attraverso un disallineamento

del bersaglio (7° di angolo di tilt

rispetto alla direzione 110)

•

attraverso un’amorfizzazione

preventiva della superficie del

bersaglio con un processo di

impiantazione effettuato con

atomi di grande massa (Argon)

Annealing

L’annealing (ricottura di breve durata tramite laser o

forno) del materiale è il processo successivo

all’impiantazione ionica:

•

il cristallo bersaglio subisce dei danni provocati

dalla cessione di energia dallo ione al reticolo

•

probabilità di avere ioni droganti situati in

posizione interstiziale e perciò non attivi

L’annealing si configura così come il trattamento

termico atto alla riparazione del danno reticolare ed

all’attivazione degli ioni droganti

• Processo necessario per la connessione elettrica di

tutti i dispositivi presenti nel circuito integrato

Metallizzazione

• Metallizzazione si realizza tramite le tecniche di

deposizione:

• Evaporazione termica

processo termico basato sull’evaporazione

del metallo se portato alla temperatura di fusione

• Sputtering

tecnica a bassa temperatura basata sul bombardamento

di un bersaglio metallico al fine di estrarre da questo gruppi di atomi (clusters)

che, successivamente, si depositano sul substrato

•

Deposizione di materiali amorfi (non

interessa la struttura cristallina, ma la

continuità elettrica)

•

Per anni utilizzato l’alluminio,

recentemente il rame

elevata conducibilità termica

Realizzazione di un transistor

Substrato p

p

p

n

Crescita epitassiale n

Substrato p

Silicio n

Drogaggio: impiantazione n+ per

emettitore e collettore

Substrato p

p

Drogaggio: diffusione p per

pozzetti di isolamento

p

n+

n

Silicio n

Substrato p

Drogaggio: impiantazione p

per base del transistor

p

Substrato p

Resist

SiO2

p

p

Metallizzazione

p

Metallo

p

E

B

p

n

Substrato p

C

p

Substrato a fine processo

Collaudo automatico

Testing e Packaging

Identificazione

chip difettosi

Chiusura del package

Metallizzazioni esterne

(bonding) e packaging

Taglio del substrato nei

singoli chip (laser)

Differenza di potenziale

Banda di conduzione

Elettrone

Banda

proibita

Silicio policristallino

Applicazioni: celle fotovoltaiche

•

Monocristallino: rendimento 18-23%, costo

100 €/kg

•

Policristallino: rendimento 12-14%, vita

media 25-30 anni, costo 10 €/kg

•

Amorfo: rendimento 7%, vita media 10

anni, costo minimo

Lacuna

Banda di valenza

• Conversione da energia

elettromagnetica ad energia

elettrica

• Contribuisce alla conduzione solo

la radiazione con energia

superiore alla banda proibita

Strato antiriflesso

Silicio policristallino

Giappone, USA, Germania non solo incentivano

l’installazione degli impianti, ma comprano l’energia

ad un prezzo superiore a quello di mercato