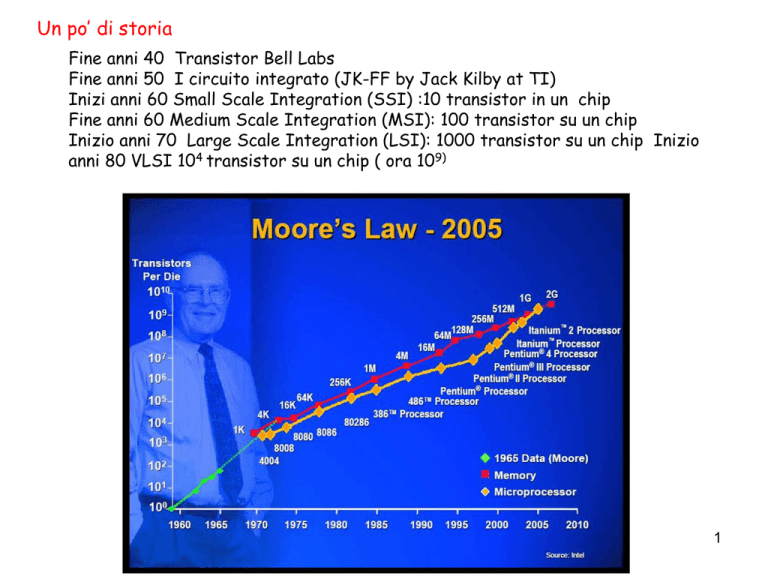

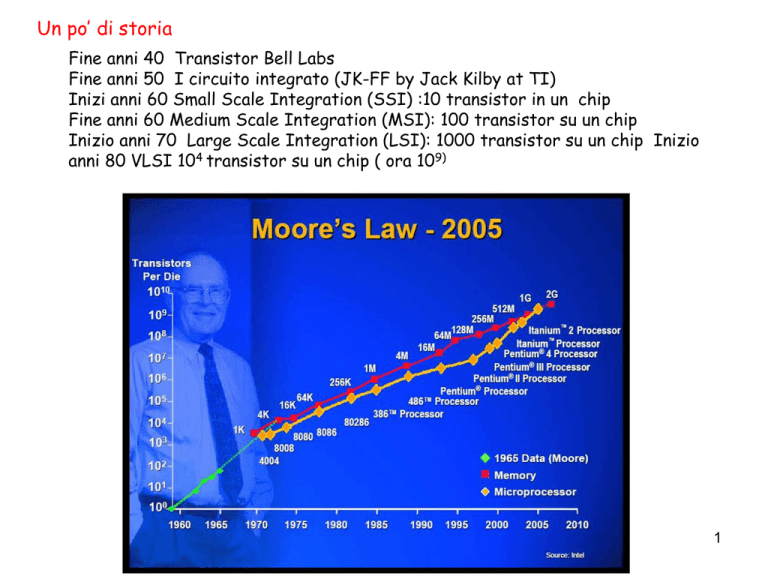

Un po’ di storia

Fine anni 40 Transistor Bell Labs

Fine anni 50 I circuito integrato (JK-FF by Jack Kilby at TI)

Inizi anni 60 Small Scale Integration (SSI) :10 transistor in un chip

Fine anni 60 Medium Scale Integration (MSI): 100 transistor su un chip

Inizio anni 70 Large Scale Integration (LSI): 1000 transistor su un chip Inizio

anni 80 VLSI 104 transistor su un chip ( ora 109)

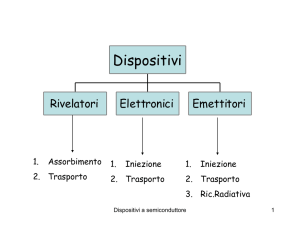

Dispositivi a semiconduttore

1

VLSI :low power consumption& dissipation

Ok sistemi con controllo in tensione

JFET

FET: transistor ad effetto di campo

MOSFET

Rispetto ai transistor bipolari:

-dispositivo unipolare

-alta impedenza ingresso

-coeff.temperatura negativo ( non tutti), cioè al crescere di T la corrente

diminuisce. Ne segue maggiore stabilità e uniformità termica

-manca storage minoritari ( come pol.diretta transistor bipolari) e quindi

tempi commutazione rapidi

Dispositivi a semiconduttore

2

JFET

Canale conduttivo con 2 contatti ohmici: S e D

Il Gate G forma una giunzione con il canale

JFET: voltage-controlled resistor

L: lunghezza canale

VG 0 VD 0

Source a massa: la corrente elettroni verso il drain

Dispositivi a semiconduttore

3

JFET a canale n

Dispositivi a semiconduttore

4

Caratteristiche

saturazione

lineare

Dispositivi a semiconduttore

5

JFET

W(x)

W(x)

Dispositivi a semiconduttore

6

Dispositivi a semiconduttore

7

JFET: caratteristiche statiche

VD , P

Dispositivi a semiconduttore

8

dx

JFET

W(X)

dV (x) ID dR(x)

1 dx

dx

dR(x)

S(x) b2(a W (x))

W(X)

x

2

W (x)

(Vbi VG V (x))

qN D

Dispositivi a semiconduttore

9

W (x)

2

(Vbi VG V (x))

qN D

W (0)

2

(Vbi VG ) : Dimensione regione svuotamento al source

qN D

W (L)

2

(Vbi VG VD ) : Dimensione regione svuotamento al drain

qN D

Pinch - off quando W = a

Potenziale di pinch-off

Nella regione lineare:

qN D a

2

2

VD VD,P VG Vbi

Dispositivi a semiconduttore

10

JFET

Tensione di pinch-off

qN D a 2

2

Vbi VG V (x)

dV (x)b2a1

ID dx

VD

L

Vbi VG V (x)

ID dx

dV (x)b2a1

0

0

b2a

2 1

3/2

3/2

ID

VD

Vbi VG VD Vbi VG

L

3

ID è continua nel canale e quindi

Dispositivi a semiconduttore

indipendente da x

11

b2a

2 1

3/2

3/2

ID

VD

Vbi VG VD Vbi VG

L

3

b2a

gmax

: conduttanza max canale per W = 0

L

La corrente satura ad un valore IDsat che si ottiene al pinch-off:

W a

VD,P : tensione di pinch - off

Vbi VG VD,P

qa 2 N D

2

VD,P VG VT

dove :

VT Vbi

2 V V

bi

G

ID,sat gmax Vbi VG 1

3

3

Dispositivi a semiconduttore

12

VD VD , P VG Vbi

2

qN D a

2

2 1

3/2

3/2

ID gmax VD

Vbi VG VD Vbi VG

3

Vbi VG VD gmax

ID

gD

gmax

1

(a W )

VD

a

V V V

V

V

ID

bi

G

D

bi

G

gm

gmax

VG

g : transconduttanza diretta g : transconduttanza di drain

m

D

Dispositivi a semiconduttore

13

JFET: caratteristiche statiche

VD , P

Dispositivi a semiconduttore

14

JFET

Onset della saturazione

VD VD,P VG Vb,i VG VT

V V V

ID

bi

G

D

gm

gmax

VG

gm,sat gmax

1

V

V

bi G

V

V

bi G g

D,lin

gD,lin è la transconduttanza di drain in regime lineare per V

Dispositivi a semiconduttore

D

0

15

JFET: confronto modello dati

Dispositivi a semiconduttore

16

Effetti legati a mobilità cariche:

-saturazione velocità drift comporta una riduzione della corrente nel canale

e la transconduttanza diminuisce: non si può considerare costante la mobilità

-overshoot velocità riduce il tempo di transito in FET a canale corto

Risposta in frequenza:

-tempo di transito tr=L/E ≈L2/VG e tr=L/vs

Per un gate di 1 µm tr≈ 10 ps

-effetti capacitivi

ft=gm/(2CGS)

Dispositivi a semiconduttore

17

Diodo MIS

Dispositivi a semiconduttore

18

Diodo MIS

=SiO2

=Si

Dispositivi a semiconduttore

Diodo MOS

19

Diodo MOS

9 eV

Dispositivi a semiconduttore

20

Diodo MOS

eV0

eS

Dispositivi a semiconduttore

21

Diodo p-MOS

V=0

Dispositivi a semiconduttore

22

Diodo p-MOS

V=0

V>0

Dispositivi a semiconduttore

23

Diodo p-MOS

V=0

V>0

V=-V0- S

Dispositivi a semiconduttore

24

Diodo p-MOS : reale

Svuotamento

V=0

Inversione

V>0

Bande piatte

V=-V0- S

Accumulazione

V<-V0-S

Dispositivi a semiconduttore

25

Diodo p-MOS

V=0

Svuotamento

V>0

Inversione

Non polarizzato

V=-V0- S

Accumulo

V<-V0-S

Dispositivi a semiconduttore

26

Diodo p-MOS

VT>V>0

Svuotamento

V>VT

Inversione

Non polarizzato

V=0

Accumulo

V<0

Dispositivi a semiconduttore

27

Diodo p-MOS Ideale

VT>V>0

Svuotamento

V>VT

Inversione

Non polarizzato

V=0

Accumulo

V<0

Dispositivi a semiconduttore

28

Diodo n-MOS Ideale

0>V>-VT

Svuotamento

V<-VT

Inversione

Non polarizzato

V=0

Accumulo

V>0

Dispositivi a semiconduttore

29

Diodo p-MOS Ideale

Dispositivi a semiconduttore

30

Dispositivi a semiconduttore

31

Dispositivi a semiconduttore

32

Varactor

Dispositivi a semiconduttore

33

MOS Varactor

1

CMOS

d

O

Dispositivi a semiconduttore

W (V )

S

1

1

CO C j

34

Elettrostatica MOS

Accumulo

Svuotamento

Inversione

Dispositivi a semiconduttore

35

MOSFET : dispositivo a 4 terminali

>99% IC sono MOSFET (RAM, flash memory, processori,etc)

Annunciata per il prossimo anno la realizzazione di chip con tecnologia 22 nm

( da Technology Review giugno 2010)

Dispositivi a semiconduttore

36

Regime di inversione

Dispositivi a semiconduttore

37

Diodo p-MOS

VT>V>0

Svuotamento

V>VT

Inversione

Non polarizzato

V=0

Accumulo

V<0

Dispositivi a semiconduttore

38

Nel regime di inversione formazione di un canale in cui il

numero di elettroni dipende dalla tensione di gate

Dispositivi a semiconduttore

39

I vari regimi (Source a massa

e substrato a massa)

a) Schema

b) Condizione di equilibrio VD=VG= VSB=0

c) Equilibrio con VD=0 ma bias VG

d) Non equilibrio VD e VG ≠0

Nella condizione d) il quasi- livello

di Fermi delle lacune rimane al

livello del bulk mentre quello degli

elettroni si abbassa verso il drain

Dispositivi a semiconduttore

40

Nel caso di non equilibrio la regione di svuotamento alla superficie è funzione di VD

Dispositivi a semiconduttore

41

Caratteristiche

Dispositivi a semiconduttore

42

Regione lineare: canale

con conduttanza che dipende da

VD

Al crescere di VD il canale si

stringe fino al pinch-off:

diminuisce l’inversione

ID è costante e la

strozzatura del canale si

sposta all’indietro.

Dispositivi a semiconduttore

43

MOSFET (n channel=pMOS)

Dispositivi a semiconduttore

44

MOSFET

Dispositivi a semiconduttore

45

MOSFET

Dispositivi a semiconduttore

46

MOSFET

Dispositivi a semiconduttore

47

Tensione di soglia

Dispositivi a semiconduttore

48

Tipi di MOSFET

Dispositivi a semiconduttore

49

Normally off

Normally on

CMOS

Dispositivi a semiconduttore

50

Invertitore

Dispositivi a semiconduttore

51