Insegnamenti di

Sistemi Elettronici Dedicati 1

(Corso di Laurea in Ingegneria Elettronica)

Sistemi Elettronici Digitali1

(Corso di Laurea Specialistica in Ingegneria delle Telecomunicaizoni)

Introduzione ai

Dispositivi FPGA

Edizione 2004

Rodolfo Zunino

FPGA (Field Programmable Gate Array)

I dispositivi FPGA sono circuiti integrati contenenti molte celle logiche identiche, che

possono essere viste come delle singole porte logiche. Ogni cella può indipendentemente prendere

possesso di una funzione specifica, definita da una tabella e può comunicare con le altre celle

tramite una fittissima trama di interconnessioni e di interruttori. Questa matrice di celle e di

connessioni forma la base per la costruzione di ogni circuito, anche di quelli più complessi, grazie

alla grande varietà di funzioni possibili e all'elevatissimo numero di connessioni.

Sono dispositivi programmabili direttamente dall’utente, costituiti da un array di componenti

logici, circondati da blocchi di I/O programmabili liberamente e collegabiti tra loro tramite

interconnessioni programmabili; costituiscono un’importante evoluzione nel mondo dei dispositivi

programmabili poichè hanno un’elevata potenza di calcolo e di connessione. Un aspetto molto

importante sono i collegamenti locali che attraversano il dispositivo e che sono condivisi da pochi

elementi logici, quindi la potenza utilizzata ed i ritardi che si generano sono contenuti. All’interno

di uno stesso dispositivo possono esserci differenti linee locali di lunghezza differente e questo

garantisce un’elevata flessibilità del sistema.

Field Programmable significa che la funzione dell'FPGA è definita dal programma dell'utente,

piuttosto che dalla disposizione, non modificabile, dei dispositivi che realizzano le funzioni logiche.

Questi dispositivi permettono di raggiungere livelli di integrazione molto spinti, mantenendo la

caratteristica di basso costo di produzione iniziale, tipico dei dispositivi programmabili.

2

I componenti FPGA si distinguono per il tipo di blocchi logici implementati all'interno del

chip e per il modo di programmarle; vengono usati in applicazioni che richiedono alte prestazioni,

dove sono necessari dei tempi di risposta brevi, in situazioni in cui sia necessario realizzare un data

path, nelle I/O intensive applications oppure nelle register intensive applications (ad esempio

possono essere utilizzate per realizzare un interfacciamento ad un bus PCI a 33MHz o a 66MHz,

oppure un controllore di una DRAM con ts=3ns e tco=6ns, o ancora per applicazioni collegate a reti

ETHERNET o reti ancora più prestanti come le reti ATM). Le MPGA (Mask Programmable Gate

Array) hanno le stesse funzionalità degli FPGA, ma sono programmabili dalla sola ditta costruttrice

attraverso le maschere tecnologiche e quindi non sono nè programmabili sul campo nè tantomeno

riprogrammabili; sono gate array in cui viene fatta una prima fase tecnologica a livello di ossido

sottile (TOX thin oxide), ma non vengono messe le metallizzazioni per realizzare le

interconnessioni. Queste ultime vengono aggiunte in un secondo tempo in seguito ad una richiesta

da parte dell'utente.

Le FPGA sono commercialmente anche conosciute come:

•

LCA (Logic Cell Array)

•

pASIC (programmable ASIC)

•

FLEX, APEX (Altera)

•

ACT (Actel)

•

ORCA (Lucent)

•

Virtex (Xilinx)

•

pASIC (QuickLogic)

Le FPGA sono particolarmente interessanti sotto alcuni punti di vista, poichè rappresentano:

•

il miglior compromesso tra flessibilità, prestazione e costo;

•

piattaforme per la realizzazione di sistemi completi, infatti possono essere sia definitivi sia

prototipi.

Sebbene abbiano prestazioni ridotte rispetto ad un ASIC (Application Specific Integrated

Circuit), hanno:

•

un costo e un tempo di produzione inferiori;

•

un costo per unità più basso per bassi volumi di produzione;

•

la particolarità di poter far riversare sullo stesso dispositivo le configurazioni che descrivono

applicazioni differenti; le descrizioni risiedono in ROM e, prima dell’uso, vengono caricate

in RAM oppure direttamente caricate in RAM durante l’esecuzione.

3

Un tradizionale approccio allo sviluppo di questi dispositivi prevede che la simulazione

comportamentale di un circuito venga svolta via software, purtroppo però la crescente complessità

dei dispositivi mette in evidenza due svantaggi di tale modus-operandi, infatti la verifica di porzioni

ridotte del dispositivo introduce problemi di verifica del funzionamento globale e riduce anche la

possibilità di rispettare le scadenze imposte dal time-to-market.

Le FPGA sono tipicamente inadatte per applicazioni puramente G.P. (General Purpose),

basati su microprocessori, o anche S.P. (Special Purpose), dominio degli ASIC, ma col tempo il

“gap” e la linea di confine presente tra FPGA, ASIC e µP si è assottigliata poichè si sono

ottimizzate alcune aree del sistema.

I. Tecnologie per programmare i dispositivi FPGA

Le interconnessioni tra le celle possono essere di due tipi:

•

Volatili: si mette una RAM in cui si scrive la configurazione;

•

Non Volatili: si mette o una EEPROM, o una FLASH, o si può cablare direttamente nel

FPGA le informazioni relative alle piste oppure si utilizza il metodo

dell’AntiFuse[O1] (PROM)

cioè si ha un circuito aperto fino al momento in

cui viene forzata la corrente.

Le tecnologie influenzano la scelta delle architetture per le interconnessioni e per il routing

che, a loro volta, influenzano l'architettura dei blocchi logici (se un certo tipo di tecnologia permette

di realizzare molte intercnnessioni la scelta del tipo di blocchi da utilizzare sarà orientata verso

blocchi piccoli e poco complessi). Per la realizzazione delle interconnessioni ci sono tre possibilità:

1.

Utilizzare delle "antifuse devices" che normalmente sono dei circuiti aperti, ma possono

diventare dei conduttori se viene fatta passare una corrente elevata tramite una opportuna

tensione. I dispositivi antifuse possono essere realizzati in due modi differenti:

a. dispositivo antifuse che utilizza silicio amorfo; Si crea una "via" conduttrice (R=5ohm)

nel silicio amorfo che normalmente è un isolante a causa degli ioni metallici che vi si

insinuano quando si applica per un tempo adeguato una tensione di 10-12V.

4

Questa tecnologia non è riprogrammabile, ma ha il vantaggio che permette di realizzare

dispositivi con matrici di interconnessioni ad alta densità, e questo consente di realizzare

blocchi logici semplici. Il limite alla densità raggiungibile con questa tecnologia è dato

dalla dimensione fisica minima che devono avere le linee di collegamento;

b. dispositivo antifuse che utilizza oxide-nitride-oxide

2. Programmare le interconnessioni tramite celle di SRAM: questa tecnologia mi permette di

riprogrammare sia le connessioni sia le funzionalità dei blocchi durante il funzionamento del

dispositivo, perchè la SRAM è omogenea con la normale attività del sistema.

La grande flessibilità consentita dall'utilizzo di SRAM si paga però in termini di area, perchè il

suo utilizzo comporta dimensioni superiori di almeno un ordine di grandezza rispetto ai

5

dispositivi antifuse; inoltre questo tipo di tecnologia presenta una resistenza di interconnessione

dell'ordine del KΩ.

Per realizzare interconnessioni programmabili attraverso delle SRAM si utilizzano

configurazioni di questo tipo:

Esistono altre configurazioni, più complesse, che permettono la creazione di collegamenti

estremamente flessibili come ad esempio:

Per ottenere il collegamento completo non sarebbe necessario programmare tutti i transistor, ma

in

questo

modo

non

ci

sarebbe

resistenza

minima

all'interconnessione.

Una RAM statica si può realizzare con 5 transistor in questo modo:

6

3. Interconnessioni basate sui transistor floating gate; si distinguono in EPROM (cancellabili con i

raggi ultravioletti) e EEPROM (cancellabili con la tensione, quindi hanno il pregio di essere

riprogrammabili direttamente sulla scheda). Esse sono riprogrammabili e non volatili, richiedono

un’area con dimensioni che stanno a metà strada tra le due tecnologie precedenti.

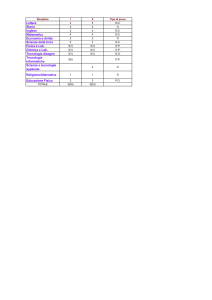

La seguente tabella riassume le caratteristiche delle tre tecniche considerate sopra:

Tecnologia

Volatilità Programmabilità

Area

R

(KΩ)

0.5-2

C

Extra

(pF)

steps

SRAM

Si

Si

Grande

10-20

0

Antifuse

No

No

Piccola

0.05-0.1 1.1-1.3

3

Antifuse ONO

No

No

Piccola

0.3-0.6

3

EPROM

No

Si

Media

2

10-20

3

EEPROM

No

2

10-20

>5

silicio amorfo

Si sul circuito

Il

doppio

5

dell’EPROM

Nota: per “extra steps” si intendono i passi aggiuntivi richiesti dalla tecnologia rispetto al processo

di produzione delle SRAM

7

Tecniche di programmazione dei dispositivi FPGA

Il linguaggio di programmazione utilizzato è il VHDL e di seguito viene riportato uno schema

semplificato di un tipico iter progettuale di dispositivo digitale basato su FPGA.

Le varie fasi di questo iter possono essere cosi’ sintetizzate:

Sintesi:

descrizione schematica del dispositivo, prende in ingresso una descrizione

comportamentale e dà in uscita una descrizione strutturale (rete logica);

Simulazione:

ricrea la rete, senza modificare nulla, ottimizza il tutto indipendentemente dalla

tecnologia che si utilizzerà in seguito;

Mapping:

conversione della lista dei componenti base in una lista di componenti logici.

Si ottimizza il circuito per ridurre o l’area da utilizzare o per aumentare le

prestazioni, quindi è un passo che dipende dalla tecnologia che si utilizza;

Simulazione

(fisico-elettrica del circuito, ad esempio con programmi di CAD quali SPICE);

8

Place & Route:

assegna le celle logiche ad una specifica locazione del FPGA e seleziona

segmenti di linee di connessione, li collega alle celle e configura la matrice degli

interruttori (se presente);

Simulazione/Emulazione: dipende dalla tecnologia e dal FPGA utilizzati.

Si inizia con la descrizione in HDL (può essere VHDL ma anche AHDL, Verilog o altro)

dell’FPGA; in commercio esistono diversi tool che aiutano a scrivere in HDL.

Un esempio di descrizione Vhdl è la seguente:

Successivamente si effettua la simulazione per verificare che le temporizzazioni siano

effettivamente quelle desiderate. Se ci sono ad esempio dei ritardi che possono provocare errori

allora si andrà a rivedere la descrizione in HDL.

9

Con la simulazione si visualizzeranno le uscite desiderate ed il loro andamento nel tempo, ad

esempio:

Se la simulazione è corretta si passa alla sintesi, la quale produce lo schema elettrico, es:

10

Nella sintesi i blocchi dell’FPGA sono generici, nella fase successiva di place & route invece le

risorse usate saranno reali:

Il place & route è un processo semi-automatico nel quale è possibile inserire diversi vincoli,

ad esempio che venga occupata la minore area possibile, oppure vincoli temporali tra due

connessioni, ecc; quindi per ottenere una simulazione corretta ci sono molti vincoli che devono

essere rispettati.

Non sempre il processo di place & route viene completato in automatico, a volte perché il

circuito è troppo complesso, a volte perché è proprio impossibile rispettare i vincoli.

In tali casi si può agire manualmente sulla matrice dei CLB o sulle risorse usate.

11

Cenni sul VHDL

Il VHDL è un linguaggio standard per la descrizione dell’hardware (Hardware Description

Language) , che può essere utilizzato per la documentazione, la simulazione e la sintesi di sistemi

digitali. Il VHDL è stato introdotto come linguaggio standard per la documentazione di sistemi

digitali complessi, è nato con lo scopo di fornire una descrizione non ambigua di un sistema

digitale, che potesse essere interpretata univocamente dai vari progettisti impegnati nello sviluppo

dello stesso sistema. Una delle caratteristiche del VHDL è quella di poter simulare il sistema

descritto, sia a livello funzionale sia tenendo conto dei ritardi del circuito; esso consente infatti di

descrivere efficacemente sistemi complessi cui corrispondono netlist di milioni di porte logiche

elementari, così come in un programma software ad alto livello è possibile ottenere facilmente

programmi in linguaggio macchina costituiti da milioni di istruzioni elementari a partire da un

listato di poche centinaia di righe. Un ulteriore vantaggio legato all’utilizzo di programmi di sintesi

è legato al fatto che la descrizione di un sistema digitale in VHDL può essere (quasi del tutto)

indipendente dalla particolare tecnologia scelta per l’implementazione del circuito, così come un

programma descritto in un linguaggio ad alto livello può essere compilato ed eseguito su

piattaforme hardware differenti.

Cenno alle differenze tra DSP e FPGA

DSP e FPGA coprono due fasce di mercato diverse; per applicazioni in cui è richiesta una

grande potenza di calcolo è sicuramente meglio l’utilizzo dei DSP (per via dell’architettura,

parallelismi vari, ecc…), mentre per gli FPGA è ancora la Glue-Logic a possedere la fetta di

mercato maggiore, sebbene non manchino esempi di applicazioni complete di controllo basate su

FPGA all-on-chip.

Un’altra importante differenza che allontana gli FPGA dal mondo dei DSP è la libertà di

configurazione dei PIN, quindi degli ingressi e delle uscite, i DSP infatti avevano una più rigida

configurazione della piedinatura. Il punto fondamentale quindi è che con un FPGA si ha una

maggiore flessibilità progettuale.

In un’applicazione in cui conviene l’utilizzo di un DSP, si inserisce spesso un FPGA

complementare, che possiede tutta la logica che non possiede il DSP, per sempio per generare

segnali si servizio (refresh per DRAM) o sincronismi verso i dispositivi di I/O.

12

Inoltre un FPGA costa molto di più di un DSP, infatti un DSP può costare poche decine di

dollari (5-10$ circa), mentre un FPGA economico può costare circa 100-150$.

III. Appendice: Esempi di FPGA commerciali

Fra i principali produttori di FPGA si annoverano Altera, Xilinx, ed ACTEL; dell’Altera

verranno considerati il MAX7000, il FLEX 8000, il FLEX10 e l’APEX20, mentre della Xilinx

verrà considerato l’XC4000.

Altera MAX7000

Nella figura sottostante viene riportato lo schema a blocchi di una MAX7000, dispositivo

EEPROM, dalle elevate prestazioni in termini di frequenza di funzionamento. Tale FPGA viene

realizzato in tre differenti versioni, con Core alimentato a 5, 3.3 o 2.5 volt. Ovviamente i dispositivi

a tensione minore sono quelli di ultima generazione, integrano perciò una tecnologia migliore che

permette di raggiungere il massimo delle frequenze operative. Come in quasi la totalità dei

dispositivi Altera, anche le MAX 7000 sono dotate di Multivolt I/O, ossia di un interfaccia che

permette di collegare logiche con tensione differente.

Particolare attenzione bisogna volgere al caso in cui si utilizzino FPGA con core a 3.3 v o 2.5

v. Per questi dispositivi la tensione massima di alimentazione dell’ interfaccia I/O è di 3.3 volt.

13

Nei ralativi datasheet però, viene dichiarata una compatibilità con le logiche a 5 volt;

ovviamente una porta di output, il cui buffer è alimentato a 3.3 volt non potrà mai arrivare a 5 volt;

il collegamento e’ possibile se il dispositivo a valle è conforme alle specifiche TTL 5V, per cui un

segnale maggiore di 2.4 V viene riconosciuto come livello alto.

Sebbene la figura di sopra riporti la struttura interna specifica di una MAX 7000 di Altera, si

può considerare tale schema significativo per capire come in generale sia fatto un FPGA; gli

elementi fondamentali sono:

•

Gruppi LAB (Logic Array Blocks) contenenti le macro-celle

•

Blocchi di connessione I/O

•

PIA (Programmable Interconnect Array)

•

Pin dedicati (GLCK1,GLCK2,OE1,OE2,GCLRn)

Un gruppo LAB, racchiude un certo numero di macro-celle, ossia i "nuclei" che realizzano le

strutture fondamentali del FPGA. Per capire a cosa servono tutti gli elementi visti nella struttura

generale bisogna analizzare la macro-cella nel dettaglio.

14

La parte combinatoria, della logica che si deve implementare, è svolta da una serie di porte

logiche predefinite, collegate in maniera opportuna, secondo le informazioni impartite dal

programma utilizzato per lo sviluppo del progetto. L’elemento che realizza fisicamente tali

connessioni è la Product Term Select Matrix. La cosa importante da osservare è che in questo

dispositivo, le funzioni logiche combinatorie sono realizzate effettivamente attraverso una struttura

logica cablata; negli FPGA RAM, le funzioni logiche combinatorie sono realizzate attraverso una

memoria, in cui gli indirizzi costituiscono gli ingressi della rete logica e le uscite i dati.

Questi due tipi di architetture hanno pregi e difetti facilmente intuibili; se da un lato

un’architettura micro-cablata permette di raggiungere prestazioni elevate in termini di tempi di

propagazione, d’altra parte l’integrazione che si riesce a raggiungere e’ notevolmente inferiore a

quella ottenibile attraverso una analoga struttura RAM. E’ comunque opportuno tenere a mente un

fatto sempre vero, ossia che confronti di questo tipo vanno fatti su logiche utilizzanti tecnologie

analoghe; ovviamente passando ad un processo costruttivo piu’ moderno si possono realizzare

logiche micro-programmate più veloci di quelle micro-cablate realizzate con una tecnologia di

cinque anni fa.

Qualora la macro-cella in questione non contenesse sufficienti elementi logici per

implementare al funzione combinatoria richiesta, è possibile utilizzare una macro-cella adiacente;

l’interconnessione avviene tramite i 16 Expander Product Terms. Notare che nel caso in cui questi

15

16 canali non bastassero, oppure le risorse interne al gruppo LAB fossero insufficienti, un ulteriore

espansione potrebbe avvenire unicamente attraverso il circuito a valle del registro, tramite una

nuova connessione con il PIA, con prestazione decisamente inferiori.

Come visibile da schema, se il registro presente in ogni macro-cella, risultasse non necessario

per la funzione che si deve realizzare, puo’ essere escluso attraverso un opportuno selettore. Altri

interruttori logici, permettono di selezionare da quale fonte prelevare segnali come il clock del

registro, il clear o il dato D. In particolare, è possibile connettere tali ingressi, ad un segnale

proveniente dalla parte combinatoria della macro-cella, oppure ad un ingresso dedicato; in

particolare, mentre il dato D puo’ essere collegato direttamente ad un pin di I/O, i segnali di clock e

clear possono essere assegnati ai rispettivi ingressi dedicati; per raggiungere le massime prestazioni

in termini di frequenza operativa, infatti, risulta indispensabile fare uso di questi I/O dedicati, in

particolare del Global Clock.

Altera FLEX8000, FLEX10K e APEX20k

Sono tutti dispositivi SRAM aventi la struttura di interconnessione chiamata FastTrack.

Questa modalità di interconnessione si realizza mediante dei fasci di fili raggruppati in righe o

colonne che attraversano il componente in tutta la sua dimensione. Esistono interconnessioni a tre

livelli tipiche delle famiglie FLEX8000 e FLEX10K, e interconnessioni a quattro livelli tipiche

della famiglia APEX20K.

Nelle strutture ad interconnessione a tre livelli i Logic Element sono organizzati in gruppi di

otto o dieci per formare un blocco denominato Logic Array Block (LAB). I LAB sono organizzati

in forma di matrice di righe e colonne e tra questi sono inseriti dei canali di routing sia orizzontali

che verticali che forniscono le necessarie connessioni. L’interconnettività all’interno di un LAB è

fornita da canali di interconnessione locali denominati LAB Local Interconnect. Il passaggio da

colonna a riga è compiuto mediante dei multiplexer programmati in fase di configurazione e

selezionati, in base al tipo di routing compiuto, mediante le celle static RAM della memoria di

configurazione.

Quando un LE di un LAB deve essere connesso a un LE di un qualsiasi altro LAB del

dispositivo il segnale viene immesso in un canale della colonna che lambisce il LAB, poi in un

canale della riga che serve il LAB destinatario e quindi raggiunge il LE mediante un canale del

Local Interconnect. I canali usati per questo collegamento appartenenti sia ad una riga che ad una

colonna, anche se in misura minore rispetto alla loro lunghezza totale, non possono più essere

utilizzati per un altro collegamento. Se il LAB destinatario appartiene alla stessa riga del sorgente è

16

possibile evitare il passaggio mediante colonna entrando direttamente nella riga. Se il LE sorgente

appartiene allo stesso LAB del LE destinatario allora è possibile evitare anche il passaggio della

riga per compiere direttamente la connessione mediante l’interconnessione interna del LAB.

Nella famiglia APEX20K sono previsti quattro livelli di interconnessione. Dieci Logic

Element sono raggruppati in un LAB e sedici LAB e un blocco embedded ESB (Embedded System

Block) sono raggruppati insieme per formare un MegaLAB.

L’ESB può essere una ram, una rom, una cam, un blocco di sedici macrocelle basate sulla

struttura a product term, xor e flip flop. L’interconnessione tra i LAB adiacenti è fornita dal Local

Interconnect in maniera simile a come avviene nella FLEX8000, mentre l’interconnessione

all’interno del MegaLAB è garantita dal MegaLAB Interconnect. All’interno del componente i

MegaLAB sono connessi mediante canali di routing costituiti da righe e colonne. Sia per le

interconnessioni a tre livelli che a quattro, alcuni blocchi di I/O sono direttamente connessi con i

canali verticali, altri con quelli orizzontali.

Di seguito sono riportati i diagrammi a blocchi dei rispettivi dispositivi.

FLEX8000:

17

FLEX10K:

APEX20K:

18

Xilinx XC4000

La serie XC4000 viene implementata con un’architettura di CLB regolare,flessibile e

programmabile, circondata da un perimetro di blocchi di I/O programmabili (IOB).

I CLB forniscono gli elementi funzionali per la costruzione della parte logica, mentre gli IOB

serviranno da interfaccia tra i pin del package e le linee dei segnali interni. I principali elementi

CLB sono mostrati nella figura seguente:

Sono presenti due generatori di funzione a 4 ingressi (F e G) le cui uscite possono essere

mandate all’ingresso di un terzo generatore di funzione a tre ingressi (H). Almeno un ingresso di H

sarà esterno al CLB. Ogni CLB contiene due elementi di memoria (Flip-Flop) che possono essere

usati per immagazzinare i risultati dei generatori di funzione.

L’XC4000 adotta una logica per la propagazione rapida del carry tra i CLB secondo questo schema:

19

Quando non sono presenti CLB in alto o in basso (quindi ai vertici di questo schema) il carry

viene propagato a destra. La figura seguente mostra lo schema di tale logica:

20

Per formare la somma i carry output sono combinati con gli operandi nei generatori di

funzione.

Per quanto riguarda gli IOB un diagramma a blocchi semplificato può essere il seguente:

L1 e L2 portano i segnali di ingresso nell’array e sono connessi ad un registro che può

funzionare da flip-flop o da latch. Gli ingressi L1 e L2 possono essere ritardati di diversi

nanosecondi prima di entrare nel registro, in modo da alzarne il tempo di set-up.

I segnali di uscita (out) possono passare direttamente al pad o essere immagazzinati nel flipflop.

Il segnale T serve a mettere in alta impedenza il buffer di uscita.

21

Le linee di connessione dei CLB sono illustrate nel seguente diagramma ad alto livello:

La seguente tabella mostra quante linee sono disponibili a seconda del loro tipo:

22

Il seguente diagramma invece rappresenta dettagliatamente il CLB con le relative linee di

connessione:

Gli ingressi e le uscite sono presenti su tutti e quattro i lati in modo da fornire la massima

flessibilità; in generale l’intera architettura è simmetrica e regolare.

Le linee orizzontali e verticali intersecano in un box chiamato PSM (Programmable Switch

Matrix).

Ogni matrice di interruttori consiste di pass transistor programmabili,usati per stabilire le

connessioni tra le linee (vedere figura 26 nella pagina precedente).

Le linee possono essere singole, doppie, quadruple (solo per l’XC4000X) e lunghe:

23

Le linee singole sono otto verticali e otto orizzontali per ogni CLB e sono usate nelle

connessioni tra le PSM dei CLB. Le linee doppie sono quattro verticali e quattro orizzontali per

ogni CLB e corrono attraverso due CLB prima di entrare in una PSM, sono lunghe il doppio delle

linee singole. Le linee quadruple sono dodici verticali e dodici orizzontali per ogni CLB, corrono

attraverso quattro CLB prima di entrare in una PSM e sono quattro volte più lunge delle linee

singole.

Le linee lunghe attraversano tutto l’array per lunghezza o per larghezza e sono usati per il

fan-out o per reti distribuite in lunghe distanze.

24