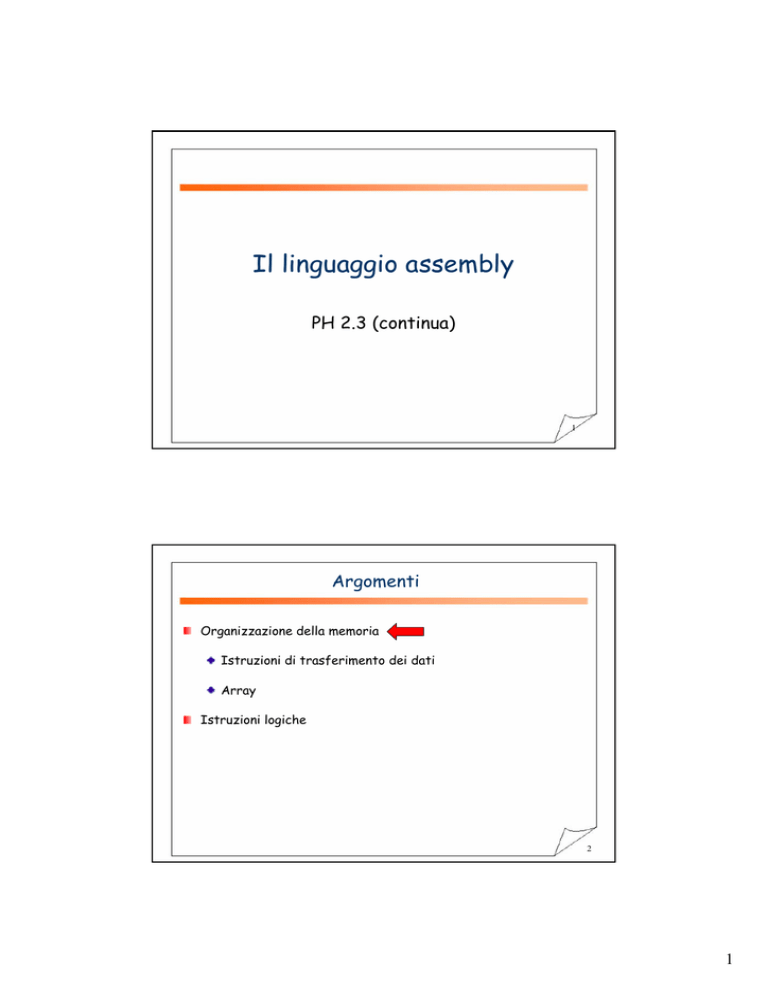

Il linguaggio assembly

PH 2.3 (continua)

1

Argomenti

Organizzazione della memoria

Istruzioni di trasferimento dei dati

Array

Istruzioni logiche

2

1

La memoria del MIPS

I contenuti delle locazioni di memoria possono rappresentare

sia istruzioni che dati (sequenze di bit, numeri)

La memoria è vista come un unico grande array unidimensionale

di bytes

Un indirizzo di memoria costituisce un indice all'interno

dell'array

MIPS utilizza un indirizzamento al byte, cioè l'indice punta ad

un byte di memoria

Byte consecutivi hanno indirizzi consecutivi

Indirizzi di parole consecutive (adiacenti) differiscono di un

fattore 4 (8-bit x 4 = 32-bit).

3

Indirizzamento dei bytes all’interno della parola

4

2

Endianess

Due modi di memorizzare una parola in memoria:

Big Endian

memorizza il byte più significativo nell'indirizzo più basso

( memorizza il byte meno significativo nell'indirizzo più alto )

Little Endian

memorizza il byte meno significativo nell'indirizzo più basso

( memorizza il byte più significativo nell'indirizzo più alto )

5

Indirizzamento della memoria

Gli indirizzi di parole adiacenti in memoria differiscono per un

fattore quattro (8-bitx4 = 32-bit)

In MIPS ogni parola (word) deve iniziare ad un indirizzo

multiplo di 4 (allineamento a parola)

Half word (16-bit) allineate ai multipli di 2

Per convenzione l’indirizzo di una parola coincide con l’indirizzo

del suo byte più a sinistra (disposizione big-endian)

6

3

Indirizzamento della memoria

0

32 bit

4

32 bit

8

32 bit

12

32 bit

16

32 bit

20

24

32 bit

32 bit

28

32 bit

7

Organizzazione logica della memoria

Nei sistemi basati su processore MIPS la memoria è

solitamente divisa in tre parti:

Segmento testo: contiene le istruzioni del programma

Segmento dati: ulteriormente suddiviso in:

dati statici: contiene dati la cui dimensione è conosciuta

al momento della compilazione e il cui intervallo di vita

coincide con l’esecuzione del programma

dati dinamici: contiene dati ai quali lo spazio è allocato

dinamicamente al momento dell'esecuzione del

programma su richiesta del programma stesso

Segmento stack: contiene lo stack allocato

automaticamente da un programma durante l'esecuzione

8

4

Organizzazione logica della memoria

7fffffff16

Stack segment

Dynamic data

Data segment

Static data

1000000016

Text segment

0040000016

Reserved

9

Istruzioni di trasferimento dei dati

MIPS fornisce due operazioni base per il trasferimento dei

dati da memoria a registro e viceversa:

lw (load word) per trasferire una parola di memoria in un

registro della CPU

sw (store word) per trasferire il contenuto di un registro

della CPU in una parola di memoria

Argomento di lw e sw è l’indirizzo della locazione di memoria da

cui leggere o scrivere una parola

10

5

Istruzione load

L'istruzione di load trasferisce una copia della parola

(dati/istruzioni) contenuta in una specifica locazione di

memoria ai registri della CPU

lw $t0, ind

# $t0 ← mem[ind]

La CPU invia l'indirizzo della locazione desiderata alla memoria

e richiede un‘operazione di lettura del suo contenuto

La memoria effettua la lettura dei dati memorizzati

all'indirizzo specificato e li invia alla CPU

11

Istruzione di store

L'istruzione di store trasferisce una parola di informazione dai

registri della CPU in una specifica locazione di memoria,

sovrascrivendo il precedente contenuto di quella locazione:

sw $t1, ind # mem [ind] ← $t1

La CPU invia l'indirizzo della locazione desiderata alla memoria,

assieme con i dati che vi devono essere scritti e richiede

un'operazione di scrittura

La memoria effettua la scrittura dei dati all'indirizzo

specificato.

12

6

Sintassi di Load

Nel MIPS, l’istruzione lw ha tre argomenti:

il registro destinazione in cui caricare la parola letta dalla

memoria

una costante o spiazzamento (offset)

un registro base (base register) che contiene il valore

dell‘indirizzo base (base address) da sommare alla costante

L’indirizzo della parola di memoria da caricare nel registro

destinazione è ottenuto dalla somma della costante e del

contenuto del registro base

La costante può anche essere una espressione che

l’assemblatore può calcolare (compile time)

13

Istruzione lw

lw $s1, 100($s2)

# $s1 ← mem[$s2 + 100]

Al registro destinazione $s1 è assegnato il valore contenuto

all’indirizzo di memoria ($s2 + 100)

14

7

Istruzione sw

sw possiede argomenti analoghi alla lw

Esempio:

sw $s1, 100($s2) # mem[$s2 + 100] ← $s1

Alla locazione di memoria di indirizzo ($s2 + 100) è assegnato il

valore contenuto nel registro $s1

15

Calcolo dell’indirizzo

load/store il contenuto

della locazione con indirizzo

sw $t0, 4($sp)

indirizzo

indirizzo è :: ($sp

($sp ++ 4)

4)

sw $t0, 4($fp)

-4($fp)

l'indirizzo

($fp – 4)

l'indirizzo è:

è: ($fp

lw $a0, 0($sp)

lw $a0, ($sp)

sw $t0, arr($t0)

lw $a0, var($

($zero

zero)

)

var

var($zero)

lw $a0, var

l'indirizzo

l'indirizzo è: ($sp + 0)

0)

l'indirizzo

l'indirizzo è:

($t0

($t0 ++ indirizzo

indirizzo di

di arr)

arr)

l'indirizzo

l'indirizzo è:

($zero

zero + indirizzo

($

var

($zero

indirizzo di

di var)

var))

16

8

Istruzioni load and store

Esempio:

.text # text segment

lw $t1, op1 # carica op1

lw $t2, op2 # carica op2

add $t0, $t1,$t2 # op1 + op2

sw $t0, ris

# memorizza ris

.data

op1: .word

op2: .word

ris: .word

# data segment

4

op1

3

0

op2

4

ris

0

3

17

Istruzioni load and store

7fffffff16

Stack segment

Dynamic data

op1

4

op2

3

ris

0

Data segment

Static data

1000000016

Text segment

0040000016

Reserved

18

9

Argomenti

Organizzazione della memoria

Istruzioni di trasferimento dei dati

Array

Operazioni logiche PH 2.5

19

Array

$S3 + 0

A[0]

$S3 + 4

A[1]

$S3 + 8

A[2]

$S3 + 12

A[3]

20

10

Array

L'elemento i-esimo di un array si troverà nella locazione:

registro-base + 4 * i

dove:

registro-base è il registro base (base register)

"i" è l'indice ad alto livello

il fattore 4 dipende dal dall'indirizzamento al byte della

memoria nel MIPS

21

Array: esempio 1

Sia A un array di 100 word

Istruzione C:

g = h + A[8];

Si suppone che:

le variabili g, h siano associate rispettivamente ai registri

$s1 e $s2

l'indirizzo del primo elemento dell'array (base address) sia

contenuto nel registro $s3

In MIPS

ggin

in $s1

$s1

hhin

in $s2

$s2

addr.A

addr.Ain

in$s3

$s3

lw $t0, 32($s3)

# t0 = A[8]

add $s1, $s2, $t0

# g = h + A[8]

22

11

Array: esempio 2

Sia A un array di 100 word

Istruzione C:

g = h + A[i];

Si suppone che:

ggin

in $s1

$s1

hhin

in $s2

$s2

ii in

in $s4

$s4

addr.A

addr.Ain

in$s3

$s3

23

Array: esempio 2 (cont.)

L'elemento i-esimo dell'array si trova nella locazione di

memoria di indirizzo ($s3 + 4 * i)

Costruzione dell'indirizzo di A[i] nel registro temporaneo $t1:

add $t1, $s4, $s4

add $t1, $t1, $t1

add $t1, $t1, $s3

#

#

#

#

St1 <- 2 * i

$t1 <- 4 * i

$t1 <- add. of A[i]

cioè ($s3 + 4 * i)

Per trasferire A[i] nel registro temporaneo $t0:

lw $t0, 0($t1) # $t0 <- A[i]

Per sommare h e A[i] e mettere il risultato in g:

add $s1, $s2, $t0 # g = h + A[i]

g in $s1

h in $s2

i in $s4

addr.A in $s3

24

12

Indirizzo di un array (pseudo istruzione la)

Un array è allocato nella porzione static data del data segment

Pseudo istruzione load address :

la rdest,

rdest symbolicsymbolic-address

es: la $s3, vet

durante la compilazione vet è noto

25

Argomenti

Organizzazione della memoria

Istruzioni di trasferimento dei dati

Array

Istruzioni logiche

26

13

Operazioni logiche

Operazioni di shift logico

right (srl)

in Java <<

left (sll)

in Java >>

Logico = riempito con '0‘

shift massimo: 31 bit

Esempio: sll $t0, $t1, 3 # equivale moltiplicare per 8 =23

$t1: 0000 0000 0000 0000 1100 1000 0000 1111

$t0: 0000 0000 0000 0110 0100 0000 0111 1000

Formato istruzione

27

Operazioni logiche

AND bit a bit

and $t0, $t1, $t2

andi $t0, $t1, 3

OR bit a bit

or $t0, $t1, $t2

ori $t0, $t1, 3

Esempio:

$t0:

$t1:

$s0:

$s1:

in Java

&

in Java

|

and $s0, $t0, $t1

or $s1, $t0, $t1

0000 0000 0000 0110 0100 0000 0111 1000

0000 0000 0000 0000 1100 1000 0000 1111

0000 0000 0000 0000 0100 0000 0000 1000 and

0000 0000 0000 0110 1100 1000 0111 1111 or

28

14

Array: esempio 2 (seconda versione)

Sia A un array di 100 word

Istruzione C:

g = h + A[i];

MIPS :

sll

sll $t1,

$t1, $s4,

$s4, 22

add

add $t1,

$t1, $t1,

$t1, $s3

$s3

lw

lw $t0,

$t0, 0($t1)

0($t1)

add

add $s1,

$s1, $s2,

$s2, $t0

$t0

##

#

##

##

#

ggin

in $s1

$s1

hhin

in $s2

$s2

ii in

in $s4

$s4

addr.A

addr.Ain

in$s3

$s3

St1

St1 <<- 44 ** ii

$t1 <- add. of A[i]

cioè

cioè ($s3

($s3 ++ 44 ** i)

i)

St0

St0 <<- A[i]

A[i]

g = h + A[i]

29

15