Curriculum Vitae del Dott. Ing. Paolo Zicari

1

Informazioni generali

2

Percorso Formativo

3

Attività didattiche e professionali

4

Conoscenze specifiche riguardanti aspetti teorici, metodologici ed

applicativi

5

Attività di ricerca scientifica

5.1 Progetto e realizzazione di circuiti riconfigurabili per le comunicazioni

5.2 Progetto e realizzazione di circuiti e sistemi per l’accelerazione di

operazioni multimediali

5.3 Progetto e realizzazione di sistemi per l’elaborazione di immagini

5.4 Progetto e realizzazione di tecniche per rendere affidabili i circuiti per

applicazioni spaziali

5.5 Pubblicazioni scientifiche

1. Informazioni Generali

Nome:

Paolo Zicari

Luogo di nascita :

Cosenza

Data di nascita:

30/03/1973

Professione:

Assegnista di ricerca presso il Dipartimento di

Elettronica Informatica e Sistemistica dell’Università

degli Studi della Calabria, Via P. Bucci 42C, I piano,

CAP 47036, Arcavacata di Rende (CS)

Professore

a

Contratto

Mediterranea di Reggio Calabria

Telefono dello studio:

+39 0984 49 4647

E-mail:

[email protected]

presso

l’Università

2. Percorso Formativo

Diploma di maturità scientifica

conseguito in giugno 1992

presso il liceo scientifico “E. Fermi” di Cosenza, con voti 60/60.

Laurea in Ingegneria Informatica

conseguita in Ottobre 1998

presso l’Università della Calabria, Arcavacata di Rende (CS)

con voti 110/110 e lode

Titolo della tesi: “Implementazione di un algoritmo SRT per il calcolo della divisione e

della radice quadrata in floating point e programmazione di un FPGA (Field

Programmable Gate Array) per l’accelerazione dell’ALU (Aritmetic Logic Unit) di un

processore general purpose”.

Dottorato di Ricerca in Ingegneria Elettronica, XVIII ciclo

conseguito il 6 Marzo 2006

presso l’Università Mediterranea di Reggio Calabria con sede consorziata Università

della Calabria, D.E.I.S. (Dipartimento di Elettronica Informatica e Sistemistica).

Titolo della tesi: “I Systems on Programmable Chip: progetto di soluzioni innovative

per il trattamento di immagini e di segnali”

Tirocinio di Ricerca

Programmi Regionali ed Extra regionali di Alta Formazione annualità 2005-2007 in

attuazione del Programma Integrato di Voucher e Borse per l'

Alta formazione misura 3,7 - BURC Suppl. Straord. n.1 del 18 giugno 2007 al n. 24 del 15 giugno

2007

Marzo 2008 – Dicembre 2008

presso DEIS (Dipartimento di Elettronica Informatica e Sistemistica) dell’Università

della Calabria e CNR- IMM (Consiglio Nazionale delle Ricerche, Istituto per la

Microelettronica e i Microsistemi) sezione di Napoli

Titolo del tirocinio: “Nuove Tecnologie Di Interconnessione Per Circuiti LogicoProgrammabili Per Applicazioni Multimediali”

Corso “Design of Modern Integrated Transceivers”

8-12 Maggio 2006, presso il Dipartimento di Ingegneria dell'

Informazione: Elettronica,

Informatica, Telecomunicazioni, via G. Caruso, Pisa,

tenuto dal Prof. Pietro Andreani (Center for Physical Electronics, Technical University

of Denmark, Lyngby)

Corso “Advanced On-Chip Interconnect”

21-22 Giugno 2006, DEIS Università della Calabria, Arcavacata di Rende (CS)

tenuto dal Prof. Eby G. Friedman (Università di Rochester USA)

Scuola di dottorato in Ingegneria Elettronica

9-14 Giugno 2003, Passignano sul Trasimeno (PG)

Organizzata dal gruppo di elettronica GE 2003 con argomento “Progettazione a

Radio Frequenza”

Corso di lingua inglese di secondo livello per dottorandi

anno 2003, presso il DEIS dell’Università degli Studi della Calabria.

Corso “Training in Isolator & QCAM PCB Prototyping System”

6-7 Ottobre 1999, presso ST Microelectronics Pennsylvania, USA

Realizzazione di circuiti stampati.

Corso “Basic Training in Soldering PCB and PCB to Copper Core”

7 Ottobre 1999, presso ST Microelectronics Pennsylvania, USA

Realizzazione di circuiti stampati.

Corso di UML (Unified Modeling Language)

02-06 Aprile 2002, Selvin Wright

Progettazione e analisi di sistemi informativi.

MobileAcademy, Microsoft – O2

13-17 Maggio, Reading (UK)

Conferenza sulle soluzioni mobile, MMIS (Microsoft Mobile Information Server),

Mobile Tool Kit, Mobile Web Application, Server Activ Sync, Security in mobile.

Corso di Inglese: “General English Course”

2 settimane, Giugno 2009

EF International School, Miami, FL (USA)

Corso di Inglese: “General English Course”

Marzo-Aprile 2001, Londra (UK)

Greenwich School of English

Corso di Inglese: “Callan Method”

30 lezioni, Agosto 1994

Callan School of English, Londra (UK)

3. Attività Didattiche e Professionali

•

Gennaio 2006 – oggi: Assegnista di ricerca presso il Dipartimento di

Elettronica Informatica e Sistemistica (DEIS), Facoltà di Ingegneria, Università

degli Studi della Calabria;

•

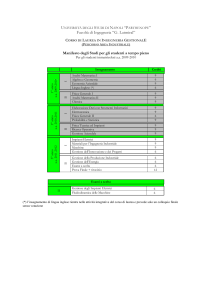

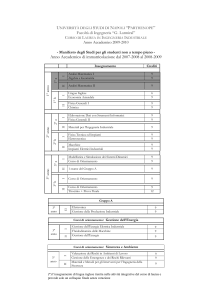

Anno Accademico 2008-2009: Docente a contratto dell’insegnamento di

“Elettronica dei Sistemi Digitali I” del corso di laurea in Ingegneria Elettronica

presso l’Università Mediterranea di Reggio Calabria, Facoltà di Ingegneria;

•

Anno Accademico 2007-2008: Docente a contratto dell’insegnamento di

“Elettronica dei Sistemi Digitali I” del corso di laurea in Ingegneria Elettronica

presso l’Università Mediterranea di Reggio Calabria, Facoltà di Ingegneria;

•

Anno Accademico 2006-2007: Docente a contratto dell’insegnamento di

“Elettronica dei Sistemi Digitali I” del corso di laurea in Ingegneria Elettronica

presso l’Università Mediterranea di Reggio Calabria, Facoltà di Ingegneria;

•

Anno

Accademico

2008-2009:

Esercitatore

per

l’insegnamento

di

“Complementi di Circuiti Integrati Riconfigurabili” del corso di laurea

specialistica in Ingegneria Elettronica presso l’Università degli Studi della

Calabria, Facoltà di Ingegneria;

•

Anno Accademico 2008-2009: Esercitatore per l’insegnamento di “Circuiti

Logici Riconfigurabili” dei corsi di laurea specialistica in Ingegneria Informatica

e Ingegneria Automatica presso l’Università degli Studi della Calabria, Facoltà

di Ingegneria;

•

Anno

Accademico

2007-2008:

Esercitatore

per

l’insegnamento

di

“Complementi di Circuiti Integrati Riconfigurabili” del corso di laurea

specialistica in Ingegneria Elettronica presso l’Università degli Studi della

Calabria, Facoltà di Ingegneria;

•

Anno Accademico 2007-2008: Esercitatore per l’insegnamento di “Circuiti

Logici Riconfigurabili” dei corsi di laurea specialistica in Ingegneria Informatica

e Ingegneria Automatica presso l’Università degli Studi della Calabria, Facoltà

di Ingegneria;

•

Marzo 2008 – Dicembre 2008: Tirocinio di Ricerca per Programmi Regionali

ed Extra regionali di Alta Formazione annualità 2005-2007 in attuazione del

Programma Integrato di Voucher e Borse per l'

Alta formazione - misura 3,7 BURC Suppl. Straord. n.1 del 18 giugno 2007 al n. 24 del 15 giugno 2007,

“NUOVE TECNOLOGIE DI INTERCONNESSIONE PER CIRCUITI LOGICOPROGRAMMABILI PER APPLICAZIONI MULTIMEDIALI” presso le seguenti

strutture: DEIS (Dipartimento di Elettronica Informatica e Sistemistica)

dell’Università della Calabria e CNR- IMM (Consiglio Nazionale delle Ricerche,

Istituto per la Microelettronica e i Microsistemi) sezione di Napoli;

•

Anno 2008: Esperto Informatico per la docenza del modulo “D 1 FSE 200751” Interventi formativi rivolti ai docenti e al personale della scuola, sulle nuove

tecnologie della comunicazione”, 30 ore. PROGETTO PON azione D 1 FSE

2007- 51, presso la Scuola Media “B. Zumbini”, via Roma, Cosenza.

•

Anno 2008: Esperto Informatico per la docenza del modulo “Informatica di

base”, Fondo Sociale Europeo “Competenze per lo Sviluppo”, Fondo Europeo

Sviluppo Reg.le “Ambienti per l’apprendimento” 2007 – IT 16 1 PO, 30 ore,

presso la Scuola Media Statale, Sezione staccata di San Giacomo d’Acri (Cs).

•

Anno

Accademico

2006-2007:

Esercitatore

per

l’insegnamento

di

“Complementi di Circuiti Integrati Riconfigurabili” del corso di laurea

specialistica in Ingegneria Elettronica presso l’Università degli Studi della

Calabria, Facoltà di Ingegneria;

•

Anno Accademico 2006-2007: Esercitatore per l’insegnamento di “Circuiti

Logici Riconfigurabili” dei corsi di laurea specialistica in Ingegneria Informatica

e Ingegneria Automatica presso l’Università degli Studi della Calabria, Facoltà

di Ingegneria;

•

Luglio 2006: Chairman della sessione 3 “Communication System” alla terza

conferenza internazionale sui circuiti e sistemi per le comunicazioni (3rd

International Conference on Circuits and Systems for Communications)

tenutasi il 6 e 7 luglio 2006 presso l’Università Politecnica di Bucharest,

Romania.

•

Anno Accademico 2005-2006: Esercitatore per l’insegnamento di “Circuiti

Logici Riconfigurabili” dei corsi di laurea specialistica in Ingegneria Informatica

e Ingegneria Automatica presso l’Università degli Studi della Calabria, Facoltà

di Ingegneria;

•

Anno

Accademico

2005-2006:

Esercitatore

per

l’insegnamento

di

“Complementi di Circuiti Integrati Riconfigurabili” del corso di laurea

specialistica in Ingegneria Elettronica presso l’Università degli Studi della

Calabria, Facoltà di Ingegneria;

•

Anno Accademico 2004-2005: Esercitatore per l’insegnamento di “Progetto di

Elettronica Digitale” del corso di laurea in Ingegneria Elettronica nuovo

ordinamento presso l’Università degli Studi della Calabria, Facoltà di

Ingegneria;

•

Correlatore di numerose tesi di laurea in Ingegneria Elettronica presso

l’Università della Calabria;

•

Ottobre 2002 – Settembre 2005: Dottorato di Ricerca in Ingeneria Elettronica

presso l’Università Mediterranea di Reggio Calabria con sede consorziata

Università della Calabria, D.E.I.S. (Dipartimento di Elettronica Informatica e

Sistemistica);

•

Anno 2002: contratto di “esperto esterno di settore” per docenza “modulo

multimedia” di 30 ore, progetto PON “AMBITEC-AMBIENTE E TECNOLOGIA”

finanziato dal M.I.U.R. (prot. N. 9977/int/u05 del 28/05/2004) presso la scuola

media statale “G. Pucciano” di Bisignano (CS), cod. mecc. CSMM05200X;

•

Anno 2002: Docente del corso “TECNICHE DI PROGETTAZIONE CON I

DESIGN PATTERNS” di 16 ore. Incarico di collaborazione occasionale, per

attività di docenza. Progetto di Formazione “Operatori di Progetto” –

Finanziamento M.I.U.R., Sottotema “Rifocalizzazione professionale personale

esistente”,

Linea

1.3

“Formazione

specialistica attinente

al

progetto

d’innovazione LP2” presso il CALPARK – PARCO SCIENTIFICO E

TECNOLOGICO DELLA CALABRIA, C.da Santo Stefano 87036 Rende (CS).

•

Anno 2002: Docente del corso “FONDAMENTI DI INFORMATICA” di 75 ore.

Incarico di collaborazione occasionale per attività di docenza, POR Calabria,

Annualità 2000/2001 – corso IFTS Cod. 43 – “Project Manager di Ecommerce”, presso LAIF, Consorzio per il Lavoro e le Attività Innovative e

Formative, Rende via Don Minzioni 95 (CS);

•

Anno 2002: Docente del corso “Alfabetizzazione Di Informatica” di 15 ore.

Incarico di collaborazione occasionale per attività di docenza, POR Calabria,

Annualità 2000/2001 – corso IFTS Cod. 43 – “Project Manager di Ecommerce”, presso LAIF, Consorzio per il Lavoro e le Attività Innovative e

Formative, Rende via Don Minzioni 95 (CS);

•

Anno 2002: Docente del corso “Fondamenti Di Informatica” di 72 ore. Incarico

di collaborazione occasionale per attività di docenza, POR Calabria, Annualità

2000/2001 – corso IFTS Cod. 44 – “Web Site Developer”, presso LAIF,

Consorzio per il Lavoro e le Attività Innovative e Formative, Rende via Don

Minzioni 95 (CS);

•

Anni

2001-2002:

Consulente

ICT

(Information

and

Communication

Technology) presso la NOTANGLE s.r.l.;

•

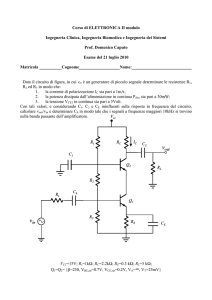

Settembre 1999 – Ottobre 2000: Power RF Application Engineer presso

l’STMicroelectronics per il progetto e la realizzazione di amplificatori RF da

utilizzare per il test dei dispositivi a semiconduttore LDMOS:

o LDMOS SD57045, N-Channel enhancement mode lateral

mosfet, Pout = 45W PEP with 13 db gain @ 945MHz

o LDMOS SD57030, N-Channel enhancement mode lateral

mosfet, Pout = 30W PEP with 13 db gain @ 945MHz

o LDMOS SD57070, N-Channel enhancement mode lateral

mosfet, Pout = 70W PEP with 13 db gain @ 945MHz

o LDMOS SD59030, N-Channel enhancement mode lateral

mosfet, Pout = 30W PEP with 10 db gain @ 2GHz

La strumentazione utilizzata ha previsto l’impego di S-parameter

network analyzer, power-meter, attenuatori, accoppiatori direzionali;

•

Marzo 1999 – Settembre 1999: Borsista per la ricerca nel campo dei

componenti elettronici presso il CNR IRECE (Istituto di Ricerca per

l’Elettromagnetismo e i Componenti Elettronici), Napoli;

•

Gennaio 1999-Marzo 1999: Contrattista di formazione lavoro presso Pitagora

S.P.A.

4. Competenze specifiche riguardanti aspetti teorici, metodologici

ed applicativi.

•

Impiego di programmi CAD per la progettazione di circuiti elettronici: Cadence,

Spice, Hspice;

•

Progettazione di circuiti elettronici mediante linguaggio VHDL e Verilog;

•

Impiego di programmi CAD per la progettazione di circuiti elettronici su

piattaforma riconfigurabile FPGA (Field Programmable Gate Array): Xilinx ISE;

•

Progettazione di System on Programmable Chip con utilizzo di processori

embedded tramite CAD Xilinx EDK;

•

Sistemi operativi DOS, Windows e Sun Os Solaris;

•

Linguaggi di programmazione: Java , C/C++/C#, SQL, HTML, Prolog;

•

Software di sviluppo: Visual Studio .NET, Visual Studio, Embedded Visual

Studio;

•

Ottima conoscenza della lingua Inglese scritta e parlata.

5. Attività di ricerca scientifica

5.1 Progetto e realizzazione di circuiti riconfigurabili per le comunicazioni

I moderni sistemi di comunicazione richiedono un’elevata flessibilità al fine di

supportare la rapida evoluzione degli standard dei protocolli di comunicazione, la

comunicazione in differenti bande, e la possibilità di rinnovare le funzionalità offerte.

Le Software Defined Radios (SDR) costituiscono la soluzione emergente a questo

tipo di esigenza; inoltre gli FPGA (Field Programmable Gate Array) forniscono

l’appropriato supporto per la realizzazione di hardware riconfigurabile per tali tipi di

sistemi di comunicazione.

L’attività di ricerca condotta si è focalizzata sull’ottimizzazione di circuiti FPGA

rivolti alla sincronizzazione di bit, un’operazione che si pone al termine della catena

dei blocchi costituenti un sistema di ricezione, che svolge le funzioni di allineare

temporalmente il flusso di dati ricevuto con il flusso di dati trasmesso, e di rilevare e

interpretare correttamente il dato ricevuto.

Le pubblicazioni relative a tale campo di ricerca sono [RI3], [CI2], [CI3], [CI9],

[CI10] e [CI11].

5.2 Progetto e realizzazione di

circuiti e sistemi per l’accelerazione di

operazioni multimediali

I moderni algoritmi di elaborazione “real-time” dei segnali audio e video richiedono

architetture hardware in grado di effettuare operazioni aritmetiche con un elevato

throughput.

Il paradigma SIMD (Single Instruction Multiple Data), introdotto nelle architetture di

calcolo dedicate alle operazioni multimediali al fine di processare, con un alto livello

di parallelismo, dati a precisione variabile (tipicamente operandi interi a 8, 16, o 32bit), è stato adottato per la realizzazione di un SIMD Soft Microcontroller per FPGA

in [CI7], capace di aumentare notevolmente la velocità di esecuzione dell’unità ALU

su dati a bassa precisione, a discapito di un esiguo incremento di risorse hardware

rispetto all’architettura SISD (Single Instruction Single Data).

Le operazioni su matrici sono alla base delle architetture multimediali, tuttavia,

l’esecuzione da parte di processori general purpose richiede un elevato carico

computazionale dovuto alla sequenzialità del flusso di esecuzione, ed alla presenza

di istruzioni di salto e di controllo degli indici necessari alla scansione delle matrici.

Un’architettura di coprocessore ottimizzata per l’esecuzione del calcolo del prodotto

matriciale a supporto di processori soft e hard per FPGA è stata presentata in [RI2] e

[CI5]; l’introduzione del parallelismo nel calcolo insieme ad una stretta integrazione

tra sistema host e coprocessore opportunamente gestita tramite uno specifico

protocollo di comunicazione ha permesso di ridurre drasticamente il tempo di

esecuzione del prodotto matriciale.

Una soluzione circuitale ottimizzata al calcolo dell’operazione di accumulo nei

moduli MAC (Multiply And Accumulate) è stata proposta in [CI4], un sommatore

dalle prestazioni elevate e dalla bassa dissipazione di potenza è stato proposto in

[RI4], un moltiplicatore low power è stato proposto in [RI5].

5.3 Progetto e realizzazione di sistemi per l’elaborazione di immagini

Nell’ambito della tematica relativa all’elaborazione di immagini, sono stati seguiti due

filoni di interesse: la compressione di immagini e la visione tridimensionale.

Le tecniche di compressione di immagini più efficienti allo stato dell’arte si basano

sull’uso della trasformata wavelet discreta (DWT) abbinata ad algoritmi di

compressione nel

dominio trasformato. La DWT gode della proprietà di

rappresentare i segnali a diverse risoluzioni. Essa ha inoltre una buona caratteristica

di localizzazione delle singolarità, sia nel tempo che in frequenza, ed ha la capacità

di compattare l’energia in pochi coefficienti trasformati. Algoritmi efficienti di

compressione, come SPIHT e EZW, basano la codifica dei coefficienti trasformati

sulla rappresentazione della mappa di significatività mediante Zerotree. L’esecuzione

software di tali algoritmi è estremamente onerosa dal punto di vista computazionale

risultando spesso inefficiente sopratutto nel caso di applicazioni real-time. In tale

ambito è stata presentata un’architettura completa di Field Programmable Sytem on

Chip dedicata alla compressione di immagini basata su trasformata Wavelet discreta

bidimensionale ed algoritmo di codifica SPIHT in [CI6] e [RI1]. Un efficiente

partizionamento del sistema ha previsto la realizzazione di un circuito specifico per

l’esecuzione della trasformata Wavelet, e l’implementazione dell’algoritmo SPIHT

tramite una routine software in linguaggio C, ottimizzata per essere eseguita dal

processore soft Xilinx MicroBlaze; le due unità essendo interfacciate tramite bus

dedicato. La soluzione proposta risulta particolarmente efficiente sia in termini di costi

temporali, fornendo un elevato livello di accelerazione rispetto alle più lente

esecuzioni puramente software degli algoritmi di compressione, sia in termini di

occupazione di risorse circuitali, offrendo una soluzione competitiva rispetto ai core

hardware disponibili commercialmente. Nei confronti di questi ultimi, viene offerta una

maggiore flessibilità dovuta all’impiego di un processore che permette di variare

facilmente l’algoritmo di codifica con la sostituzione della routine software, senza la

necessità di modificare l’intero sistema.

Per

quanto

riguarda

la

visione

tridimensionale,

una

soluzione

circuitale

particolarmente efficiente e dalle elevate prestazioni è stata fornita per il problema

del matching delle finestre stereo basata sul calcolo delle SAD (Sum of Absolute

Differences) al fine di trovare la mappa di disparità necessaria al rilevamento della

profondità di una coppia i immagini stereo[CI1, CI8]. L’approccio adottato, sfruttando

in maniera innovativa il riutilizzo di operazioni comuni al computo del valore delle

SAD per finestre adiacenti, permette di ottenere un efficiente impiego di risorse

hardware ed elevate prestazioni in termini di PDS (PointsxDisparity per Second).

5.4 Progetto e realizzazione di tecniche per rendere affidabili i circuiti per

applicazioni spaziali

Un settore molto avanzato della ricerca scientifica, che vede coinvolti come principali

soggetti interessati la NASA e l’ESA, si occupa di rendere affidabili i circuiti quando

vengono utilizzati in applicazioni spaziali.

In tale direzione è stata condotta una

ricerca rivolta a rendere affidabili e tolleranti i circuiti elettronici implementati su

piattaforma riconfigurabile FPGA agli effetti SEU (Single Event Upset) dovuti alle

particelle ionizzanti presenti nello spazio, che sono causa di errori e quindi

malfunzionamenti. Particolare interesse ha suscitato nella comunità scientifica la

tecnica presentata al 5th International Workshop on Applied Reconfigurable

Computing, ARC2009 [CI12]. La tecnica proposta, applicabile ai più largamente

diffusi FPGA di tipo SRAM based, fornisce un sistema hardware intelligente capace

di auto-riconfigurarsi nel momento in cui rileva eventuali errori ingenerati da un

evento SEU, permettendo di correggere gli errori di configurazione che altrimenti

rimarrebbero

in

maniera

permanente

fino

ad

una

successiva

completa

riconfigurazione del sistema stesso. I benefici di un sistema di auto diagnostica e

auto correzione come quello proposto risultano evidenti se si considera che non si

rendono necessari sistemi esterni di controllo che a loro volta richiederebbero di

essere resi immuni agli effetti dei SEU.

5.5 Pubblicazioni scientifiche

[RI1] P.Corsonello, S.Perri, P.Zicari, G.Cocorullo, “Microprocessor-based FPGA

implementation of SPIHT image compression subsystems”, Microprocessors and

Microsystems,Vol.29, n°6, pp.299-305, The Netherlands, 2005.

[RI2] P. Zicari, P. Corsonello, S. Perri, G. Cocorullo, “A matrix product accelerator

for field programmable systems on chip”, Microprocessors and Microsystems,

Vol. 32, Issue 2, pp. 53-67, March 2008, Elsevier.

[RI3] P. Zicari, Emanuele Sciagura, Stefania Perri, Pasquale Corsonello, “A

Programmable Carrier-Phase Independent Symbol Timing Recovery Circuit for

QPSK/OQPSK Signals”, Microprocessors and Microsystems, Vol. 32, Issue 8, pp.

437-446, November 2008, Elsevier.

[RI4] Fabio Frustaci, Marco Lanuzza, Paolo Zicari, Stefania Perri, Pasquale

Corsonello, “Designing High Speed Adders in Power-Constrained

Environments”, Circuits and Systems II: Express Briefs, IEEE Transaction on

Circuits and Systems TCAS II, Volume 56, Issue 2, Feb. 2009. Page(s): 172 - 176.

[RI5] Fabio Frustaci, Marco Lanuzza, Paolo Zicari, Stefania Perri, Pasquale

Corsonello, “Low-Power Split-Path Data-Driven Dynamic Logic (SPD3L)”,

accepted by IET Circuits, Devices & Systems.

[CI1] S. Perri, D. Colonna, P. Zicari, P. Corsonello, “SAD-Based Stereo Matching

Circuit for FPGAs”, Proc. of the 13th IEEE International Conference on Electronics,

Circuits and Systems - ICECS’06, December 10-13, 2006, Nice, France.

[CI2] P. Zicari, P. Corsonello, S. Perri, “An Efficient Circuit for Bit-Detection and

Timing Recovery Using FPGAs”, Proc. of the 13th IEEE International Conference

on Electronics, Circuits and Systems - ICECS’06, December 10-13, 2006, Nice,

France.

[CI3] P. Zicari, P. Corsonello, S. Perri, “A high flexible Early-Late Gate Bit

Synchronizer in FPGA-Based Software Defined Radios”, Proc. of the 3rd

International Conference on Circuits and Systems for Communications - ICCSC’06,

July 6-7, 2006, Bucharest, Romania.

[CI4] P. Zicari, S. Perri, P. Corsonello, G.Cocorullo, “An optimized Adder

Accumulator for high speed MACs”, Proc. of the International Conference on

ASIC, ASICON 2005, October 24-27, Shanghai, China.

[CI5] P.Corsonello, S.Perri, P.Zicari, “A Matrix Product Coprocessor for FPGA

embedded soft processors”, International Symposium on Signals, System and

Circuits - ISSCS 2005, July 14-15, 2005, Iasi, Romania.

[CI6] P. Corsonello, S. Perri, P. Zicari, G. Cocorullo, “A FPSoC for wavelet-based

image compression”, Proc. of the International Conference on Signals and

Electronic Systems, September 2004, Poznan, Poland.

[CI7] S. Perri, P. Zicari, P. Corsonello, “A high flexible 8-bit and 16-bit SIMD soft

microcontroller for FPGAs”, Proc. of the International Conference on Signals and

Electronic Systems, September 2004, Poznan, Poland.

[CI8] S. Perri, D. Colonna, P. Zicari, P. Corsonello, “Flexible Hardware for AreaBased Stereo Matching”, Asia-Pcific Workshop on Visual Information Processing –

VIP 2006, November 7-9, 2006, Chinese Academy of Sciences, Beijing, China.

[CI9] E. Della Sala, E. Sciagura, D. De Caro, A. Caravella, P. Longobardi, P. Zicari,

V. Garofalo, G. Capuano, P. Corsonello, E. Napoli, G. M. Strollo, “HIGH RATE DATA

DOWN LINK”, 18th ESA Symposium on European Rocket and Balloon Programmes

and Related Research, 3-7 June 2007, Visby, Sweden.

[CI10] E. Sciagura, P. Zicari, S. Perri, P. Corsonello, "An efficient and optimized

FPGA Feedback M-PSK Symbol Timing Recovery Architecture based on

Gardner Timing Error Detector". Atti del convegno "IEEE 10th EUROMICRO

Conference on Digital System Design", Lubeck (Germania), 2007.

[CI11] P. Zicari, G. Cocorullo, “Radio Frequency Identification and Integrity

Control System for collision monitoring”, Proc. of the International Conference on

Signals and Electronic Systems, ICSES’08, 14 -17 September 2008, Kraców,

Poland.

[CI12] Marco Lanuzza, Paolo Zicari, Fabio Frustaci, Stefania Perri, Pasquale

Corsonello, “An Efficient and Low-Cost Design Methodology to Improve SRAMbased FPGA Robustness in Space and Avionics Applications”, accepted on

Proc. of the 5th International Workshop on Applied Reconfigurable Computing,

ARC2009, 16 -18 March 2009, Karlsruhe, Germany.

__________________________

Paolo Zicari