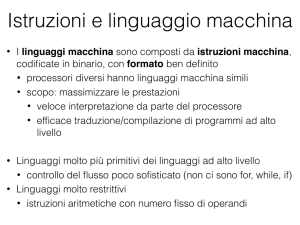

La programmazione dei calcolatori

• Linguaggio macchina (codifica con numeri binari)

– Linguaggio direttamente comprensibile dal calcolatore

– Attività di programmazione lunga e noiosa

– Facile commettere errori

L’insieme delle istruzioni

• Linguaggio assembler (o assembly)

– Rappresentazione simbolica del linguaggio macchina

– Più comprensibile del linguaggio macchina (simboli anziché

sequenze di bit)

– Tradotto dall’assemblatore in linguaggio macchina

– Dalla forma simbolica dell’istruzione macchina al

corrispondente formato binario

Architetture dei Calcolatori

(lettere A-I)

• Linguaggi ad alto livello

– Tradotti dal compilatore in assembler

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Vantaggi e svantaggi dell’assembler

Benefici dei linguaggi ad alto livello

• Vantaggio: la dipendenza dall’architettura del calcolatore

permette

• Notazione vicina al linguaggio corrente ed alla

notazione algebrica (maggiore espressività e leggibilità)

• Incremento di produttività

–

–

–

–

– Facilitano la programmazione, svincolandola dalla conoscenza

dei dettagli architetturali della macchina utilizzata

Ottimizzazione delle prestazioni (maggiore efficienza)

Programmi (potenzialmente) più compatti

Massimo sfruttamento delle potenzialità dell’hardware sottostante

Importante per

• Programmare controller di processi e macchinari (anche real-time)

• Programmazione di apparati limitati (embedded computer, dispositivi

portatili, telefonini cellulari, …)

• Indipendenza dalle caratteristiche peculiari

dell’architettura (processore) su cui il programma va

eseguito (portabilità)

• Principali svantaggi della programmazione

– Ideati non per essere compresi direttamente da macchine reali,

ma da macchine astratte, in grado di effettuare operazioni più

di alto livello rispetto alle operazioni elementari dei processori

reali

–

–

–

–

• Permettono l’uso di librerie di funzionalità già scritte

(riusabilità del codice)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

1

2

Strutture di controllo in forme limitate (minore espressività)

Necessario conoscere i dettagli dell’architettura

Mancanza di portabilità su architetture diverse

Difficoltà di comprensione, possibile lunghezza maggiore, facilità di

errore rispetto a programmi scritti in linguaggio ad alto livello

(minore produttività del programmatore)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

3

1

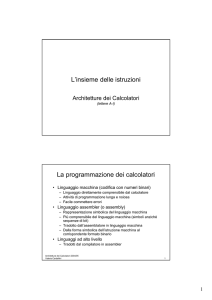

Il processo di compilazione

Compilazione

Programma sorgente

• Nella prima fase, il programma ad alto livello viene

tradotto nel linguaggio assembler utilizzando un

apposito programma detto compilatore

• Dopo la fase di compilazione, il programma scritto il

linguaggio assembler viene tradotto in linguaggio

macchina utilizzando un apposito programma detto

assemblatore (assembler)

• Spesso con il termine compilazione si indica l’intero

processo di traduzione da linguaggio ad alto livello a

linguaggio macchina (essendo l’assemblatore spesso

integrato con il compilatore)

hello.c

compilatore

Programma in linguaggio assembler hello.s

assemblatore

Programma in linguaggio

macchina (codice oggetto) hello.out

• Il programma sorgente è

scritto in un linguaggio ad

alto livello (ad es., C)

• Il codice oggetto, scritto in

linguaggio macchina, viene

memorizzato su disco

• Il caricatore (loader) carica il

programma in memoria

principale per l’esecuzione

caricatore

Programma in memoria

Architetture dei Calcolatori 2004/05

Valeria Cardellini

4

5

Il processo di compilazione (2)

Il linker

Programma sorgente

• Il linker (link editor o collegatore) ha il compito di

collegare tra loro vari moduli che compongono lo stesso

programma

compilatore

– Programma sorgente suddiviso in più file che vengono

compilati separatamente creando diversi file oggetto

– Utilizzo di funzioni di libreria

Programma in linguaggio assembler

assemblatore

• Il linker collega tra loro i file contenenti il codice oggetto

dei vari moduli che costituiscono il programma,

unendovi anche il codice delle funzioni di libreria

utilizzate, producendo un file contenente il codice

eseguibile, memorizzato su disco

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Oggetto: modulo in

linguaggio macchina

Oggetto: libreria di

funzioni

linker

6

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Eseguibile: programma

in linguaggio macchina

caricatore

Programma in memoria

7

2

Alcuni principi progettuali

I principi della progettazione

• Le istruzioni sono codificate in forma binaria

• I programmi vengono immagazzinati in memoria

insieme ai dati

• L’obiettivo è avere un set di istruzioni che

– Faciliti la costruzione della macchina

• Semplicità per il progettista

– Concetto di programma memorizzato

– In memoria istruzioni e operandi, che devono essere entrambi

trasferiti dalla memoria al processore

– Le istruzioni non sono di per sé distinguibili rispetto agli altri tipi

di informazione in memoria

– Faciliti la costruzione dei compilatori

– Ottimizzi i costi di produzione

– Permetta prestazioni elevate

• Competitività sul mercato

• Solo l’interpretazione da parte del processore stabilisce se una

data configurazione di bit è da considerarsi come un dato o

un’istruzione

• Principio della semplicità della realizzazione: semplice

significa

• Storicamente

–

–

–

–

– Architettura introdotta nel 1946 da Von Neumann

– Opposta alla architettura Hardware, in cui lo spazio di memoria

è separato per dati e programmi (impiegata in calcolatori

destinati a specifici campi applicativi, ad es. elaborazione dei

segnali)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

8

Architettura MIPS

Architetture dei Calcolatori 2004/05

Valeria Cardellini

• Le informazioni sono codificate in dati

• I dati sono rappresentati da numeri

• Esempio

– Progettata nei primi anni ’80

– Prodotta e sviluppata da MIPS Technologies negli anni ’90

(http://www.mips.com)

– Per effettuare a=b+c e a=b-c

add a, b, c sub a, b, c

• Tecnologia attualmente utilizzata da

Sony (Playstation, Playstation 2, AIBO)

Nintendo 64

Router CISCO

Stampanti, macchine fotografiche digitali, palmtop

Set-top box, DVD

TV al plasma

NB: gli operandi non

sono ancora quelli reali

• Ogni istruzioni aritmetica in MIPS esegue solo una

operazione e deve avere sempre 3 operandi

• Principio progettuale: “la semplicità favorisce la regolarità”

• Il prezzo della semplicità

Commento su ogni

– Per effettuare f = (g+h)-(i+j)

• Rappresenta un buon modello architetturale per la

didattica, perché è un’architettura semplice da

comprendere

Architetture dei Calcolatori 2004/05

Valeria Cardellini

9

Operazioni aritmetiche

• Sviluppata e progettata a Stanford (USA)

–

–

–

–

–

–

economico (semplicità = regolarità)

affidabile

di facile apprendimento ed uso (per i programmatori)

di facile traduzione (per i compilatori)

10

Architetture dei Calcolatori 2004/05

Valeria Cardellini

linea preceduto da #

add t0, g, h

# calcolo t0=g+h

add t1, i, j

# calcolo t1=i+j

sub f, t0, t1

# calcolo f=t0-t1

11

3

I registri

Gli operandi

• Il livello ISA dell’architettura MIPS richiede che

• A differenza dei linguaggi ad alto livello, gli operandi

devono provenire da speciali locazioni di memoria

all’interno del processore, dette registri

– Gli operandi delle istruzioni provengano dai registri

– Architettura di tipo load-store (o registro-registro)

• Il processore possiede un numero limitato di registri

– Nei linguaggi ad alto livello non ci si preoccupa di dover portare

i dati dalla memoria ai registri e dai registri alla memoria

– Il processore MIPS possiede 32 registri di tipo general-purpose

(GPR), ciascuno dei quali è composto da 32 bit (parola)

– Il processore MIPS possiede ulteriori 32 registri da 32 bit per le

operazioni in virgola mobile (floating point), detti FPR

• E’ compito del compilatore inserire le istruzioni necessarie

• Caratteristiche dei registri

– Elevata velocità di accesso

– In numero limitato

• Per convenzione, per denotare i registri si usano nomi

simbolici preceduti da $

• Convenzione MIPS per rappresentare i registri:

• Altro principio progettuale: “piccolo = veloce”

– Usando i registri

– $s0, $s1, … per i registri che contengono variabili

– $t0, $t1, … per i registri di uso temporaneo

– I registri possono anche essere indicati direttamente mediante il

loro numero (0, …, 31) preceduto da $ (quindi $0, …, $31)

• Si riduce il traffico con la memoria

• L’esecuzione del programma è più veloce

• Migliora la densità del codice

Architetture dei Calcolatori 2004/05

Valeria Cardellini

12

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Le operazioni e gli operandi

Il ruolo del compilatore

• Le istruzioni MIPS consentono operazioni di tipo diverso

classificabili nelle quattro categorie

• Consideriamo il seguente segmento di programma C

che utilizza 5 variabili

–

–

–

–

f = (g+h)-(i+j)

• Il compilatore associa alle variabili presenti nel

programma i registri presenti nel processore

• Il compilatore introduce due variabili temporanee (t0

e t1) che associa a due registri temporanei $t0 e $t1

# i+j

sub $s0, $t0, $t1

# f = (g+h)-(i+j)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

• Necessarie due modalità di trasferimento tra memoria e registri

del processore

– Load (caricamento) o read (lettura)

– Store (memorizzazione) o write (scrittura)

# g+h

add $t1, $s3, $s4

Istruzioni aritmetiche-logiche (es., somma, moltiplicazione, AND)

Istruzioni di trasferimento da/verso memoria

Istruzioni per il controllo del flusso del programma

Istruzioni di supporto alle procedure

• Gli operandi

– Accesso ai registri del processore

– Accesso alla memoria

– Ad esempio, alle variabili f, g, h, i e j sono associati i registri

$s0, $s1, $s2, $s3 e $s4

add $t0, $s1, $s2

13

– Uso di costanti

14

Architetture dei Calcolatori 2004/05

Valeria Cardellini

15

4

Istruzioni aritmetiche-logiche

Indirizzamento della memoria nel MIPS

• In MIPS un’istruzione aritmetico-logica possiede tre

operandi: i due registri contenenti i valori da elaborare

(registri sorgente) ed il registro contenente il risultato

(registro destinazione)

• L’ordine degli operandi è fisso: prima il registro

contenente il risultato dell’operazione e poi i due

operandi

• Esempio: istruzione add

.

.

.

12

.

.

.

$0

8

4

0

– Serve per sommare il contenuto di due registri sorgente rs e rt e

porre in rd la somma del contenuto di rs e rt

add rd, rs, rt

• Memoria come un array

monodimensionale, le cui

locazioni sono indicizzate

tramite indirizzi

• Dimensione della parola pari a

32 bit (4 byte)

• L’indirizzamento di una parola

è legato a 4 byte (vincolo

dell’allineamento)

$1

.

.

.

$31

Memoria

Processore

• Esempio: istruzione sub

• Per motivi di efficienza, è

possibile l’indirizzamento a

livello dei singoli byte che

compongono una parola

– Serve per sottrarre il contenuto di due registri sorgente rs e rt e

porre in rd la differenza del contenuto di rs e rt

sub rd, rs, rt

Architetture dei Calcolatori 2004/05

Valeria Cardellini

16

• L’accesso è generalmente con indirizzamento del byte

0

• Esistono due convenzioni per ordinare i byte all’interno di

una parola (endianess)

Allineato

– Big Endian: il byte il cui indirizzo è x…00 è nella posizione più

significativa della parola (big end)

– Little Endian: il byte il cui indirizzo è x…00 è nella posizione meno

significativa della parola (little end)

– Esempio: parola di 32 bit Indirizzo

2

1

0

7

6

5

4

0

4

0

1

2

3

4

5

6

7

Word

Big Endian

2

3

• In MIPS, allineamento della parola ad

un indirizzo multiplo di 4 (equivale a

indirizzo mod 4 = 0)

Word

18

• La mancanza di allineamento causa

un incremento della complessità

dell’hardware ed un numero maggiore

di accessi in memoria

• Terminologia delle sequenze di bit di particolare lunghezza

– Intel 80x06 è Little Endian, MIPS può essere sia Big Endian sia

Little Endian in dipendenza del valore logico su di un pin

Architetture dei Calcolatori 2004/05

Valeria Cardellini

1

– Half word (16 bit) allineata ai multipli di 2

Non allineato

Byte

Byte

17

• L’allineamento richiede che la parola inizi ad un indirizzo

multiplo della sua dimensione

– L’indirizzo di una parola corrisponde all’indirizzo di uno dei byte

all’interno della parola

3

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Allineamento dei byte e terminologia

Ordinamento dei byte

Little Endian

– Quindi gli indirizzi delle parole

differiscono di 4

– Memoria formata da 230 parole

Architetture dei Calcolatori 2004/05

Valeria Cardellini

4 bit: nibble

8 bit: byte

16 bit: half-word

32 bit: word

64 bit: double-word

19

5

Istruzione di trasferimento dati

Istruzioni load e store

• L’istruzione di load trasferisce una copia dei dati contenuti

in una specifica locazione di memoria ai registri del

processore, lasciando inalterata la parola di memoria

• MIPS fornisce due istruzioni di base per il

trasferimento di dati tra registri del processore e

memoria

– Il processore invia l’indirizzo della locazione desiderata alla

memoria e richiede un’operazione di lettura del suo contenuto

– La memoria effettua la lettura dei dati memorizzati all’indirizzo

specificato e li invia al processore

– lw (load word): per trasferire una parola di memoria in un

registro del processore

– sw (store word): per trasferire il contenuto di un registro del

processore in una parola di memoria

• L’istruzione di store trasferisce il contenuto di un registro

del processore in una specifica locazione di memoria,

sovrascrivendo il contenuto precedente di quella

locazione

• Le istruzioni lw e sw richiedono come argomento

l’indirizzo della locazione di memoria sulla quale

devono operare

– Il processore invia l’indirizzo della locazione desiderata alla

memoria insieme ai dati che vi devono essere scritti, e richiede

un’operazione di scrittura

– La memoria effettua la scrittura dei dati all’indirizzo specificato

Architetture dei Calcolatori 2004/05

Valeria Cardellini

20

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Istruzione lw

Istruzione sw

• In MIPS, l’istruzione lw ha tre argomenti

• In MIPS, l’istruzione sw ha tre argomenti, analogamente

all’istruzione lw

– Il registro destinazione in cui caricare la parola letta dalla memoria

– Una costante o spiazzamento (offset)

– Un registro base (base register) che contiene il valore dell’indirizzo

base (base address) da sommare all’offset

– Il registro sorgente, il cui contenuto deve essere scritto in memoria

– Una costante o spiazzamento (offset)

– Un registro base (base register) che contiene il valore dell’indirizzo

base (base address) da sommare all’offset

• Indirizzamento registro base (o con spiazzamento)

• Indirizzamento registro base (o con spiazzamento)

– L’indirizzo della parola di memoria da caricare nel registro è

ottenuto sommando il contenuto del registro base alla costante

– L’indirizzo della parola di memoria da sovrascrivere è ottenuto

sommando il contenuto del registro base alla costante

• Esempio

lw $s1, 100($s2)

• Esempio

sw $s1, 100($s2)

# $s1 = M[$s2+100]

– Al registro destinazione $s1 è assegnato il valore contenuto

all’indirizzo di memoria ($s2+100)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

21

# M[$s2+100] = $s1

– Alla locazione di memoria di indirizzo ($s2+100) è assegnato il

valore contenuto nel registro sorgente $s1

22

Architetture dei Calcolatori 2004/05

Valeria Cardellini

23

6

Istruzioni lw e sw: esempio di

compilazione

Array: esempio

• Codice C:

• Supponiamo che:

• Codice C: A[12] = h+A[8];

• Supponiamo che:

– A è un array di 100 word

– Le variabili g, h e i sono associate rispettivamente ai registri $s1,

$s2 e $s4

– L’indirizzo del primo elemento dell’array (base address) è

contenuto nel registro $s3

– La variabile h è associata al registro $s2

– L’indirizzo del primo elemento dell’array (base address) è

contenuto nel registro $s3

• Strutture dati (ad es. array) sono allocate in memoria

• Codice MIPS:

lw $t0, 32($s3)

• L’elemento i-esimo dell’array sarà nella locazione di

memoria di indirizzo ($s3 + 4*i)

– i è l’indice dell’array ad alto livello

– Il fattore 4 dipende dall’indirizzamento della memoria nel MIPS

A[0] $s3

A[1] $s3+4

A[2] $s3+8

.

.

.

# $t0=M[$s3+32]

add $t0, $s2, $t0

# $t0=$s2+$t0

sw $t0, 48($s3)

# M[$s3+48]=$t0

Architetture dei Calcolatori 2004/05

Valeria Cardellini

24

Architetture dei Calcolatori 2004/05

Valeria Cardellini

Array: esempio (2)

• In genere i programmi usano più variabili di quanti

sono i registri del processore

• Il compilatore cerca di mantenere le variabili usate

più frequentemente nei registri e le altre variabili in

memoria, usando istruzioni di load/store per trasferire

le variabili tra registri e memoria

– Caricamento dell’indirizzo di A[i] nel registro temporaneo $t1

# $t1=2*i

add $t1, $t1, $t1

# $t1=4*i

add $t1, $t1, $s3

# $t1=ind di A[i]

– Trasferimento di A[i] nel registro temporaneo $t0

lw $t0, 0($t1)

– Il tempo di accesso ai registri è minore del tempo di accesso

alla memoria

# $t0=A[i]

• La tecnica di mettere le variabili meno usate (o usate

successivamente) in memoria viene detta register

spilling

– Somma tra h e A[i] e risultato in g

add $s1, $s2, $t0

Architetture dei Calcolatori 2004/05

Valeria Cardellini

25

Register spilling

• Codice MIPS:

add $t1, $s4, $s4

g = h+A[i];

# g=h+A[i]

26

Architetture dei Calcolatori 2004/05

Valeria Cardellini

27

7

Formato istruzioni aritmetiche

Rappresentazione dei registri

• La rappresentazione binaria di un’istruzione assembler è

composta da 32 bit (stessa dimensione della parola di

memoria)

• Essa segue il formato di tipo R (istruzione register) per

un’istruzione logico-aritmetica tra registri

• Formato istruzioni di tipo R

shamt funct

op

rs

rt

rd

• Una convenzione per assegnare nomi dei registri e

numeri corrispondenti

• I registri $s0, $s1, …, $s7 (detti registri saved)

– Corrispondono ai registri $16, $17, …, $23

• I registri $t0, $t1, …, $t7 (detti registri temporaries)

– Corrispondono ai registri $8, $9, …, $15

6 bit

• Il registro $zero

– Corrisponde al registro $0

– Contiene sempre il valore 0

28

op

rs

rt

rd

6 bit

5 bit

5 bit

5 bit

6 bit

Valeria Cardellini

5 bit

6 bit

– All’offset sarebbe riservato un campo di 5 bit (al massimo

costanti di dimensione pari a 32)

– Si usa un formato diverso, detto di tipo I (istruzione immediate),

sempre di 32 bit

non usato

17

18

8

0

32

6 bit

5 bit

5 bit

5 bit

5 bit

6 bit

• Formato istruzioni di tipo I

op

rs

rt

6 bit

5 bit

5 bit

5 bit

address

16 bit

• Significato dei campi

000000 10001 10010 01000 00000 100000

5 bit

29

Formato istruzioni di tipo I

shamt funct

0

Architetture dei Calcolatori 2004/05

Valeria Cardellini

5 bit

• Il formato di tipo R non è adatto a rappresentare

istruzioni di tipo load/store

add $t0, $s1, $s2

5 bit

5 bit

op: opcode (codice operativo), indica il tipo di istruzione

rs: registro contenente il primo operando sorgente

rt: registro contenente il secondo operando sorgente

rd: registro destinazione contenente il risultato

shamt: shift amount (scorrimento)

funct: function, la variante specifica dell’operazione indicata nel

Architetture dei Calcolatori 2004/05

campo op

Istruzioni di tipo R: esempio

5 bit

5 bit

–

–

–

–

–

–

Architetture dei Calcolatori 2004/05

Valeria Cardellini

6 bit

5 bit

• Ai vari campi sono assegnati dei nomi mnemonici

–

–

–

–

6 bit

30

op: opcode, indica il tipo di istruzione

rs: registro base

rt: registro destinazione (load) o sorgente (store)

address: spiazzamento (±215 byte o 213 parole rispetto

all’indirizzo indicato dal registro base)

Architetture dei Calcolatori 2004/05

Valeria Cardellini

31

8

La memorizzazione del programma:

esempio

Istruzioni di tipo I: esempio

op

rs

rt

6 bit

5 bit

5 bit

address

• Codice C:

16 bit

6 bit

19

8

1000

5 bit

5 bit

16 bit

5 bit

5 bit

• $t1 è il registro base

add $t0, $s2, $t0

sw $t0, 1200($t1)

35

100011 10011 01000 0000001111101000

6 bit

Assumendo che:

• Codice MIPS: lw $t0, 1200($t1)

lw $t0, 1000($s3)

35

A[300] = h+A[300];

16 bit

Architetture dei Calcolatori 2004/05

Valeria Cardellini

32

Uso alternativo dell’indirizzamento

con spiazzamento

9

8

0

18

8

43

9

8

Architetture dei Calcolatori 2004/05

Valeria Cardellini

• $s2 corrisponde a h

1200

8

0

32

1200

Traducendo da decimale a binario si ottiene la

rappresentazione binaria del programma

33

Uso alternativo dell’indirizzamento

con spiazzamento (2)

• L’indirizzamento con spiazzamento prevede l’uso di

• La scelta di porre l’indirizzo base nel registro (anziché

nella costante)

– Indirizzo base contenuto nel registro base

– Spiazzamento specificato nell’istruzione tramite una costante

– Esempio: lw $t0, 16($s0)

– Permette di utilizzare 32 bit per indicare la locazione di inizio

• Quindi di accedere a tutta la memoria

Se $s0=100, in $t0 viene caricata la parola di memoria di indirizzo 116

• Viceversa, ponendo l’indirizzo base nella costante

• In alternativa, si può invertire l’uso del registro e della

costante

– Si possono utilizzare solo 16 bit per indicare la locazione di inizio

(vedi formato delle istruzioni di tipo I)

– Indirizzo base specificato nell’istruzione tramite una costante

– Spiazzamento contenuto nel registro indice (detto in precedenza

registro base)

– Detto indirizzamento indicizzato o indicizzazione

– Esempio: lw $t0, 100($s0)

• La scelta di porre lo spiazzamento nel registro

– Permette di scorrere l’array incrementando l’indice

– Da qui il nome di indirizzamento indicizzato e registro indice

• Se $s0=16, in $t0 viene caricata la parola di memoria di indirizzo 116

• I due usi dell’indirizzamento con spiazzamento sono

equivalenti?

Architetture dei Calcolatori 2004/05

Valeria Cardellini

34

Architetture dei Calcolatori 2004/05

Valeria Cardellini

35

9