Inverter CMOS

Lucidi del Corso di Circuiti Integrati

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

Porte Logiche

Lucidi del Corso di Circuiti Integrati

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

Porte logiche

Una porta logica (gate) è un circuito elettronico

che implementa una determinata funzione

logica (NOT, AND, OR, NAND, NOR, XOR, etc.)

Una generica porta logica avrà quindi N ingressi

e 1 uscita

Le caratteristiche in base alle quali si giudica il

comportamento di una porta logica sono:

Funzionalità

Robustezza (margini di rumore)

Area

Prestazioni (velocità, consumo di potenza)

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

3

L’inverter

La porta logica più semplice ed al

tempo stesso più significativa per

giudicare le caratteristiche di una

determinata tecnologia è l’inverter.

A

Z

Funzionalità: bisogna che il circuito implementi

veramente la funzione logica richiesta (la negazione)

Robustezza: il circuito deve essere il più possibile

immune ai disturbi

Area: il circuito deve essere il più compatto possibile

Prestazioni: tempo di propagazione fra variazioni

dell’ingresso e dell’uscita e consumo di energia devono

essere minimizzati

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

4

Rappresentazione dei segnali

V (volt)

VOH

VIH

1 (HIGH)

Logica negativa: tensioni

basse rappresentano il

valore 1, tensioni alte lo 0

VIL

VOL

Logica positiva: tensioni

alte

(HIGH)

rappresentano il valore 1,

tensioni basse (LOW)

rappresentano lo 0

0 (LOW)

10 Ottobre 2012

CI - Inverter CMOS

In pratica, viene utilizzata

solo la logica positiva

Massimo Barbaro

5

Rappresentazione dei segnali

VOH (Voltage Output High): la tensione nominale che

dovrebbe corrispondere ad un valore 1. Si vuole che sia

la più alta possibile (quindi prossima alla tensione di

alimentazione)

VIH(Voltage Input High): minima tensione che viene

interpretata ancora come valore 1

VOL(Voltage Output Low): tensione nominale che

dovrebbe corrispondere al valore 0. La si vuole più

piccola possibile quindi prossima allo zero.

VIL(Voltage Input Low): massima tensione che viene

ancora interpretata come 0

Il pedice O sta sempre per uscita (tensione nominale in uscita dalla

porta). Il pedice I sta invece per ingresso (è in ingresso ad una porta che

una tensione deve essere interpretata correttamente come alta o bassa)

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

6

Caratteristica ideale

La caratteristica ideale ingresso/uscita di un inverter (che

rappresenta la sua funzionalità) deve essere fatta in modo

che per tensioni basse in ingresso l’uscita sia alta e

viceversa.

Vout

VTC (Voltage-Transfer

Characteristic)

VOH

VOL

10 Ottobre 2012

Vin

CI - Inverter CMOS

Massimo Barbaro

7

Caratteristica reale

La caratteristica reale, ovviamente, non sarà mai squadrata.

Bisogna allora definire arbitrariamente quando l’uscita sta

cambiando valore.

Si stabilisce, convenzionalmente, che i punti di commutazione

siano quelli per cui la pendenza della curva è esattamente -1

Vout

Pendenza -1

VOH

VOL

10 Ottobre 2012

Vin

VIL

VIH

CI - Inverter CMOS

Massimo Barbaro

8

Margini di rumore

I margini di rumore misurano la robustezza di un inverter,

ossia la sua immunità ai disturbi.

0

1

I1

1

I2

Se fra l’uscita del primo inverter e l’ingresso del secondo

viene iniettato del rumore pari a V il sistema funzionerà

ancora?

Il sistema funzionerà ancora se all’ingresso di I2 ci sarà al

massimo VIL , cioè se I2 riconosce ancora l’ingresso come

basso.

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

9

Margini di rumore

Se l’ingresso Vin1 è alto (Vin1 > VIH) l’uscita del primo

inverter, se tutto fosse ideale, DOVREBBE essere bassa:

(1) Vout1 = VOL

Vout1= Vin2

Se il rumore iniettato dal primo inverter è pari a V l’uscita

cambierà e diventerà:

Vin1

(2) Vout1 = VOL + V (valore ideale + rumore)

I1

I2

Vout2

Perché il secondo inverter riconosca in ingresso comunque

un valore basso, l’uscita non deve uscire dall’intervallo

quindi:

(3) Vout1 < VIL

Sostituendo in (3) il valore di Vout1 ricavato in (2) si ottiene:

(4) VOL + V < VIL

Risolvendo (4) rispetto a V:

(5) V < VIL - VOL

10 Ottobre 2012

V < VIL - VOL

Questa è dunque la massima quantità

di rumore accettabile prima che il

segnale venga alterato (in senso

logico) e si chiama margine di rumore.

CI - Inverter CMOS

Massimo Barbaro

10

Margini di rumore

Lo steso ragionamento si potrebbe fare anche con ingresso

basso, dunque esistono due Margini di Rumore (Noise

Margins, NM), uno per i segnali alti e uno per i bassi

V (volt)

NMH = VOH - VIH

VOH

1 (HIGH)

VIH

Per massimizzare

NMH, VIH deve

diminuire

Compromesso: VIL=VIH=VDD/2

VIL

0 (LOW)

NML = VIL - VOL

VOL

10 Ottobre 2012

CI - Inverter CMOS

Per massimizzare

NML, VIL deve

aumentare

Massimo Barbaro

11

Margini di rumore

In un inverter ideale i due margini di rumore dovrebbero essere i più

grandi possibile.

Se aumento uno dei due margini, però, penalizzo necessariamente

l’altro (se aumento NML, essendo fissato l’intervallo complessivo,

deve diminuire NMH)

Per massimizzare entrambi i margini contemporanemente bisogna

allora che essi siano uguali e pari a metà della tensione massima

(tensione di alimentazione)

Questo è quello che succede nel inverter ideale, dove la VTC è

perfettamente squadrata ed il punto di commutazione (quindi anche

il punto dove la pendenza è –1) è posto al centro dell’intervallo di

tensioni disponibili

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

12

Proprietà rigenerativa

Perché si sceglie proprio un andamento come quello di

sinistra e non come la figura di destra che è comunque

invertente?

La VTC di sinistra ha la prerogativa della rigeneratività

Vout

Gate rigenerativo

VOH

VOH

Vin

VOL

10 Ottobre 2012

Vout

Gate non rigenerativo

VIL VIH

Vin

VOL

CI - Inverter CMOS

VIL VIH

Massimo Barbaro

13

Proprietà rigenerativa

Il vantaggio di questa VTC sta nel fatto che un segnale

sporcato dal rumore, attraversando livelli di logica, viene

riportato a valori nominali

X

I1

Y

Z

I2

Y

VOH

XZ

Z=Y’=(X’)’=X

La curva continua è la VTC del

primo inverter e la tratteggiata

quella del secondo (gli assi sono

invertiti per fare in modo che

l’ordinata della prima VTC coincida

con l’ascissa della seconda)

VOL

Anche se X è uno zero sporco (maggiore di VIL)

dopo 2 inversioni Z risulta uno 0 pieno

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

14

Proprietà rigenerativa

Il vantaggio di questa VTC sta nel fatto che un segnale

sporcato dal rumore, attraversando livelli di logica, viene

riportato a valori nominali

Y,Z

X

VOH

4

Attraverso I1 (da X a Y)

Attraverso I2 (da Y a Z)

6

7

2

5

8

Z (0 pulito)

10 Ottobre 2012

I2

Z

Z=Y’=(X’)’=X

3

VOL

I1

Y

1

X,Y

X (0 sporco)

CI - Inverter CMOS

Il passaggio 4 (l’arco) serve a

riportare l’uscita del primo inverter

(Y) sull’asse delle ascisse, per poi

utilizzare la stessa curva (che è

anche la VTC del secondo inverter)

Massimo Barbaro

15

Proprietà rigenerativa

Se la VTC avesse l’altro andamento un piccolo errore

verrebbe amplificato attraverso le diverse porte fino a

portare ad un risultato logicamente sbagliato

X

I1

Y

Z

I2

Y

VOH

XZ

Z=Y’=(X’)’=X

La curva continua è la VTC del

primo inverter e la tratteggiata

quella del secondo (gli assi sono

invertiti per fare in modo che

l’ordinata della prima VTC coincida

con l’ascissa della seconda)

VOL

Se X è uno zero valido (minore di VIL) dopo 2

inversioni Z tende a diventare un 1 sporco

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

16

Proprietà rigenerativa

Lo svantaggio di questa VTC sta nel fatto che un

segnale, attraversando livelli di logica, viene

ulteriormente degradato

Y,Z

X

VOH

I1

Y

I2

Z

Z=Y’=(X’)’=X

3

6

4

2

VOL

7

1

X (0 pulito)

10 Ottobre 2012

5

8

Attraverso I1 (da X a Y)

Attraverso I2 (da Y a Z)

X,Y

Z (0 sporco)

CI - Inverter CMOS

Massimo Barbaro

17

Proprietà rigenerativa

Matematicamente la proprietà rigenerativa corrisponde

ad una VTC che abbia un guadagno molto piccolo (<<1)

per tensioni di ingresso basse ed alte ed un guadagno

molto grande (>>1) per le tensioni di ingresso al centro

dell’intervallo (fra VIL e VIH)

Guadagno << 1

Vout

VOH

Guadagno >> 1

Vin

VOL

10 Ottobre 2012

VIL VIH

CI - Inverter CMOS

Massimo Barbaro

18

Soglia logica

La proprietà rigenerativa permette di definire il concetto

di soglia logica.

La soglia logica è il punto della VTC per cui Vout = Vin

Grazie alla rigenerazione, i segnali al di sotto della

soglia logica, attraverso una cascata di inverter, saranno

interpretati come 0 e quelli al di sopra come 1

Vout

Retta a pendenza unitaria

VOH

VM

Vin

VOL

10 Ottobre 2012

VM

CI - Inverter CMOS

Massimo Barbaro

19

Soglia logica

Tutto ciò che è a sinistra della soglia logica (a sinistra del punto di intersezione della

VTC con la retta a pendenza unitaria), dopo la prima inversione si sposterà a destra

della soglia logica (perché il guadagno è negativo) ed il punto di arrivo sarà più distante

da VM di quello di partenza (perché il guadagno è elevato).

Dopo la seconda inversione, dunque, il punto sarà sospinto ancora più a sinistra di

quello iniziale, diventando così uno 0.

Stesso discorso, rovesciato, per i punti che si trovano a destra della soglia logica

(diventeranno degli 1).

Y,Z

VOH

X

Retta a pendenza

unitaria

3

4

Y

I1

I2

Z

Z=Y’=(X’)’=X

6

7

VOL

Attraverso I1 (da X a Y)

Attraverso I2 (da Y a Z)

2

8

1

5

VM

X,Y

Ciò che è a sinistra di VM diventerà 0

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

20

Rigenerazione e rumore

La proprietà rigenerativa è quella che rende

intrinsecamente più precisi ed insensibili al rumore i

circuiti digitali rispetto a quelli analogici

In un sistema analogico il segnale, ad ogni stadio di

elaborazione, viene corrotto dal rumore (ogni stadio

inietta del rumore aggiuntivo)

In un sistema digitale, invece, il segnale,

nell’attraversare diversi stadi di logica viene ripulito dal

rumore

E’ per questo che copiare un CD (digitale) viene ritenuto

un reato grave ed è invece tollerato copiare una

musicassetta (analogico)

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

21

Fan-In e Fan-Out

Il Fan-In è il numero di ingressi ad una determinata porta logica (nel

caso dell’inverter è sempre 1). Determina ovviamente la complessità

della porta stessa.

Il Fan-Out è il numero di porte connesse all’uscita di una

determinata porta logica (anche nel caso dell’inverter può essere

1). In alcune tecnologie esiste un numero massimo di porte

collegabili in uscita. In tecnologia CMOS il numero di porte in uscita

influenza solo le caratteristiche dinamiche (la velocità) della porta,

non le sue caratteristiche statiche

Fan-In N

10 Ottobre 2012

N

M

Fan-Out M

CI - Inverter CMOS

Massimo Barbaro

22

Comportamento dinamico

Il comportamento dinamico dell’inverter

caratterizzato da 3 parametri fondamentali:

è

Tempo di Propagazione (tp): il tempo medio

necessario perché una transizione in ingresso si

propaghi in uscita

Tempo di salita (tr): il tempo che impiega il segnale

in uscita per andare da basso a alto

Tempo di discesa (tf): il tempo che impiega il

segnale in uscita per andare da alto a basso

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

23

Comportamento dinamico

tpHL/tpLH= tempo fra

una variazione del

50% dell’ingresso ed

una del 50% dell’uscita

Vin

50%

t

tpHL

tpLH

tr= tempo di variazione

dell’uscita dal 10% del

valore nominale alto al

90%

Vout

90%

50%

t

10%

tf

10 Ottobre 2012

tr

CI - Inverter CMOS

tp=(tpHL+tpLH)/2

tf= tempo di variazione

dal 90% del valore

nominale alto al 10%

Massimo Barbaro

24

Consumo di potenza

Il consumo di potenza è un parametro fondamentale per

misurare le caratteristiche di una tecnologia, in particolar

modo nei sistemi moderni contenenti milioni di gate,

dove la potenza (ed il conseguente riscaldamento del

dispositivo) diventano un parametro critico

In genere la potenza dissipata da una porta logica si

divide in 2 componenti:

Statica (consumata in situazione di stabilità dell’uscita)

Dinamica (consumata in commutazione dell’uscita)

La

potenza

media

T

è

definita

come:

T

Vsup ply

1

Pav isup plyVsup plydt

isup plydt

T0

T 0

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

25

Inverter CMOS

Lucidi del Corso di Circuiti Integrati

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

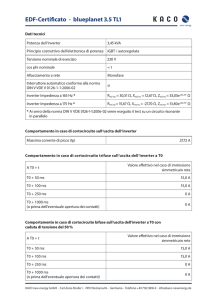

Inverter CMOS

VDD

PMOS

Vin

Tensione di alimentazione,

storicamente 5V ma ormai,

in tecnologie moderne, può

essere 3.3V, 2.5V, 1.8V,

1.2V, 0.9V

Vout

Tensione di uscita

NMOS

Tensione di

ingresso

10 Ottobre 2012

E’ chiamato CMOS, da

Complementary

MOS

perché sfrutta entrambi i tipi

di MOS (p e n)

CI - Inverter CMOS

Massimo Barbaro

27

Interruttore NMOS

VGS>VTn

E’ sicuramente

acceso se

VG=VDD

G

S

VGS<VTn

Il terminale di source è

(tipicamente) quello in basso ed

è collegato alla massa

10 Ottobre 2012

RON

CI - Inverter CMOS

E’ sicuramente

spento se VG=0

Circuito

aperto

Massimo Barbaro

28

Interruttore PMOS

VSG>|VTp|

S

RON

E’ sicuramente

acceso se VG=0

G

VSG<|VTp|

Il terminale di source è

(tipicamente) quello in alto ed è

collegato all’alimentazione (VDD)

10 Ottobre 2012

CI - Inverter CMOS

E’ sicuramente

spento se

VG=VDD

Circuito

aperto

Massimo Barbaro

29

Inverter: funzionamento di massima

Nelle resistenze non scorre VDD

corrente quindi: V=R•I=0

Vin=0

V =VDD – Vout

Vout

Vin

Vout=VDD

Vout=0

Vin=VDD

V = Vout

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

30

Inverter: funzionamento di massima

Ma perché possiamo affermare

che la corrente è esattamente

uguale a zero?

Vin=0

VDD

La corrente non può scorrere

verso massa perché lo NMOS è

interdetto.

Inoltre il carico (il circuito a valle)

sarà necessariamente un circuito

dello stesso tipo (nel caso più

semplice un altro inverter uguale,

come in figura) e perciò

presenterà in ingresso i gate di

un nmos ed un pmos che sono

circuiti aperti e NON assorbono

corrente.

10 Ottobre 2012

CI - Inverter CMOS

Vout

Massimo Barbaro

Vout2

31

Inverter: VTC

Se il comportamento di massima è giustamente quello di

un inverter come è la VTC?

E’ necessario costruirla per punti conoscendo le curve

caratteristiche dei due MOS al variare della tensione

gate-source.

Procedimento: si impone che le correnti del pmos e del

nmos siano uguali (lo sono perché non ci sono altri

possibili percorsi per la corrente). Graficamente questo

significa disegnare le caratteristiche dei due mos sullo

stesso grafico e trovare i punti di intersezione

Nel caso del NMOS: VGS=Vin , VDS=Vout

Nel caso del PMOS: VSG=VDD-Vin , VSD=VDD-Vout

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

32

Inverter: VTC

VDD

VSGp=VDD -Vin

IDp

Vin

E’ necessario mettere in relazione le

grandezze della VTC ossia ingresso (Vin)

ed uscita (Vout) con le tensioni che

determinano la corrente dei MOS ossia

VDSn (VSDp) e VGSn (VSGp).

VSDp=VDD -Vout

Vout

IDn=IDp

IDn

VGSn =Vin

10 Ottobre 2012

VDSn=Vout

CI - Inverter CMOS

Perché la corrente

non può andare

da

nessun’altra

parte

Massimo Barbaro

33

IDn , IDp

Inverter: VTC

Vin=0

PMOS

NMOS

Vin=1

Vin=0.125

Vin=0.875

Vin=0.250

Vin=0.750

Vin=0.375

Vin=0.625

Vin=0.500

Vout

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

34

Inverter: VTC

(a)

pmos triodo

(b)

Vout

pmos saturazione

La

VTC

è

quella

desiderata, ossia una VTC

che gode della proprietà

rigenerativa

(c)

nmos off (VIN<VTn)

pmos off (VIN>VDD-|VTp|)

nmos saturazione

VTn

10 Ottobre 2012

nmos triodo

(d)

CI - Inverter CMOS

(e)

Massimo Barbaro

Vin

35

Inverter VTC

La caratteristica è divisa in 5 zone:

Infatti lo NMOS è:

Pmos in triodo, nmos spento (a)

Pmos in triodo, nmos in saturazione (b)

Pmos in saturazione, nmos in saturazione (c)

Pmos in saturazione, nmos in triodo (d)

Pmos off, nmos in triodo (e)

Off se Vin<VTn

In triodo se Vout<VDSAT, in saturazione altrimenti

Infatti il PMOS è:

Off se Vin>VDD-|VTp|

In triodo se Vout>VDD-|VDSAT|, in saturazione

altrimenti

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

36

Inverter CMOS

Calcolo dei parametri statici

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

Parametri statici

Una volta ottenuta la VTC dell’inverter si

possono

ricavare

i

parametri

statici.

Banalmente:

VOH = VDD

VOL = 0

Per ricavare VIL, VIH e VM bisogna utilizzare le

equazioni dei MOS

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

38

Inverter: calcolo di VM

La soglia logica (VM) si trova imponendo che le due correnti siano uguali e

Vout=Vin. Tale condizione si verificherà sicuramente nella zona (c) dove entrambi i

MOS sono in saturazione.

VGS=Vin =VM

VSG= VDD-Vin= VDD -VM

VDSATn

knVDSATn VM VTn

2

VM

con

10 Ottobre 2012

r

=

VDSATp

k pVDSATp VDD VM VTp

2

VDSATp

VDSATn

VTn

r VDD VTp

2

2

1 r

k pVDSATp

knVDSATn

pVDSATpWp Ln vsatpWp

nVDSATnWn L p vsatnWn

CI - Inverter CMOS

Massimo Barbaro

39

Inverter: dimensionamento per VM

E’ possibile, ovviamente, ricavare, a partire dall’equazione precedente, le

dimensioni da dare ai transistor (o meglio i loro rapporti) per ottenere una precisa

VM.

Ricordando che:

W

W

kn kn ' nCOX

L n

L n

W / L p

W / L n

10 Ottobre 2012

W

W

k p k p ' p COX

L p

L p

V

k 'n VDSATn VM VTn DSATn

2

VDSATp

k ' p VDSATp VDD VM VTp

2

CI - Inverter CMOS

Massimo Barbaro

40

Soglia logica: considerazioni

La soglia logica è funzione del rapporto fra i fattori di forma del pmos e del

nmos

La condizione ideale (che rende la caratteristica simmetrica e massimizza i

margini di rumore) è quella in cui VM=VDD/2

In un circuito tipico, in cui si punta a minimizzare le dimensioni totali, le due

lunghezze saranno uguali e pari alla lunghezza minima consentita dal

processo

Tipicamente, in processi moderni:

Le tensioni di soglia di NMOS e PMOS sono uguali

La VDSATp è leggermente maggiore della VDSATn (i PMOS sono meno soggetti

alla velocity saturation)

La mobilità degli elettroni è circa 3-4 volte quella delle lacune

Se ne ricava che, per posizionare la soglia logica al centro dell’intervallo, è

richiesto (se Ln=Lp=Lmin e se le VDSAT sono molto simili):

r=1 → Wp = (μnVDSATn/μpVDSATp ) Wn = r’ Wn ≈ μn/μp Wn

Il rapporto fra le dimensioni del PMOS e del NMOS dovrebbe quindi essere 3-3.5

ma tipicamente, grosse variazione di Wp non modificano di molto la soglia logica,

un valore ottimo spesso utilizzato è quello di Wp/Lp=2Wn/Ln il che porta la soglia

vicino a VDD/2 (anche se non esattamente uguale) e mantiene le dimensioni

dell’inverter ridotte.

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

41

Margini di rumore

Per calcolare i margini di rumore è necessario trovare VIL e VIH.

Questo calcolo è complesso se si usano le definizioni standard.

Modificheremo quindi la definizione dei due valori approssimando la

VTC come una curva spezzata, costituita da 3 tratti

VIL viene ora definito come il punto di intersezione della retta

centrale (a pendenza g) con VOH e VIH come l’intersezione con VOL

Vout

VOH

VTC (Voltage-Transfer

Characteristic)

VM

Pendenza molto elevata pari a:

g

Vin

VOL

VIL VM VIH

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

42

Margini di rumore

Sappiamo già che:

VOH=VDD

VOL=0

Possiamo calcolare VIH e VIL geometricamente:

VM

VIH VM

g

VDD VM

VIL VM

g

VDD

VM

Il guadagno g è ovviamente un numero

numero negativo che deve essere calcolato.

VM- VIL VIH- VM

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

43

Calcolo di g

Per prima cosa consideriamo VIN=VOUT=VM ed uguagliamo le correnti del

NMOS e PMOS, tenendo conto della modulazione di lunghezza di

canale (qui non è trascurabile perché altrimenti il guadagno sarebbe

infinito)

I DSATn 1 nVOUT I DSATp 1 p VDD VOUT

Deriviamo membro a membro per VIN

I DSATn

VOUT

1 nVOUT n

I DSATn

VIN

VIN

I DSATp

VIN

10 Ottobre 2012

VOUT

1 p VDD VOUT p

I DSATp

VIN

CI - Inverter CMOS

Massimo Barbaro

44

Calcolo di g

Ricordiamo che

g = dVOUT/dVIN

Risolvendo per g, otteniamo:

Trascuriamo al numeratore

dipendenti dai λn e λp

i

termini

nCOX VDSATnWn / Ln 1 r

g

I DSATn (n p )

10 Ottobre 2012

1 r

VDSATn

VM VTn

(n p )

2

CI - Inverter CMOS

Massimo Barbaro

45

Dimensionamento: considerazioni

Si è visto che la condizione Wp/Lp=2Wn/Ln

rende la caratteristica simmetrica, posiziona la

soglia logica vicino al centro del range di

tensioni e massimizza, contemporaneamente, i

due margini di rumore

Cosa succede se la condizione non è verificata?

Qualitativamente si può pensare in questo

modo: quando Wp/Lp<2Wn/Ln lo NMOS è più

conduttivo (assorbe più corrente) quindi è più

difficile spegnerlo per portare l’uscita a 0 quindi

la soglia logica si sposta verso il basso.

L’opposto avviene se Wp/Lp>2Wn/Ln

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

46

Dimensionamento

Poiché l’obiettivo finale è sempre quello di avere i

dispositivi più piccoli possibili (anche perché sono più

veloci) per ottenere Wp/Lp=2Wn/Ln si agisce sulle

larghezze (W) dei due MOS imponendo per ciascuno la

lunghezza minima ottenibile per una data tecnologia

Sarà quindi

Ln=Lp=Lmin

W p= 2 W n

Nello schematico di un circuito digitale, dunque, affianco

ad un transistor si mette un numero che rappresenta la

sua W (espressa in micron) dando per scontato che la L

sia la minima possibile

In tecnologie moderne la lunghezza di canale arriva a

Lmin= 22nm.

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

47

Caratteristiche statiche: riassunto

Le tensioni nominali di uscita sono rispettivamente VDD e

0 dunque coprono il massimo range di tensioni possibile

(massimizzando i margini di rumore)

Il valore delle tensioni nominali VOH e VOL NON dipende

dalle dimensioni dei MOS (logica ratioless, ossia NON a

rapporto)

In condizioni statiche esiste sempre un percorso a bassa

impedenza verso massa o verso l’alimentazione (a

seconda che sia chiuso lo NMOS o il PMOS)

In condizioni statiche NON esiste un percorso di

corrente diretto fra alimentazione e massa

L’impedenza di ingresso è molto elevata (virtualmente

infinita) perché rappresentata dal gate di un MOS

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

48

Inverter CMOS

Calcolo dei parametri dinamici

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

Inverter: caratteristiche dinamiche

Per

trovare

le

caratteristiche dinamiche è

necessario un modello

ancora più approfondito

dei transistor.

In prima approssimazione Vin

si può pensare che la

risposta sia influenzata da

una sola capacità che

rappresenta

tutte

le

capacità parassite e di

carico connesse sul nodo

di uscita

10 Ottobre 2012

CI - Inverter CMOS

Vout

CL

Massimo Barbaro

50

Inverter: tempo di propagazione

Un’approssimazione del tempo di propagazione si può

trovare col semplice modello ad interruttore:

L’evoluzione del sistema è quella di un tipico sistema RC. La

tensione d’uscita avrà un andamento esponenziale (parte da VDD)

fino ad arrivare a 0. Il tempo di propagazione è dato dal tempo che

impiega un sistema del primo ordine a raggiungere il 50% (VDD/2)

dell’escursione

Vout

Req

CL

VDD

Vout

Vout (t ) VDD e

t

Req C L

VDD/2

t

tpHL

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

51

Inverter: tempo di propagazione

Definizione di tempo di tpHL

VDD

Vout (t pHL )

2

Andamento esponenziale

Vout (t pHL ) VDD e

t pHL

RC

t pHL

VDD

VDD e RC

2

t pHL ln(2) ReqCL 0.69ReqCL

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

52

Calcolo del tempo di propagazione

Evidentemente è necessario avere un modello

ancora più dettagliato per avere informazioni

quantitative sul comportamento dinamico.

Il primo punto da focalizzare è il valore esatto

della capacità CL di carico: da quali capacità è

costituita e quanto valgono

Il secondo punto è identificare Req e,

successivamente, sostituirla con un modello più

concreto del MOS

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

53

Calcolo del tempo di propagazione

Quali sono le condizioni di carico in cui misurare la

capacità di carico CL?

Ipotizziamo di avere come carico dell’inverter la porta

più semplice possibile (il caso migliore), ossia l’inverter

stesso

In tale situazione infatti il tempo di propagazione sarà il

migliore possibile, in tutti gli altri casi a carico maggiore

corrisponderà tp maggiore

Vout

Carico

Vin

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

54

Calcolo di tp: capacità in gioco

CGSp+CGBp

Mp

CDBp

CGp2

Mp2

Vout

Vin

CGDp+CGDn

CW

Mn

CDBn

CGSn+CGBn

10 Ottobre 2012

CI - Inverter CMOS

Mn2

CGn2

Massimo Barbaro

55

Calcolo di tp: capacità in gioco

Le capacità CGSn+CGBn e CGSp+CGBp non hanno

influenza perché si suppone che il segnale in ingresso

vari istantaneamente (ci pensa il generatore di segnale)

Le capacità CDBn e CDBp sono capacità di diffusione

La capacità CW è la capacità associata alla metallo di

interconnessione fra i due inverter (spesso trascurabile)

Le capacità CGn2 e CGp2 contengono diversi contributi

(gate/bulk, gate/drain, gate/source) ma possono essere

approssimate con la sola capacità di ossido (COXWL)

La capacità CGDn+CGDn è l’unica che non sia connessa

direttamente fra il nodo d’uscita e la massa. Può essere

trasformata in una capacità fra nodo d’uscita e massa

applicando il teorema di Miller. Contiene solo il

contributo di overlap perché il PMOS e o NMOS sono

sempre prevalentemente o in saturazione o in cutoff

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

56

Teorema di Miller

Il teorema di Miller afferma che, se fra il nodo V1 e V2

esiste il guadagno A è sempre possibile trasformare

un’ammettenza fra i due nodi con due ammettenze fra

ciascuno dei due nodi e massa di valore opportuno.

V1

Y

V1

V2

Yeq1=Y(1-A)

V2

Yeq2=Y(1-1/A)

Nel caso dell’inverter il guadagno fra il nodo di ingresso

e quello di uscita può essere considerato pari a -1 nel

punto di commutazione quindi Yeq1=Yeq2=2Y

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

57

Calcolo di CL

E’ possibile a questo punto calcolare CL come la somma

di tutti i componenti connessi al nodo di uscita

C

Valore

CGDp

2COVWp

CGDn

2COVWn

Si usa il peso 2 per via

dell’effetto Miller

CDBp Keq(CJ0ADp+CJSW0PDp)

CDBn Keq(CJ0ADn+CJSW0PDn)

CGp2

COXWpLp

CGn2

COXWnLn

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

58

Calcolo del tempo di propagazione

Per calcolare il tempo di propagazione HL facciamo

l’ipotesi che l’ingresso commuti istantaneamente da 0 a

VDD. In tale caso si può affermare che il PMOS si

spenga istantaneamente mentre lo NMOS si accende

Vout(t)

Req

CL

La corrente che scorre

attraverso lo NMOS

deve

scaricare

la

capacità CL fino a 0

ID(t)

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

59

Calcolo di RON

Per calcolare Req dobbiamo tenere conto che, in realtà,

corrente del MOS varia al variare della tensione di

uscita.

Tipicamente si calcola quindi una resistenza media,

integrando il valore della resistenza offerta (V/I) al

variare della tensione e dividendo per il range di tensioni

di interesse

V2 V

1

Req

dV

V2 V1 V1 I (V )

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

60

Calcolo di RON

Per

via della velocity-saturation il MOS si trova a lavorare, durante tutta la

commutazione (ossia per Vout che varia da VDD a VDD/2), in regione di

saturazione.

La VDSATn è infatti tipicamente più piccola di VDD/2.

La cosa non sarebbe vera nel caso classico, in quanto VGS-VTH è tipicamente

maggiore di VDD/2.

Velocity-saturated

Classico

Commutazione

Commutazione

LIN

SAT

LIN

2

VDSATn

10 Ottobre 2012

2

1

VDD/2

SAT

1

VDD/2 VGS-VTH

CI - Inverter CMOS

Massimo Barbaro

61

Calcolo di RON

1

Req

VDD / 2 VDD

2

I DSATnVDD

VDD / 2

VDD

VDD / 2

VDD

V

dV

I DSATn (1 V )

1

1 x

1 x

V (1 V )dV

3 VDD 7

Req

1 VDD

4 I DSATn 9

Analoghi calcoli e risultato si possono ovviamente ottenere per il

PMOS.

Abbiamo quindi Reqn e Reqp, la prima interviene nel fenomeno di

scarica (commutazione HL) e la seconda in quello di carica

(commutazione LH)

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

62

Calcolo del tempo di propagazione

Stessi conti si possono fare per il tempo di propagazione

nella commutazione inversa (LH). Facendo la media si

ottiene il tempo di propagazione globale:

tp

t

10 Ottobre 2012

pHL

t pLH

2

0.69CL

CI - Inverter CMOS

Reqn Reqp

Massimo Barbaro

2

63

Effetti del dimensionamento

Per ragionare sul risultato ottenuto vediamo il singolo contributo del

NMOS (analogo discorso si può fare per il PMOS), sostituendo la

formula per la corrente di saturazione e, nella formula per la resistenza,

transcurando l’effetto di modulazione di lunghezza di canale (λ) che ha

poco impatto:

3 VDD

CLVDD

t pHL 0.69CL

0.52

4 I DSATn

k 'n W / L n VDSATn VDD VTn VDSATn / 2

Da cosa dipende questo valore e come può essere diminuito?

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

64

Diminuzione di tp

Le opzioni per la diminuzione del tempo di propagazione

sono:

Aumento della tensione di alimentazione

Riduzione della CL

In realtà non è praticamente possibile agire su questo parametro

perché è fissato da motivazioni tecnologiche e di processo.

Potendo farlo, però, tp diminuirebbe perché diminuirebbe la

resistenza equivalente (per via della parte dipendente da λ che

abbiamo trascurato nell’ultima formula)

Il che significa ridurre al minimo le dimensioni dei transistor e del

carico

Aumento di Wn e (Wp)

Questa è una soluzione solo parziale perché, a parità di carico,

l’aumento delle dimensioni comporta l’aumento delle capacità

parassite e quindi l’aumento di CL (effetto di self-loading, l’inverter

carica sé stesso)

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

65

Dimensionamento: minimizzazione ritardo

Il dimensionamento effettuato per posizionare la soglia

logica a VDD/2 non coincide col dimensionamento per la

minimizzazione del ritardo intrinseco

Infatti per avere VM=VDD/2 è necessario rendere più

largo il PMOS rispetto al NMOS in modo da equalizzare

le resistenze equivalenti

Ciò comporta, però, un aumento delle dimensioni del

PMOS, ossia una aumento delle sue capacità parassite

e della capacità di gate offerta in ingresso dall’inverter di

carico (supposto sempre che sia di identico all’inverter in

esame).

Come è possibile allora minimizzare il ritardo accettando

di rinunciare ad una soglia logica perfettamente

centrata?

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

66

Dimensionamento per il ritardo

Consideriamo un PMOS β volte più largo di un NMOS a dimensione

minima:

Sappiamo che tutte le capacità

Capacità di diffusione

(complessive)

del

primo inverter (n e p)

Viceversa, la resistenza equivalente del

PMOS è inversamente proporzionale

alla sua W quindi la Reqp sarà β volte

più piccola di quella di un PMOS

minimo

Capacità

gate/drain

(overlap) del primo

inverter (n e p)

Cdp1 Cdn1

Cgp2 Cgn2

Rp

Capacità di gate

(complessive) del

secondo inverter

Sostituendo

W

W

L p

L n

parassite sono proporzionali alla

larghezza del transistor quindi le

capacità parassite del PMOS saranno β

volte più grandi di quelle del NMOS

Reqp

Capacità

dei wire

Cdn1 Cdp1 2Cgdn1 2Cgdp1 Cgn2 Cgp2 CW

[1 Cdn1 2Cgdn1 Cgn2 CW ]

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

67

Dimensionamento per il ritardo

Mettendo tutto insieme:

t pHL 0.69[1 Cdn1 2Cgdn1 Cgn2 CW ]Reqn

t pLH 0.69[1 Cdn1 2Cgdn1 Cgn2 CW ]Reqp

In

entrambe

le

commutazioni (HL e

LH) la capacità da

scaricare o caricare è

sempre la stessa,

ossia

la

capacità

parassita al nodo di

uscita.

Per ottenere il tempo di propagazione totale dobbiamo fare la media fra i due

tempi di propagazione HL e LH:

tp

t pHL t pLH

2

10 Ottobre 2012

0.69 1 Cdn1 2Cgdn1 Cgn2 CW

CI - Inverter CMOS

Massimo Barbaro

Reqn Reqp

2

68

Dimensionamento per il ritardo

Mettendo in relazione il rapporto delle

resistenze con il parametro r già visto

per il calcolo di VM (pag.14)

Mettendo in evidenza e manipolando:

Reqp 1

3 VDD

0.69

Reqp 4 I DSATp

1 Cdn1 2Cgdn1 Cgn2 CW Reqn 1

tp

2

R

eqn

Reqn 3 VDD

4 I DSATn

r'

0.345 1 Cdn1 2C gdn1 C gn2 CW Reqn 1

I DSATn nVDSATn

I DSATp pVDSATp

r'

Per ottenere il dimensionamento ottimo deriviamo rispetto a β ed uguagliamo a

zero.

Riscriviamo l’espressione in modo più comodo:

A 0.345R

r'

t p AB B C 1

10 Ottobre 2012

CI - Inverter CMOS

eqn

B Cdn1 2Cgdn1 Cgn2

C CW

Massimo Barbaro

69

Dimensionamento per il ritardo

Derivando:

t p

r' B r' A

2 B B C 0

A B

B

r ' B C

opt

2

0

opt

2

C

r ' 1

B

C

W

opt r ' 1

C

2

C

C

dn1

gdn1

gn2

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

70

Dimensionamento : considerazioni

Se la capacità dei wire (CW) è trascurabile si ottiene un rapporto

proporzionale alla radice di r’ anzi che a r’ come ottenuto dal

dimensionamento per la soglia logica (pag. 16).

Paradossalmente, quindi, a transistor più piccoli corrispondono gate

più veloci (sempre quando la capacità dei wire è trascurabile e

supponendo un carico uguale al gate stesso)

La ragione è da ricercare nel fatto che, alla diminuzione di uno dei

due tempi di propagazione (quello LH) dovuto all’aumento delle

dimensioni del PMOS corrisponde un aumento del tempo HL dovuto

al fatto che lo NMOS, a parità di dimensioni, deve scaricare una

capacità più grande

Il valore di β trovato corrisponde al punto in cui la media dei due

fenomeni è minima il che NON corrisponde al punto in cui i due

ritardi sono uguali (come sarebbe richiesto dall’avere soglia logica

pari a VDD/2)

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

71

Ritardo: riassunto

Il ritardo di inverter si minimizza agendo sulle

dimensioni (minimizzando la capacità parassita)

Il dimensionamento per ritardo ottimo non

corrisponde al dimensionamento per soglia

logica ottima

All’aumentare delle dimensioni il gate si carica

da solo (self-loading) e le prestazioni non

migliorano più

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

72

Inverter CMOS

Consumo di potenza

Università di Cagliari

Dipartimento di Ingegneria Elettrica ed Elettronica

Laboratorio di Elettronica (EOLAB)

Potenza dissipata

Le componenti del consumo di potenza sono 3:

Potenza statica: è quella dissipata quando l’inverter

ha ingresso costante, in condizioni di stabilità

Potenza dinamica dovuta a CL: è la potenza

consumata in commutazione, dovuta al fatto che in

corrispondenza di una variazione d’ingresso deve

avvenire una variazione dell’uscita che comporta la

carica e la scarica di CL

Potenza dinamica dovuta a correnti di cortocircuito: è la potenza che si dissipa in

commutazione quando, temporaneamente, si

creano percorsi conduttivi diretti fra alimentazione e

massa

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

74

Potenza dinamica su CL

Ogni volta che CL viene caricata in una commutazione

LH una certa quantità di energia deve essere prelevata

dall’alimentazione.

Parte di questa energia viene immagazzinata su CL e

parte dissipata nel PMOS

Se la transizione dell’ingresso è istantanea, lo NMOS

si spegne istantaneamente ed il PMOS si accende

(inizialmente in saturazione)

Il PMOS carica CL fino al valore di VDD con la sua

corrente di drain che varia al variare di Vout

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

75

Potenza dinamica su CL

dVout (t )

iVDD (t ) CL

dt

Vin=0

Vout

CL

Energia fornita dall’alimentazione

EVDD 0 iVDD (t )VDD dt

Non c’è percorso diretto

verso massa perché lo

NMOS è off

10 Ottobre 2012

Energia assorbita da CL

ECL 0 iVDD (t )Vout (t )dt

CI - Inverter CMOS

Massimo Barbaro

76

Energia erogata dall’alimentazione

L’energia totale erogata dall’alimentazione per

caricare completamente CL è:

dVout

EVDD CLVDD 0

dt

dt

VDD

2

CLVDD 0 dVout CLVDD

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

77

Energia assorbita da CL

L’energia totale assorbita da CL è pari alla metà

dell’energia erogata dall’alimentazione, questo

perché l’altra metà viene dissipata sul PMOS

dV

E C

V dt

dt

CV

C V dV

2

CL

out

L 0

out

VDD

L 0

10 Ottobre 2012

L

out

2

DD

out

CI - Inverter CMOS

Massimo Barbaro

78

Transizione HL

Nella commutazione opposta (HL) il PMOS si

spegne e CL si scarica attraverso lo NMOS.

In questa situazione l’alimentazione non eroga

energia (perché non eroga corrente).

L’energia che era stata precedentemente

immagazzinata su CL viene dissipata sul NMOS

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

79

Potenza dinamica dissipata

L’energia totale dissipata in una doppia

transizione (L→H→L) è data dalla somma di

quella dissipata sul PMOS e sul NMOS.

Tale energia è indipendente dalla resistenza

dei MOS e dalle loro dimensioni

La potenza dissipata si ottiene dividendo

l’energia per il tempo impiegato dalla doppia

transizione (ossia moltiplicando per la frequenza

di commutazione dell’inverter)

Pdyn = CLVDD2/T = CLVDD2 f0→1

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

80

Potenza dissipata: considerazioni

La frequenza f0→1 per cui viene moltiplicata l’energia non è

necessariamente uguale alla frequenza di funzionamento del

sistema

Non è infatti vero che ogni singolo gate commuti alla frequenza del

sistema (non tutti i gate commutano contemporaneamente)

Questo fa sì che la frequenza effettiva da usare nella formula sia da

pesare con un coefficiente moltiplicativo che deriva da

considerazioni statistiche sulla probabilità di commutazione di vari

gate

La formula ci dà il caso peggiore (worst case)

Per valutare il consumo reale bisogna avere delle statistiche sul

numero di transizioni dell’uscita, che dipendono dalla specifica

operazione svolta dal circuito (switching-activity).

Si ottiene che, se la probabilità di avere una transizione è pari a

P01:

Pdyn = CLVDD2 P0→1f = Ceff VDD2 f

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

81

Potenza dinamica da cortocircuito

In realtà l’ingresso non potrà mai variare instantaneamente fra 0 e

VDD (o VDD e 0) ma assumerà tutto i valori intermedi.

Mentre l’ingresso compie la sua commutazione, in un certo range di

tensioni sia il PMOS che lo NMOS sono accesi e si stabilisce quindi

un cortocircuito (temporaneo) fra alimentazione e massa.

Questo avviene quando l’ingresso è:

Vtn<Vin<VDD-|Vtp|

Vin

IShort

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

82

Potenza dinamica da cortocircuito

Al variare della tensione di ingresso può capitare che i due

dispositivi siano accesi contemporaneamente dando origine ad una

corrente di cortocircuito (Ishort) che dissipa potenza

Vin

Ipeak

Ishort

tf

tr

Edp=VDDIpeak(tr+tf)/2

Pdp=Edp f0→1= f0→1VDDIpeak(tr+tf)/2

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

83

Potenza statica

La dissipazione di potenza statica è molto piccola ed è legata solo a

due fenomeni:

La corrente di leakage attraverso i diodi parassiti

La corrente di sottosoglia dei MOS.

Corrente di sottosoglia, dovuta al

fatto che, in realtà, il transistor non

si

spegne

brutalmente

ma

conduce anche per VGS inferiori

alla soglia.

Tanto più corto è il dispositivo,

tanto minore è la tensione di soglia

e maggiore la corrente di

sottosoglia.

10 Ottobre 2012

CI - Inverter CMOS

n+

n+

Diodi parassiti (formati dalle

giunzioni pn fra le sacche n+

di source e drain ed il

substrato).

Analoghe

strutture esistono nel PMOS.

Massimo Barbaro

84

Potenza statica

Il vantaggio della tecnologia CMOS rispetto a tutte le altre è proprio

il fatto di avere una dissipazione statica praticamente trascurabile

Nelle tecnologia moderne (deep-submicron), dai 90nm in giù, la

corrente di sottosoglia tende a dominare il fenomeno.

Diodi parassiti (formati dalle

sacche n+ e dal body e dalle

sacche p+ e dalla nwell)

ID

Corrente di

sottosoglia

10 Ottobre 2012

IS

Ileakage=IS+ID

Pstat=IleakageVDD

CI - Inverter CMOS

Massimo Barbaro

85

Potenza dissipata

La potenza dissipata totale è data dalla somma

delle 3 componenti:

P = Pstat+Pdyn+Pdp =

= IleakageVDD+ [CLVDD2 + VDDIpeak(tr+tf)/2]f0→1

In genere il contributo di Pdyn è quello dominante

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

86

Prodotto Potenza/Ritardo (PDP)

Un parametro fondamentale di una tecnologia è il prodotto potenza/ritardo

(Power Delay Product), ossia il prodotto fra massima frequenza di

funzionamento e ritardo.

Nel caso CMOS si può ricavare dalla formula della potenza, notando che la

massima frequenza di funzionamento dell’inverter è pari al doppio del tempo

di propagazione.

Infatti per ogni colpo di clock devono essere compiute due commutazioni (HL

e LH) (per frequenze maggiori il segnale non riesce a propagarsi prima che

l’ingresso cambi nuovamente), dunque, trascurando i contributi di statica e di

cortociruito:

PDP = Pdyntp = CLVDD2 fmax tp = CLVDD2 (1/2tp) tp= CLVDD2/2

Il termine PDP dipende solo da alimentazione e CL che vanno quindi

minimizzate contemporaneamente.

Il PDP è una misura dell’energia mediamente consumata per una transizione.

Come metrica ha però un difetto: mediando l’energia sul tempo di

elaborazione può essere resa bassa semplicemente riducendo la frequenza

di operazione, ossia impiegando più tempo per fare la stessa operazione (a

scapito delle prestazioni effettive).

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

87

Prodotto Energia/Ritardo (EDP)

Una metrica più efficace è rappresentata dal prodotto energia/ritardo

(Energy Delay Product)

Lo EDP misura infatti l’energia spesa a parità di prestazioni (a parità

di velocità di funzionamento).

Si può facilmente ricavare l’EDP di un inverter CMOS dal suo PDP

moltiplicando ulteriormente per il tempo di propagazione:

EDP = PDP tp = CLVDD2/2 tp

Si vede ora che, all’aumentare della tensione di alimentazione

aumentano le prestazioni (diminuisce tp) ma aumenta anche l’energia

dissipata (quadraticamente).

Al contrario, il PDP migliora indefinitamente al diminuire della VDD

(ovviamente a scapito delle velocità).

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

88

Potenza: riassunto

La dissipazione di potenza statica è praticamente nulla

La dissipazione di potenza dinamica è proporzionale al

quadrato della tensione di alimentazione ed alla

frequenza di commutazione

In commutazione ci possono essere cortocircuiti

temporanei fra alimentazione e massa

Il PDP dipende solo da VDD e da CL

Lo EDP dipende da VDD e da CL e dal tempo di

propagazione

10 Ottobre 2012

CI - Inverter CMOS

Massimo Barbaro

89