Circuiti Sincroni e Asincroni

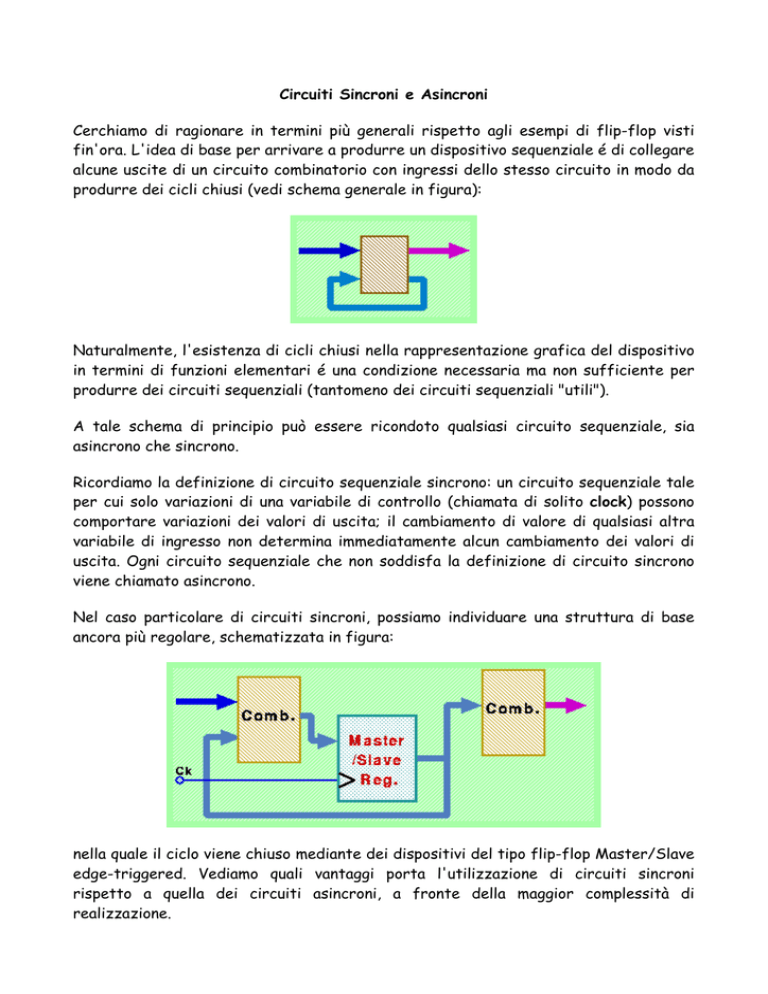

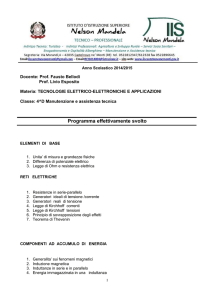

Cerchiamo di ragionare in termini più generali rispetto agli esempi di flip-flop visti

fin'ora. L'idea di base per arrivare a produrre un dispositivo sequenziale é di collegare

alcune uscite di un circuito combinatorio con ingressi dello stesso circuito in modo da

produrre dei cicli chiusi (vedi schema generale in figura):

Naturalmente, l'esistenza di cicli chiusi nella rappresentazione grafica del dispositivo

in termini di funzioni elementari é una condizione necessaria ma non sufficiente per

produrre dei circuiti sequenziali (tantomeno dei circuiti sequenziali "utili").

A tale schema di principio può essere ricondoto qualsiasi circuito sequenziale, sia

asincrono che sincrono.

Ricordiamo la definizione di circuito sequenziale sincrono: un circuito sequenziale tale

per cui solo variazioni di una variabile di controllo (chiamata di solito clock) possono

comportare variazioni dei valori di uscita; il cambiamento di valore di qualsiasi altra

variabile di ingresso non determina immediatamente alcun cambiamento dei valori di

uscita. Ogni circuito sequenziale che non soddisfa la definizione di circuito sincrono

viene chiamato asincrono.

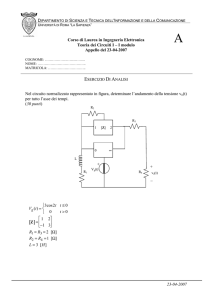

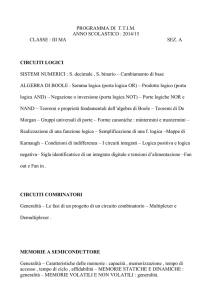

Nel caso particolare di circuiti sincroni, possiamo individuare una struttura di base

ancora più regolare, schematizzata in figura:

nella quale il ciclo viene chiuso mediante dei dispositivi del tipo flip-flop Master/Slave

edge-triggered. Vediamo quali vantaggi porta l'utilizzazione di circuiti sincroni

rispetto a quella dei circuiti asincroni, a fronte della maggior complessità di

realizzazione.

Alee e temporizzazione

Consideriamo l'esempio di circuito sequenziale asincrono illustrato in figura:

Supponiamo di voler determinare il valore dell'uscita u dopo aver applicato sugli

ingressi la seguente sequenza di combinazioni di valori:

config

d=

c=

b=

a=

1

1

1

1

1

2

0

1

1

1

3

0

0

1

1

Dalla tavola di verità delle funzioni combinatorie e dalla descrizione del flip-flop

Set/Reset determiniamo che la prima configurazione memorizza il valore u=1. La

seconda configurazione consente al flip-flop di mantenere il valore precedentemente

memorizzato, così come la terza. Quindi possiamo dedurre che il valore prodotto in

uscita dall'applicazione della sequenza di ingressi considerata sia u=1.

Non soddisfatti di questa risposta, proviamo ora a considerare alcuni dettagli

realizzativi del dispositivo Multiplexer. Supponendo di considerare la realizzazione

minimale del multiplexer vista in precedenza mediante un NOT, due AND ed un OR,

possiamo ipotizzare che ciascuna funzione logica elementare sia caratterizzata da un

ritardo di una unità di tempo per produrre il corretto valore di uscita a fronte di una

variazione dei valori di ingresso. Il passaggio dalla seconda alla terza configurazione

della sequenza può quindi essere decomposto in passi elementari di durata pari ad una

unità di tempo:

1. appena cambiata la configurazione di ingresso nessuna funzione cambia uscita:

l'AND in alto e l'OR mantengono il valore 1, l'AND in basso ed il NOT

mantengono il valore 0;

2. dopo una unità di tempo l'AND in alto passa al valore 0 (come dettato dalla sua

tavola di verità) e il NOT passa al valore 1, mentre l'OR mantiene 1 e l'AND in

basso mantiene 0;

3. dopo due unità di tempo l'OR passa al valore 0, mentre l'AND in basso passa al

valore 1 e NOT ed AND in alto mantengono il valore raggiunto in precedenza;

4. dopo tre unità di tempo, l'OR torna nuovamente a 1, mentre le altre funzioni del

multiplexer mantengono il valore del passo precedente.

Da questa analisi più dettagliata legata alle temporizzazioni dei dispositivi costituenti

il Multiplexer, vediamo quindi che questo nel transitorio di passaggio dalla seconda

configurazione di ingresso alla terza (entrambe con valore di uscita 1 per il

Multiplexer) può generare per un breve tempo una situazione intermedia, detta alea

di commutazione, con uscita 0. Tale alea di commutazione del multiplexer può

determinare la commutazione del flip-flop al valore u=0.

Questo esempio ci mostra come possa essere difficile prevedere il risultato in uscita

di un circuito sequenziale asincrono a seguito di variazioni delle configurazioni in

ingresso. In particolare vediamo come anche alee molto brevi possono determinare la

commutazione permanente di un flip-flop rispetto al valore di uscita previsto

basandosi sulla specifica del circuito combinatorio data sotto forma di tavola di verità

(prescindendo quindi dalle temporizzazioni delle funzioni).

Il problema di "imprevisti" dovuti ad alee di commutazione può essere completamente

eliminato in circuiti di tipo sequenziale sincrono mediante un'opportuna utilizzazione

della variabile di controllo clock.

Variabile Clock in circuiti sincroni

L'uso di dispositivi Master/Slave consente di far variare i valori di ingresso al flipflop senza per questo alterare il valore delle uscite, fin quando non venga dato un

apposito impulso alla variabile di controllo clock. Scegliendo un periodo di variazione

per la variabile clock grande rispetto al tempo di assestamento dei valori in uscita del

circuito combinatorio a seguito di variazioni dei valori di ingresso, si può quindi ovviare

in modo semplice al problema delle eventuali alee di commutazione: queste saranno

esaurite nel momento in cui, tramite variazioni della variabile clock, comandiamo il

passaggio dallo stato corrente allo stato successivo.

La progettazione di un circuito sincrono può quindi essere basata sulla specifica del

comportamento di un circuito combinatorio basato sulla tavola di verità, senza

necessità di una analisi raffinata del comportamento in funzione del tempo. Le uscite

dei dispositivi Master/Slave tengono fisso il valore dello stato corrente, mentre gli

ingressi di tali dispositivi predispongono il calcolo dello stato successivo. Il passaggio

dallo stato corrente allo stato successivo avviene in modo "istantaneo" e simultaneo

per tutti i flip-flop Master/Slave inclusi nel circuito sincrono a seguito di un impulso

della variabile di controllo clock.

Principali Circuiti Sincroni

I circuiti sequenziali sincroni sono, insieme ai circuiti combinatori, i "mattoni"

elementari piu' usati per definire la microarchitettura di un sistema di calcolo

moderno. Data la loro potenziale insensibilità alle alee di commutazione dei circuiti

combinatori, la loro utilizzazione consente di arrivare a progettare sistemi complessi

in modo estremamente semplice e modulare, tenendo conto solo della funzione tra

ingresso ed uscita dei dispositivi (e verificando semplici disuguaglianze per quanto

riguarda i tempi di assestamento dei valori in ingresso ed in uscita). Normalmente i

circuiti sequenziali sincroni vengono classificati in "registri" (contenenti

rappresentazioni binarie di dati su uno o più bit) caratterizzati da diverse modalità di

manipolazione dei dati.