La Comunicazione N.R.&N.

a), b)

Stefano Penna

,

a)

Silvia Di Bartolo ,

a)

Vincenzo Attanasio ,

b)

Akira Otomo ,

c)

Leonardo Mattiello

a)

Istituto Superiore delle

Comunicazioni e delle

Tecnologie

dell'Informazione (ISCOM)

b)

Advanced ICT Research

Institute - National

Institute of Information

and Communications

Technology (NICT), Kobe

(Giappone)

c) Dipartimento di Scienze

di Base e Applicate per

l`Ingegneria - Sapienza

Università di Roma

Tecnologie di fotonica integrata:

dispositivi e applicazioni

Integrated photonic technologies: devices and applications

Sommario: L’affermazione recente della fotonica in silicio e più in

generale della fotonica integrata sta introducendo una nuova

tecnologia di base di dispositivi per applicazioni ad ampio spettro, dalla

sensoristica all’ICT alle applicazioni più strettamente datacom.

Attraverso gli strumenti di finanziamento del settimo programma

quadro, negli ultimi anni l’Europa ha sviluppato diverse piattaforme

tecnologiche per la realizzazione di dispositivi fotonici integrati,

introducendo nuovi modelli di business basati sulla condivisione delle

infrastrutture di fabbricazione tra più partner per consentire la

sostenibilità economica dello sviluppo tecnologico. Il contributo descrive

i progressi ottenuti nello sviluppo delle tecnologie fotoniche integrate,

focalizzandosi sui recenti risultati della tecnologia ibrida SilicioOrganica (SOH), e fornisce una panoramica dei principali partenariati.

Abstract: The recent success of Silicon Photonics and more

generally of the integrated photonic technologies led to a new device

concept for a wide range of applications, from sensors to ICT and

datacom. Through the funding of the Framework Programmes (FP), the

European Union supported the constitution of more technology

platforms aimed at the fabrication of integrated photonic devices,

easing the introduction of a new business model based on shared

manufacturing facilities among more partners to enable the economical

and financial sustainability of the technological development. The

following contribution reports the main achievements of the different

integrated photonic technologies, focusing on the recent results of the

Silicon Organic Hybrid (SOH) technology, and provides an overlook of

the main partnerships.

1. Introduzione

L'ultima decade ha visto profondi mutamenti nel mondo

industriale e tecnologico legato alla fotonica, da un lato con

l’esplosione della bolla delle aziende “dot-com”, che dopo una crescita

vorticosa ha subito una battuta di arresto nei primi anni del duemila a

favore dell'economia di servizi basata sullo sfruttamento delle

potenzialità della banda larga, come nel caso degli operatori OTT (Over

The Top), dall'altro dai raggiunti limiti fisici e tecnologici del mondo

101

S.Penna, S.Di Bartolo,V.Attanasio, A.Otomo, L. Mattiello

della microelettronica che proprio nella fotonica vedono una possibile

soluzione, introducendo pertanto nuove prospettive di applicazione. Il

risultato di questo processo di cambiamento, ancora in essere, e` nella

definizione di Key Enabling Technology che l'Europa ha dato della

fotonica all'interno del programma quadro Horizon2020, intendendo

una tecnologia abilitante per l'innovazione in ambiti che spaziano oltre

le pure tecnologie dell'informazione e della comunicazione (ICT), dalla

sensoristica fino alla microelettronica e alle comunicazioni dati

(datacom), che nell'attuale era dei data center costituiscono forse la

principale area di sviluppo.

I principali vantaggi delle tecnologie fotoniche derivano dalle

peculiarità legate alla radiazione ottica, su tutte la larghezza della

banda potenzialmente disponibile (centinaia di THz), fino a quattro

ordini di grandezza superiore alla banda attualmente disponibile con le

tecnologie elettroniche (decine di GHz). A questo proposito la Legge di

Moore, una legge empirica del 1965 inizialmente mirata ad anticipare i

trend di crescita delle prestazioni dei processori nel solo decennio

seguente e dimostrandosi invece valida fino ad oggi, predice

l'incremento della frequenza di clock dei processori e la conseguente

riduzione di dimensioni dei transistor con un passo che si stima

raggiungerà i limiti fisici entro il 2020 [1]. Tali limiti sono legati appunto

al dominio elettrico dei segnali, per i quali una miniaturizzazione delle

connessioni elettriche all'interno de e tra chip porta ad un incremento

della potenza dissipata e soprattutto a valori di resistività maggiori che

limitano la banda disponibile e quindi la velocità di elaborazione del

dispositivo finale.

Un'ulteriore considerazione riguarda l'aspetto energetico. Come

anticipato, negli attuali processori basati su tecnologia elettronica

CMOS l'incremento della velocità porta ad un aumento della potenza

dissipata, in particolar modo nelle interconnessioni tra transistor, con

un tetto massimo di potenza dissipabile pari a 200W per un'area di 2

cm2. Al raggiungimento di questo limite le attuali interconnessioni

elettriche contribuiscono sensibilmente, con una crescita più che

lineare all'aumento della frequenza di clock. Questo aspetto ha portato

dagli anni 2000 all'introduzione del concetto di processori multi-core,

basati su calcolo parallelo [1][2].

Da quanto sopra riportato ne consegue anche un aspetto

meramente energetico, con la necessità di disporre di tecnologie a

maggiore efficienza ovvero dal minore consumo, a parità di prestazioni

garantite. Da questo punto di vista l'impiego di concetti legati alla

fotonica ed in particolare mutuati dalle reti ottiche, come la

multiplazione a divisione di lunghezza d'onda (Wavelength, Division

Multiplexing, WDM), permettono di garantire un intrinseco

parallelismo, oltre a larga banda e quindi alta velocità di elaborazione,

sostanziale immunità dalle perdite capacitive e resistive tipiche delle

connessioni metalliche e interferenza tra canali adiacenti

comparabilmente nulla [1][2]. Per meglio comprendere l'impatto di

102

La Comunicazione N.R.& N.

Tecnologie di fotonica integrata: dispositivi e applicazioni

Integrated photonic technologies: devices and applications

queste caratteristiche si possono citare i dati forniti da Google ed

Amazon relativamente agli effetti che ha sul proprio fatturato il

parametro di latenza, ovvero il tempo richiesto dalla rete internet per

fornire all'utente le informazioni da lui richieste, che e` direttamente

legato alla velocità di connessione. In particolare, per Google un

incremento di mezzo secondo sul tempo medio di caricamento di una

pagina di ricerca e` causa del 20% di riduzione del traffico di ricerca,

mentre per Amazon 100 ms di aumento nel tempo di caricamento di

una pagina portano ad un calo di vendite dell'1%. E` evidente come per

queste aziende la latenza, dominata in particolare dalla velocità di

trasferimento dati all'interno dei propri data centers, rappresenti il

fulcro abilitante della generazione di profitto. Questo aspetto

rappresenta il principale traino per lo sviluppo di interconnessioni

interamente ottiche anche per infrastrutture di rete locale come i data

centers, che richiedono di fianco alle prestazioni tipiche della banda

ottica un livello di integrazione e miniaturizzazione molto elevato per

trovare spazio all’interno delle server farm.

Lo sfruttamento della fotonica in contesti attualmente dominati

dalla microelettronica, con dispositivi fotonici in grado di garantire

velocità elevate con minori consumi energetici, e` possibile unendo il

concetto di dispositivo ottico al concetto di dispositivo integrato, con la

definizione pertanto di circuito fotonico integrato o PIC (Photonic

Integrated Circuit), ovvero un chip che è in grado di elaborare al suo

interno l’informazione come segnale ottico implementando su un unico

substrato o piattaforma le principali funzioni ottiche, quali ad esempio

generazione di luce, ricezione, modulazione e filtro. Si deve comunque

evidenziare come un chip interamente ottico abbia poco senso ai fini

pratici, dal momento che l’informazione viene comunque generata e

gestita come segnale elettrico, pertanto un PIC deve soddisfare anche

la compatibilità con le tecnologie elettroniche, su tutte la CMOS, per

potersi interfacciare in modo adeguato con costi contenuti,

possibilmente condividendo anche la stessa piattaforma e

auguratamente anche lo stesso flusso di processo di fabbricazione.

Per questo motivo negli ultimi anni si e` imposta sempre più la

Silicon Photonics [3], ad indicare la classe di dispositivi fotonici

compatibili con il Silicio. Tale affermazione e` legata ad aspetti di

carattere economico, considerando i forti investimenti in tecnologia

richiesti da un impianto di produzione di chip, nell'ordine di qualche

miliardo di dollari, che costituiscono una pesante barriera

all'introduzione di tecnologie alternative su scala industriale.

Storicamente ed attualmente le linee di produzione di chip sono

state e sono tuttora dominate dalla tecnologia CMOS basata su Silicio

ed il basso costo dei dispositivi prodotti, a fronte dell'ingente costo

degli impianti di fabbricazione, e` assicurato dagli alti volumi di

produzione e di mercato che consentono di ripartire in modo

sostenibile i costi di investimento sugli impianti e lo sviluppo dei

processi [4]. Ad oggi, gli sforzi delle aziende e degli enti di ricerca del

103

S.Penna, S.Di Bartolo,V.Attanasio, A.Otomo, L. Mattiello

settore concentrati sullo sviluppo di dispositivi fotonici compatibili o

integrabili su Silicio ha consentito di dimostrare separatamente tutte le

principali funzionalità ottiche (generazione [5][6], rivelazione [7],

modulazione [8]). Tuttavia la sfida maggiore è rappresentata proprio

dall’integrazione di queste funzioni in un unico sistema che riproduca a

livello di circuito nanometrico una rete ottica, da cui la definizione di

on-chip networks.

L'elemento chiave di un PIC, che rappresenta anche la principale

differenza rispetto ad un chip prettamente elettronico, e` costituito

dall'elemento di connessione: la guida d'onda. Se nei chip elettronici le

frequenze specifiche dello spettro elettromagnetico consentono un

trasferimento della radiazione tramite connessioni metalliche con

dimensioni nell'ordine delle decine di nanometri (1 nm = 10-9 m), nei

PIC la radiazione ottica deve essere confinata all'interno di guide

d'onda che hanno dimensioni caratteristiche confrontabili con le

lunghezze d'onda della radiazione stessa, nell’ordine di 100 nm – 1 µm.

Questo rappresenta un primo limite dei PIC, ovvero l’impossibilità

attualmente di portare il fattore di forma alla stessa scala attuale dei

transistor CMOS, introducendo quindi un limite alla densita` massima

di chip raggiungibile. Nella Silicon Photonics, l'impiego del Silicio come

elemento guidante della luce permette di ottenere strutture altamente

confinanti, quindi con basse perdite ottiche, legate all'alto contrasto di

indice di rifrazione tra il nucleo, costituito di Silicio che ha indice di

rifrazione nel vicino infrarosso pari a n=3.48, ed il substrato e, quando

presente, il mantello (cladding), che sono tipicamente costituiti di

materiali come Ossidi o altri dielettrici caratterizzati da indici di

rifrazione con valori minori, compresi tra 1.44 e 2. Il contrasto d'indice

che ne risulta si attesta intorno al 40%. Per avere un'idea di raffronto,

nelle fibre ottiche in vetro, l’esempio più noto di guida d’onda ottica, il

contrasto d'indice e` inferiore all’1%.

Questa caratteristica dei PIC in Silicio consente di ottenere campi

ottici estremamente confinati e pertanto rende possibile la

realizzazione di dispositivi con minore fattore di forma e maggiore

efficienza, come nel caso dei modulatori di fase, in cui le prestazioni e

le dimensioni delle sezioni attive dipendono dal fattore di

confinamento della radiazione ottica. Consentono inoltre di ridurre le

dimensioni caratteristiche delle guide al di sotto di 1 µm, a fronte

tuttavia di un incremento delle perdite ottiche.

2. Tecnologie

Come anticipato, esistono differenti tipologie di piattaforme di

integrazione fotonica, ognuna con una una sua particolare peculiarietà

che ne rende possibile l’impiego per specifiche applicazioni. Tale

diversità riflette la principale differenza tra l’elettronica integrata e la

fotonica integrata, ovvero mentre l’elettronica integrata è chiaramente

dominata dal Silicio, la fotonica integrata vede invece un’etereogeneità

104

La Comunicazione N.R.& N.

Tecnologie di fotonica integrata: dispositivi e applicazioni

Integrated photonic technologies: devices and applications

di materiali impiegati per la realizzazione delle diverse funzionalità

ottiche: semiconduttori elementari, come Silicio e Germanio, o

composti, come Fosfuro d’Indio (InP) ed Arseniuro di Gallio (GaAs),

materiali dielettrici, come Diossido di Silicio (SiO 2 ) o Nitruri di Silicio

(Si 3 N x ), polimeri e cristalli non lineari come il Niobato di Litio (LiNbO 3 ).

Questa eterogeneità di materiali è stata la principale barriera allo

sviluppo dei PIC, ma come vedremo nel seguito oggi questa

problematica viene affrontata con soluzioni promettenti e soprattutto

con un sensibile cambio di appoccio allo sviluppo.

La tecnologia fotonica integrata più compatibile con la tecnologia

CMOS è la Silicon Photonics, che consente di ottenere dispositivi

sostanzialmente

passivi,

privi

cioè

della

funzione

di

generazione/amplificazione ottica, a fronte però di una più semplice

integrazione con gli esistenti circuiti elettronici e di ottime prestazioni;

la tecnologia basata su Fosfuro d’Indio, un semiconduttore del gruppo

III-V, è invece l’unica per ora in grado di consentire la realizzazione di

dispositivi attivi su chip grazie all’emissione dell’InP nelle lunghezze

d’onda della banda C (1530 nm – 1565 nm), a fronte però di perdite

ottiche su guida d’onda superiori di un ordine di grandezza al Silicio; da

ultimo, la piattaforma basata su Nitruro di Silicio (Si 3 N 4 ) permette di

ottenere guide d’onda con bassissime perdite ottiche su un ampio

intervallo di lunghezze d’onda, dal visibile all’infrarosso, aggiungendo

anche funzionalità termo-ottiche.

2.1 Silicon Photonics

Quando si parla di Silicon Photonics, generalmente ci si riferisce a

dispositivi basati su substrato di Silicon On Insulator (SOI), che in uno

dei processi di fabbricazione più tipici è costituito da un wafer di Silicio,

detto handle, al di sopra del quale viene “attaccato” (bonding) uno

strato di Ossido di Silicio, l’isolante anche detto BOX (Buried Oxide),

che sulla superficie superiore presenta un ulteriore film sottile di Silicio,

detto seed [9]. Il Silicio seed ha la funzione tipicamente di core nelle

guide d’onda mentre il BOX funge da mantello, oltre che da substrato,

consentendo quindi una propagazione ottica con perdite ridotte. Come

accennato in precedenza, l’elevato contrasto d’indice del Silicio rispetto

al BOX consente di realizzare strutture con dimensioni caratteristiche

intorno a 250 nm, a fronte però di maggiore perdita ottica (nell’ordine

di 1 dB/cm), sensibilità alla polarizzazione e soprattutto un più difficile

accoppiamento con la fibra ottica. E’ stata pertanto ipotizzata una

differenziazione di guide d’onda a seconda del fine d’uso, puntando su

strutture a dimensioni più ridotte per collegamenti intra ed inter-chip,

in cui l’accoppiamento ottico in fibra non è necessario e soprattutto le

lunghezze di collegamento tipiche sono sostanzialmente ridotte, ed

impiegando strutture di dimensioni maggiori, nell’ordine di 2-3 µm, per

i collegamenti di lunghezza maggiore, portando a perdite

caratteristiche inferiori a 0.3 dB/cm, e per l’accoppiamento esterno in

fibra [1].

105

S.Penna, S.Di Bartolo,V.Attanasio, A.Otomo, L. Mattiello

Dal momento che il Silicio è un materiale a band gap indiretto non

può essere facilmente impiegato per la realizzazione di sorgenti

ottiche; di conseguenza, la piattaforma SOI viene solitamente

impiegata per la realizzazione di PIC sostanzialmente passivi.

L’obiettivo di realizzare laser su Silicio, ad esempio tramite nanocristalli

[10] o tramite drogaggio del Silicio stesso con materiali ad emissione IR

come l’Erbio [10], costuisce oggi una sfida ancora aperta. A tal

proposito, nel 2004 la University of California Santa Barbara [5] e in

forma migliorata Intel nel 2005 [6] hanno dimostrato emissione laser

da Silicio sfruttando l’effetto Raman, le cui effettive possibilità di

integrazione a basso costo su chip devono comunque essere ancora

dimostrate. Per questo motivo la Silicon Photonics basata su SOI viene

considerata per lo più per dispositivi passivi, ovvero, oltre alle già citate

guide d’onda: accoppiatori [11][12][13], riflettori di Bragg (DBR) [14], e

AWG (Arrayed Waveguide Gratings) [15].

Per quanto riguarda la funzione di fotorivelazione, dal momento

che il Silicio è trasparente alle lunghezze d’onda superiori a 1100 nm, si

utilizza un film sottile di Germanio, che è compatibile con il processo

CMOS, in posizione adiacente al core di Silicio per sfruttare

l’accoppiamento dei modi evanescenti. Sono stati dimostrati rivelatori

con bande fino a 120 GHz [16] e responsività superiore a 1.05 A/W

[17], sebbene non integrati su piattaforma.

2.2 Fosfuro d’Indio

La piattaforma basata su InP è quella che attualmente consente di

realizzare i PIC più complessi, in particolare per le caratteristiche

intrinseche del InP che permette l’implementazione di funzioni chiave

dei circuiti fotonici come le funzioni attive di emissione laser e

amplificazione.

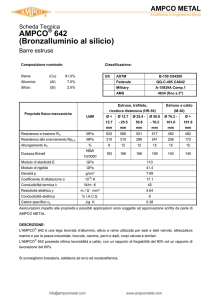

Pertanto i blocchi funzionali realizzabili coprono l’intera gamma

delle funzioni ottiche, come illustrato nella tabella dell’Istituto COBRA

(Communications Technologies Basic Research and Applications)

dell’Università Tecnica di Eindhoven [18] riportata in figura 1,

riassumbili in funzioni passive, modulatori di fase, amplificatori ottici e

covertitori di polarizzazione [19]: accoppiatori MMI couplers ed AWG,

switch ottici e modulatori, laser multi-lunghezza d’onda e tunabili, flipflops e convertitori di lunghezza d’onda ultraveloci, laser al

picosecondo e splitter e convertitori di polarizzazione [18][19].

In modo simile alla microelettronica, le diverse funzioni si possono

ottenere combinando tra loro i singoli blocchi funzionali. L’introduzione

degli Arrayed Waveguide Gratings (AWG) ha consentito di

incrementare la complessità dei PIC su InP, arrivando in tempi recenti

ad ottenere chip fotonici con oltre 450 componenti integrati su singolo

substrato [20][21]. A questo proposito, osservando i tempi di progresso

e le prestazioni ottenute, il COBRA ha proposto un interessante

parallelismo con la legge di Moore, di fatto confermandone la validità

anche per la microfotonica integrata [19].

106

La Comunicazione N.R.& N.

Tecnologie di fotonica integrata: dispositivi e applicazioni

Integrated photonic technologies: devices and applications

I componenti passivi su InP godono di prestazioni non ottimali per

quanto riguarda le perdite ottiche, che hanno in media un’ordine di

grandezza superiore ai corrispettivi in Silicon Photonics. Di

conseguenza si adattano per la realizzazione di chip ad elevata densità,

in cui la lunghezza ottiche, ma non riescono a garantire un’efficiente

connessione su lunghezze maggiori.

Tuttavia, anche per incrementare le possibilità di applicazione della

tecnologia InP, che come vedremo nella sezione successiva segue un

nuovo approccio mirato a favorire lo sviluppo in chiave commerciale

della fotonica integrata, un’intensa attività di R&D riguarda

l’integrazione delle sorgenti e degli amplificatori InP su Silicon

Photonics.

Figura 1. Elementi circuitali

e funzionalità ottiche nei

circuiti fotonici integrati

basati su piattaforma InP

[18]

Da questo punto di vista le difficoltà risiedono nella diversa

costante reticolare tra InP e Silicio (variazione del 4%) e al diverso

coefficiente di espansione termica, che rende impossibile applicare i

metodi classici di bonding ad alta temperatura. Inoltre, il bonding

pregiudica le possibilità di elevata portata di produzione ottenibile con

la Silicon Photonics, riguardando un processo intrinsecamente più lento

e delicato.

Ad ogni modo, un’interessante alternativa ai processi di bonding a

bassa temperatura basata su plasma di Ossigeno [22] è costituita

dall’adesione mediante polimero, tipicamente DVS-BCB [23], tramite

processi in soluzione liquida più a basso costo.

107

S.Penna, S.Di Bartolo,V.Attanasio, A.Otomo, L. Mattiello

2.3 Nitruro di Silicio

La tecnologia basata su Nitruro di Silicio Si 3 N 4 consente di ottenere

perdite minime pari a 0.00045 dB/cm [26], preservando tali

caratteristiche anche in caso di bassi raggi di curvatura, necessari per

connettere i blocchi del chip minimizzando il loro fattore di forma. In

particolare determinante per ottenere simili prestazioni è la

realizzazione di strutture caratterizzate dall’alternanza di Si 3 N 4 ed SiO 2 .

Il processo di fabbricazione compatibile con la tecnologia CMOS è

caratterizzato da processi di deposizione chimica in fase vapore (CVD) a

bassa pressione.

Questo processo permette di ottenere una composizione stabile

dei materiali, requisito necessario per il controllo delle loro proprietà

ottiche che influenzano le prestazioni della propagazione all’interno

della guida d’onda. La finestra di trasmissione dei due materiali

permette la realizzazione di guide a bassa perdita su un ampio

intervallo spettrale, dal visibile violetto (400 nm) fino all’infrarosso

(2350 nm), adattandosi pertanto ad applicazioni che vanno oltre le

comunicazioni insenso stretto, includendo la sensoristica ed il

biomedicale. Sono state definite tre geometrie di guida d’onda: box

shell [24], doppia striscia [25] e filled box [26].

In particolare, altra peculiarietà delle strutture basate su Si3N4

nella tecnologia proprietaria TriPlex, è la possibilità di abbinare l’alto

contrasto d’indice con l’accoppiamento ottico tra chip e fibra, due

obiettivi che solitamente sono mutuamente esclusivi con strutture in

Silicon Photonics [26].

2.4 Silicon Organic Hybrid Technology

Un ramo della Silicon Photonics basata sul SOI è la cosiddetta

Silicon Organic Hybrid Technology (SOH) [27], che fa uso di materiali

attivi di origine organica, come monomeri [27] e soprattutto polimeri

[28][29], che introducono vantaggi come il basso costo di processo, in

particolare per i polimeri dal momento che possono essere lavorati in

fase liquida con tecniche di stampa, la facilità di integrazione legata alla

loro natura amorfa che elimina le restrizioni dell’uguaglianza della

costante reticolare con il Silicio e soprattutto le possibilità uniche e

potenzialmente illimitate di migliorare o, usando un termine in voga

nella comunità scientifica, “cucire” le proprietà dei materiali

specificatamente per una determinata applicazione (molecular

tailoring) tramite il design molecolare e la conseguente sintesi chimica.

Quest’ultimo aspetto consente di ottenere materiali che in alcuni casi

sorpassano in prestazioni gli analoghi inorganici.

Un ulteriore vantaggio della tecnologia SOH è la sua completa

compatibilità con il processo di fabbricazione CMOS, in particolare si

configura come un processo di back-end, ovvero che si pone al termine

del tipico flusso di processo CMOS, pertanto può essere integrato senza

indurre variazioni nelle linee di produzione già presenti e per di più con

processi di stampa, dai costi caratteristici trascurabili rispetto al resto

della linea di produzione. Intrinsecamente, l’uso di materiali organici

108

La Comunicazione N.R.& N.

Tecnologie di fotonica integrata: dispositivi e applicazioni

Integrated photonic technologies: devices and applications

consente di replicare le caratteristiche di basse perdite ottiche dei

dispositivi basati su SOI dal momento che le condizioni di alto contrasto

d’indice tra Silicio e polimeri sono preservate.

L’applicazione più nota di tecnologia SOH è la modulazione di fase,

ottenuta tramite l’impiego di polimeri elettro-ottici che mostrano

coefficienti non lineari di molto superiori a 100 pm/V [30] (l’analogo

inorganico, il Niobato di Litio, è nell’ordine di 30-40 pm/V). La

tecnologia SOH è spesso associata alle guide d’onda slot [31] per via

dell’elevata concnetrazione di campo ottico all’interno della struttura

nanometrica. La guida d’onda slot è basata su tecnologia SOI e,

sfruttando la forte discontinuità di campo elettrico tra il Silico ed il

materiale che compone lo slot, solitamente un polimero o un Ossido di

Silicio, induce un miglioramento del campo nella centrale regione di

slot di un fattore pari al rapporto delle rispettive costanti dielettriche

dei materiali, ovvero al quadrato degli indici di rifrazione, n Si 2/n slot 2=46, come si può osservare nel profilo di campo ottico mostrato in figura,

con fattori di confinamento della radiazione ottica che superano il 30%.

Accoppiando le guide d’onda slot ai materiali elettro-ottici è possibile

ottenere modulatori di fase o anche, composti all’interno di strutture

inteferometriche Mach Zender, modulatori di ampiezza che presentano

valori di tensione V π inferiori ad 1V [32] e soprattutto bitrate superiori

a 100 Gbit/s, con punte a 160 Gb/s [33].

Figura 2. Struttura di una

guida d‘onda slot striploaded per modulatori

fotonici in tecnologia SOH e

immagine al microscopio

elettronico (SEM)

Utilizzando lo stesso tipo di materiali elettro-ottici è possibile

realizzare anche la funzione di commutazione (switching) ad alta

frequenza, necessaria per applicazioni specifiche come i data center in

cui a breve termine saranno richiesti tempi caratteristici di switching

nell’ordine dei nanosecondi, mentre allo stato dell’arte i tempi

caratteristici sono nell’ordine dei ms, con valori di punta dimostrati

nell’ordine dei 100 µs. Alcuni esempi, mirati per ora più alla

dimostrazione concettuale, mostrano tensione di switching inferiore a

10V con un coefficiente nonlineare pari a 250 pm/V su lunghezza di

accoppiamento di 1.7 cm [34].

Similmente ai materiali organici elettro-ottici è possibile utilizzare

anche altri tipi di materiali che ben si accoppiano alla tecnologia SOI

per la realizzazione di sorgenti o di fotorivelatori.

109

S.Penna, S.Di Bartolo,V.Attanasio, A.Otomo, L. Mattiello

In particolare i materiali organici drogati con Erbio possono

fungere da materiali attivi per la generazione/amplificazione della

radiazione IR a 1550 nm all’interno del chip. A questo proposito sono

stati dimostrati elettroluminescenza da LED organico cresciuto su Silicio

con tecniche da vuoto [35] e di recente, con tecniche di processo in

fase liquida, anche se non su subtrato di Silicio [36]. L’ISCOM ha

un’attività in essere su quest’ultima linea che ha portato a risultati

promettenti sia per quanto riguarda la realizzazione di guide d’onda

con processi di fabbricazione interamente ottici [37][38], sia per le

potenzialità di realizzazione di un dispositivo laser su Silicio [39]

mediante tecniche di fabbricazione a basso costo come la litografia per

Nanoimprinting [40] o nell’estremo ultravioletto (EUV) [39]. In

aggiunta, mediante la collaborazione con l’Università La Sapienza di

Roma sono state realizzate delle versioni avanzate dei monomeri

drogati con Erbio in grado di migliorare l’efficienza di emissione e

soprattutto di consentire una lavorazione interamente in fase liquida,

condizione abilitante per un processo a basso costo su scala industriale

[37][40].

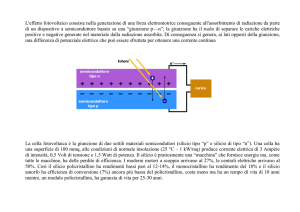

Per quanto riguarda la funzione di fotorivelazione, l’esplosione

recente del fotovoltaico organico ha portato a miglioramenti netti in

termini di materiali attivi disponibili per l’assorbimento ottico, per lo

più nel range visibile ma in prospettiva anche per il range del vicino

infrarosso inbanda C. Al momento sono in essere diversi lavori di

caratterizzazione ed ulteriore miglioramento dei materiali organici

attivi in termini di massimizzazione della velocità di risposta, peculiarità

dei fotorivelatori rispetto alle celle fotovoltaiche che lavorano con luce

continua (f=0). Si può prevedere facilmente che l’immenso know how

generato per il fotovoltaico organico in termini di design e sintesi di

110

Figura 3. Spettro laser

preliminare di cavità laser

DFB basata su Erbio trisidrossichinolina

come

materiale

attivo

per

l’emissione a 1530 nm

(banda C) [39] e immagine

del reticolo DBR realizzato

su wafer di Silicio con unico

processo di stampa da nanoimprinting su larga area (10

2

cm ) [41]

La Comunicazione N.R.& N.

Tecnologie di fotonica integrata: dispositivi e applicazioni

Integrated photonic technologies: devices and applications

nuovi materiali per l’assorbimento ottico porterà allo sviluppo in tempi

brevi di materiali in grado di competere con i loro equivalenti

inorganici.

Da questo punto di vista è stato domostrato un fotorivelatore con

una larghissima risposta spettrale (300–1450 nm), alta rivelabilità

(1012−1013 cm Hz 0.5 W–1) e un intervallo dinamico lineare (>100 dB), in

grado pertanto di competere direttamente con rivelatori in Silicio e

InGaAs [42].

Una delle principali problematiche derivanti dall’uso dei materiali

organici in elettronica è legato alla stabilità. Tuttavia, un lavoro di

sviluppo specifico in tal senso ha portato già a dimostrare la

compatibilità di alcuni prototipi come i modulatori polimerici ai

protocolli di certificazione Telcordia, ovvero previsti dall’associazione

delle industrie di telecomunicazione statunitensi, che fungono da

standard di stabilità [43][44].

Come già riportato in precedenza, ciascuna di queste tecnologie

gode di vantaggi e svantaggi legatti alle proprie cararteristiche specifici.

Pertanto, nell’ottica di convogliare gli sforzi verso obiettivi comuni,

l’approccio che domina il periodo corrente è l’integrazione tra le

diverse tecnologie integrate, in modo tale da ampliare la gamma di

applicazioni possibili e migliorare le prestazioni ottenibili. Come

accennato, ci sono diverse alternative proposte per l’integrazione dei

dispositivi attivi in InP su Silicon Photoncs, sebbene il ricorso al bonding

tende comunque ad innalzare i costi di fabbricazione se pensati su

processo in linea [45]. Di recente, ad inizio 2015, alcuni dei partner di

jEPPIX insieme a Lionix hanno annunciato l’integrabilità della tecnologia

InP su Triplex [46], in grado qundi di combinare le funzioni attive

dell’InP con le eccellenti proprietà guidanti per applicazioni nel visibile

e nel vicino infrarosso del Triplex.

3. Piattaforme Tecnologiche e Generic Foundry Model

Come citato in precedenza, una linea di processo per la

fabbricazione di chip ha costi proibitivi, sia per chip elettronici che per

PIC. Si consideri ad esempio che la realizzazione di una singola

maschera litografica ad elevata densità ha costi nell’ordine dei $

100.000 e che per un intero processo possono occorrere fino a 40

maschere.

Tuttavia, come detto, l’industria microelettronica può ripartire

questi costi su un elevato volume di produzione legato alle enormi

richieste di mercato, con quantiaà di lavorazione di circa 1.000-10.000

wafer per settimana su una singola linea [4]. Nel caso dei PIC, non

esiste ancora un mercato caratterizzato da simili volumi di richiesta. In

realtà per la quasi totalità delle applicazioni non esiste ancora un

mercato, per cui gli elevati costi di sviluppo tendono a limitare il

numero di attori del settore a pochi soggetti con disponibilità

111

S.Penna, S.Di Bartolo,V.Attanasio, A.Otomo, L. Mattiello

finanziarie adeguate. In aggiunta, la forte etereogeneità di materiali e

quindi di processi tecnologici per la realizzazione delle singole funzioni

ottiche tende ad innalzare ulteriormente i costi di sviluppo [19].

Tuttavia, proprio per far fronte a queste barriere, si è affermato un

nuovo modello basato sulla condivisione delle onerose infrastrutture

tecnologiche con la realizzazione di piattaforme tipicamente a iniziale

sovvenzione pubblica. Il concetto di riferimento è quello di Multi

Project Wafer (MPW), mutuato dall microelettronica, ovvero un wafer

al cui interno sono raccolti i design di dispositivi provenienti da diversi

clienti o partner fino saturarne l’intera area, consentendo di ripartire i

costi di realizzazione tra più progetti e creando quindi un business

sostenibile sia per il realizzatore che per il cliente [47].

Questo modello di sviluppo consente la nascita di un indotto

legato a singole competenze della catena del valore, come la

progettazione, il testing, l’integrazione, lo sviluppo di proprietà

intellettuali, incrementando la nascita di aziende anche di piccole

dimensioni ma dall’alto contenuto tecnologico [8]. Inoltre un sistema di

questo tipo favorisce la nascita delle fabless companies, ovvero delle

aziende senza impianto di fabbricazione proprietario (fab), che possono

sviluppare componenti per specifiche applicazioni, denominati ASPIC

(Application Specific PIC), demandando la realizzazione alla specifica

piattaforma tecnologica.

Tramite lo strumento dei programmi quadro FP6 ed FP7, l’Europa

ha investito pesantemente nel supporto alla nascita delle piattaforme

europee, in particolare tramite la Network of Excellence ePIXnet

(European Photonic Integrated Components and CircuitS Network) del

programma FP6. La vision di sviluppo del modello di Fonderia Generica

(Generic Foundry Model) applicato alla fotonica integrata è stato

introdotto proprio in ePIXnet [48].

Dalla rete di ePIXnet sono nati dei consorzi tecnologici a

partecipazione pubblica e privata, come ePIXfab, che è la piattaforma

di riferimento per la tecnologia SOI legata dal punto di vista dei

processi ai centri IMEC (belgio) e CEA-LETI (Francia), e jEPPIX (Joint

European Platform on Photonic Integrated CrcuitS), basata sulla

tecnologia in Fosfuro di Indio e legata per la maggior parte della

partnership al polo tecnologico di Eindhoven (Paesi Bassi). In aggiunta,

sempre originata da ePIXnet, si è affermata la tecnologia Del consorzio

Triplex basata su Nitruro di Silicio, attualmente sviluppata dall’azienda

olandese Lionix.

Ultimo “prodotto” di ePIXnet è la piattaforma ePIXpack per lo

sviluppo di tecnologie di packaging specifiche per i chip fotonici.

Attualmente il costo del packaging, che diversamente dai chip

elettronici è legato alle problematiche di accoppiamento della luce in

fibra, tende a superare di un ordine di grandezza il rimanente costo del

chip, con una percentuale sul costo totale stimato al 94% (fonte: FP7

Fabulous project).

112

La Comunicazione N.R.& N.

Tecnologie di fotonica integrata: dispositivi e applicazioni

Integrated photonic technologies: devices and applications

In ambito extra-Europeo è degna di nota la piattaforma a matrice

statunitense OpSis, giunta a conclusione a inizio 2015, legata

all’Università di Delaware e costituita da una rete di collaborazione che

ha visto partecipi anche le aziende leader della Silicon Photonics della

Silcon Valley come Luxtera e Kotura (ora all’interno di Mellanox), le

quali dispongono ognuna di linee di fabbricazione dedicate su SOI con

risoluzione rispettivamente di 200 nm e 150 nm [47], l’agenzia

tecnologica di Singapore ASTAR, Hewlett-Packard e BAE Systems.

La funzione di supporto pubblico che in Europa è assolta dai

programmi quadro, con impegni rinnovati anche all’interno dell’attuale

programma Horizon2020 per lo sviluppo di applicazioni di fotonica

integrata in ambito ICT e datacom, negli USA è svolta da DARPA

(Defense Advanced Research Projects Acency), che ha lanciato diversi

programmi di finanziamento come UNIC, mirati principalmente ad

applicazioni in ambito HPC (High Performance Computing).

In Italia si annota la recente inaugurazione del centro InPhoTec

(Integrated Photonic Techology center) all’interno del polo di ricerca

CNR-Scuola Sup. Sant’Anna di Pisa, interamente dedicato alla

realizzazione di dispositivi fotonici integrati, includendo l’attività di

packaging che attualmente rappresenta uno dei principali colli di

bottiglia per lo sviluppo commerciale dei PIC.

Conclusioni

Come detto, per garantire l’esplosione commerciale della fotonica

integrata, nonostante gli indiscussi vantaggi e potenzialità, dipende

dalle dimensioni del mercato di riferimento.

Attualmente c’è un forte impegno nello sviluppo di

interconnessioni ottiche, in particolare dedicate ad applicazioni in data

centers e per i microprocessori, e nel campo della sensoristica in fibra,

tutti settori caratterizzati da enormi potenziali volumi di richiesta che

faciliterebbero lo sviluppo commerciale e prima ancora lo sviluppo

tecnologico.

113

S.Penna, S.Di Bartolo,V.Attanasio, A.Otomo, L. Mattiello

Bibliografia.

[1] M. Ashgari, A. V. Krishnamoorty, Energy-efficient communication,

Nature, 5, p. 268-270, 2011

[2] Y. Arakawa et al., Silicon Photonics for Next Generation System

Integration Platform, IEEE Communications Magazine (2013)

[3] B. Jalali et al., Silicon photonics, J. Lightwave Technol. 24(12), p.

4600-4615, 2006

[4] T.W. Baehr-Jones, Myths and rumours of silicon photonics, Nature

Photonics, 6, p. 206-208 (2012)

[5] O. Boyraz et al., Demonstration of a silicon Raman laser, Opt. Exp.,

12 (21), p. 5269-5273 (2004)

[6] H. Rong et al., A continuous-wave Raman silicon laser, Nature 433,

p. 725-728 (2005)

[7] Liao S, Feng N, Feng D, Dong P, Shafiiha R, Kung C, Liang H, Qian W,

Liu Y, Fong J, Cunningham J, Luo Y, Asghari M. 36 GHz submicron silicon

waveguide germanium photodetector. Optics Express,19, p. 10967–

10972 (2011)

[8] M. Hochberg et al., Towards fabless silicon photonics, Nature

Photonics, 4, p. 492-494 (2010)

[9] B Aspar et al., The generic nature of the Smart-Cut® process for thin

film transfer, Journal of Electronic Materials, Vol. 30, No. 7, 2001

[10] F. Priolo et al., Silicon nanostructures for photonics and

photovoltaics, Nature Nanotechnologies, 9, p.19-32 (2014)

[11] Na Net al., Efficient broadband silicon-on-insulator grating coupler

with low backreflection. Opt. Lett. 36, p2101–3 (2011)

[14] Wang X et al, Narrow-band waveguide Bragg gratings on SOI

wafers with CMOS-compatible fabrication process. Opt. Exp. 20,

p.15547–58 (2012)

[15] Fu X, Dai D., Ultra-small Si-nanowire-based 400 GHz-spacing 15 X

15 arrayed-waveguide grating router with microbends, Electron Lett.

47, p. 266–8 (2011)

[16] Vivien L. et al., Zero-bias 40 Gbit/s germanium waveguide

photodetector on silicon. Opt Exp., 20, p. 1096–101 (2012)

[17] Liao S. et al., 36 GHz submicron silicon waveguide germanium

photodetector, Opt. Exp. 19 p. 10967–72 (2011)

[18] M. Smit et al., An introduction to InP-based generic integration

technology, Semiconductor Science and Technology, 29, p. 1-41 (2014)

[19] G. Gilardi et al., Generic InP-Based Integration Technology: Present

and Prospects, Progress In Electromagnetics Research, 147, p. 23–35

(2014)

[20] COrzine S W, Large-scale InP transmitter PICs for PM-DQPSK fibre

transmission systems, Photon. Technology Letters, 22, p. 1015-1017

(2010)

114

La Comunicazione N.R.& N.

Tecnologie di fotonica integrata: dispositivi e applicazioni

Integrated photonic technologies: devices and applications

[21] Stabile R et al., Monolithic active-passive 16x16 optoelectronic

switch, Optics Letters, 37, p. 4666-4668

[22] D. Liang et al., Hybrid Integrated Platforms for Silicon Photonics,

Materials, 3, p. 1789-1802 (2010)

[23] Roelkens et al., Adhesive bonding of InP/InGaAsP Dies to

Processed Silicon-On-Insulator wafer using DVS-bis-Benzocyclobutene,

J. Electrochem Soc., 153, G1015-G1019 (2006)

[25] J. F. Bauters et al., Planar waveguides with less than 0.1 dB/m

propagation loss fabricated with wafer bonding, Optics Express, vol. 19,

no. 24, pp. 24090– 24101, Nov. 2011.

[Zhuang] L. Zhuang et al.,, Low-loss, high-index-contrast Si3N4/SiO2

optical waveguides for optical delay lines in microwave photonics signal

processing, Optics Express, vol. 19, no. 23, pp. 23162–23170, Nov. 2011

[24] K. Wörhoff et al., TriPleX: a versatile dielectric photonic platform,

Advanced Optical Technologies, 4 (2), p. 189–207 (2015)

[26] Leinse A. et al., TriPleXTM platform technology for photonic

integration: applications from UV through NIR to IR, IEEE 2011

[27] J. Leuthold et al., Silicon Organic Hybrid Technology - A Platform

for Practical Nonlinear Optics, Proceedings of the IEEE, 97 (7), p. 13041316 (2009)

[Baehr Jones] T.W. Baehr Jones et al., Polymer Silicon Hybrid Systems:

A Platform for Practical Nonlinear Optics, J. Phys. Chem. C, 112, 8085–

8090 (2008)

[29] F. Qiu et al., A hybrid electro-optic polymer and TiO2 double-slot

waveguide modulator, Scientific Reports, 5, 8561 (2014)

[30] Y. Enami et al., Hybrid polymer/sol–gel waveguide modulations

with exceptionally large electro–optic coefficients, Nature Photonics, 1,

p. 180-185 (2007)

[31] V. Almeida et al., Guiding and confining light in void nanostructure,

Optics Letters, 29(11), p. 1209-1211 (2004)

[32] T. Baehr-Jones et al., Nonlinear polymer-clad silicon slot

waveguide modulator with a half wave voltage of 0.25 V, Appl. Phys.

Lett., 92 1633031-3 (2008)

[33] 40 GBd 16QAM Signaling at 160 Gbit/s in a Silicon-Organic Hybrid

(SOH) Modulator, Journal of Light. Tech., 2015

[34] Silicon/electro-optic polymer hybrid directional coupler switch,

Proc. SPIE 8991, Optical Interconnects XIV, 89910Q (2014)

[35] W.P. Gillin et al., Erbium (III) tris (8-hydroxyquinoline)(ErQ): A

potential material for silicon compatible 1.5 m emitters, Applied Phys.

Lett., 74 (6), p. 798-799 (1999)

[36] P. Martìn-Ramos et al., Active layer solution-processed NIR-OLEDs

based on ternary erbium(III) complexes with 1,1,1-trifluoro-2,4pentanedione and different N,N-donors, Dalton Trans., 43, p. 1808718096 (2014)

115

S.Penna, S.Di Bartolo,V.Attanasio, A.Otomo, L. Mattiello

[37] S. Penna et al., Applications and low cost processing of Erbium

Quinolinolates for active integrated photonic devices, Proc. IEEE Int.

Conf. Transaprent Optical Networks (2014)

[38] S. Penna et al., Opportunities for low Cost Processing of Erbium 8Quinolinolates for Active Integrated Photonic Applications, Journal of

Nanoscience and Nanotechnology (2015) in fase di stampa

[39] S. Prezioso et al., Infrared photoluminescence of erbium-tris (8hydroxyquinoline) in a distributed feedback cavity, Journal of

Luminescence, 131 (4), p. 682-685 (2011)

[40] S. Penna et al., Towards the implementation of an organic

inorganic laser for next generation optical applications, Proc. Of

Conference on Laser and Electro-Optics (2010)

[41] S. Penna et.al., Near-Infrared luminescent properties of

halogenated tetrakis erbium quinolinolates for photonic applications ,

in preparazione

[42] Gong, X. et al., High-detectivity polymer photodetectors with

spectral response from 300 nm to 1450 nm. Science 325, 1665–1667

(2009)

[43] M. Lauermann et al., 64 GBd Operation of a Silicon-Organic Hybrid

Modulator at Elevated Temperature, Optical Fiber Communication

Conference 2015, Tu2A.5 (2015)

[44] R. Dinu et al., Environmental stress testing of electro–optic

polymer modulators, Journal of Lightwave Technology Vol. 27, Issue 11,

pp. 1527-1532 (2009)

[45] J.T Robinson et al., First-principle derivation of gain in high-index

contrast waveguides, Optics Express, 16 (21), p. 16659-16669 (2008)

[46] http://www.vlcphotonics.com/2015/02/02/new-photonicintegration-platform-available-combining-inp-and-triplex-tmtechnologies/

[47] A. Eu-Jin Li et al., Review of Silicon Photonics Foundry Efforts, IEEE

J. Sel. Top. Quantum Electr., 4 (20), 2014

[48]

http://www.epixnet.org/uploads/media/visionphotonicsfoundryvs16.

doc

116

La Comunicazione N.R.& N.