Evoluzione dei

Sistemi

Prof. Giuseppe Pirlo

Dipartimento di Informatica

Università degli Studi di Bari

Languages, Levels, Virtual Machines

A multilevel machine

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

Contemporary Multilevel Machines

A six-level computer.

The support method for each level is indicated below it .

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

Assembler

Sistema Operativo (1960)

ISA

Users:

Programmatori

(Traduzione)

Contemporary Multilevel Machines

Micoprogrammed

ALU + registers (data path)

Livello logico-digitale (gate)

Users:

Sistemisti

(Interpretazione)

(Wilkes ’51) vs

“wired logic”

A six-level computer.

The support method for each level is indicated below it .

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

Evolution of Multilevel Machines

•

Invention of microprogramming (Wikes 1951)

•

Invention of operating system (IBM 1960) (chiamate di

sistema, sistemi batch/time-sharing)

•

Migration of functionality to microcode (CISC)

•

Elimination of microprogramming (RISC)

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

Milestones in Computer Architecture (1)

Some milestones in the development of the modern digital

computer.

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

Milestones in Computer Architecture (2)

Some milestones in the development of the modern digital

computer.

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

Computer Generations

•

0th Generation

Mechanical Computers (1642 – 1945)

•

First Generation

Vacuum Tubes (1945 – 1955)

•

Second Generation

Transistors (1955 – 1965)

•

Third Generation

Integrated Circuits (1965 – 1980)

•

Fourth Generation

Very Large Scale Integration (1980 – …) (GUI, …)

•

Fifth Generation

Pervasive Computers / Ubiquitous Computers (1990 – …)

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

Von Neumann Machine (1952)

The original Von Neumann machine.

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

PDP-8 Innovation – Single Bus (1965)

The PDP-8 omnibus

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

IBM 360 (1964)

The initial offering of the IBM 360 product line.

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

Technological and Economic Forces

Moore’s law predicts a 60-percent annual increase in the

number of transistors that can be put on a chip.

The data points given in this figure are memory sizes, in bits.

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

The Computer Spectrum

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

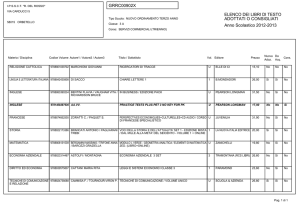

Intel Computer Family (1)

The Intel CPU family. Clock speeds are measured in MHz

(megahertz) where 1 MHZ is 1 million cycles/sec.

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

Intel Computer Family (2)

The Pentium 4 chip. The photograph is copyrighted by the Intel

Corporation, 2003 and is used by permission.

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

Intel Computer Family (3)

Moore’s law for (Intel) CPU chips.

Tanenbaum, Structured Computer Organization, Fifth Edition, (c) 2006 Pearson Education, Inc. All rights reserved. 0-13-148521-0

Core i7

Introdotto nel 2008 come diretto discendente CPU 8088 (PC IBM)

Core i7 (Architettura Nahalem – prima architettura): CPU a 4 processori,

731 milioni di transistor, frequenza 3,2 GHz , larghezza di linea 45

nanometri

Core i7 (Architettura Sandy Bridge – architetture recenti): CPU da 2 a 6

processori, 1,16 miliardi di transistor, frequenza 3,5 GHz , larghezza di

linea 32 nanometri

-

Retrocompatibilità (stesse funzionalità ISA): 80286, 80486, Pentium,

Pentium II, Pentium Pro, Pentium III, Pentium 4 (stessi registri, stesse

istruzioni, stesso standard in virgola mobile IEEE 754 su chip, ecc.)

17

Core i7

Packaging:

-

Supporto LGA (Land Grid Array)

quadrato (37,5 mm di lato) con 1155

pad posti sul fondo.

- Consuma tra i 17 e i 150 Watt

(problemi di dissipazione di calore) 5

stati di funzionamento x risparmiare

energia (da “piena esecuzione a quello

di “sonno profondo”)

18

Parallelismo

Tassonomia di Flynn

Single

Instruction

Stream

Multiple

Instruction

Stream

Single

Data

Stream

Multiple

Data

Stream

SISD

SIMD

(Calcolatori

sequenziali)

(più processori

eseguono la stessa

istruzione su dati

diversi)

MISD

MIMD

(più processori

eseguono istruzioni

differenti sullo

stesso dato – non

realizzabile!)

(più processori

eseguono istruzioni

differenti su dati

differenti)

Parallelismo a livello di istruzione (1)

Per parallelismo si intende la capacità di eseguire più

azioni allo stesso istante.

Esistono due tipologie di parallelismo:

–

a livello di processore, e quindi sono presenti più processori

che lavorano congiuntamente sullo stesso problema

–

a livello di istruzione, cioè il parallelismo viene sfruttato

all’interno delle singole istruzioni per fare in modo che

l’elaboratore esegue più istruzioni contemporaneamente.

Uno dei concetti applicati è quello di pipeline.

Il meccanismo di pipeline divide il ciclo di esecuzione in

più parti e ciascuna parte è affidata ad una

componente hardware.

Parallelismo a livello di istruzione (2)

a)

b)

Pipeline a cinque fasi

Avanzamento degli stadi in funzione del tempo. Sono rappresentanti nove cicli

Pipeline: Prestazioni

Sia

•k: numero di stadi della pipeline

•n: numero di istruzioni da eseguire

•t: tempo di uno stadio (tempo massimo).

(si considerino inoltre trascurabili i tempi di commutazione da uno

stadio al successivo)

Allora il tempo totale richiesto Tpipe per eseguire le n istruzioni (senza

salti) è:

Tpipe=[k + (n-1)] t

Il fattore di velocizzazione (speed-up) della pipeline rispetto ad una

architettura tradizionale è:

Tconvenzionale

nkt

nk

T pipe

[k (n 1)]t [k (n 1)]

Multiprocessori

Un sistema composto da più CPU ed una unica unità di memoria

condivisa viene detto Multiprocessore.

E’ necessario che le CPU siano ben sincronizzate per evitare conflitti

nelle operazioni sulla memoria condivisa.

Ad esempio:

Se nella memoria è contenuta una immagine da elaborare è possibile

affidare una sezione della immagine ad ogni CPU che eseguirebbe il

medesimo programma delle altre sulla sezione di immagine ad essa

affidata, riducendo il tempo di elaborazione dell’immagine

Multicomputer

Un multicomputer è un sistema

composto da più CPU dotate di una

memoria privata nel quale vengono

contenuti dati che non sono

condivisi ma utili all’elaborazione.

Il minor scambio sul bus rende più

veloce l’esecuzione.

L’area condivisa è utilizzata per

contenere, ad esempio, il codice del

programma da eseguire.

Le CPU sono così debolmente connesse e la comunicazione fra di

loro avviene attraverso l’uso di messaggi che viaggiano sul bus che le

collega.

Parallelismo a livello di processore (1)

Un array computer (ovvero un array di processori) consiste in un

insieme di processori che eseguono le medesime istruzioni su insiemi

diversi di dati.

La singola unità di controllo invia i dati a ciascuna coppia processorememoria. Ogni processore esegue la medesima istruzione degli altri a

passi sincronizzati sui dati contenuti nella memoria ad esso

associata.

Parallelismo a livello di processore (1)

Sia P un processo e supponiamo che sia costituito da una frazione seriale fs

(realizzabile in un tempo Ts) e da una frazione fp realizzabile in parallelo

(realizzabile in un tempo Tp) dove ovviamente fs+fp =1.

Sia T1 e Tn rispettivamente il tempo di esecuzione del processo su 1 ed n

processori:

T1=Ts+Tp (può essere considerato normalizzato a 1)

Tn=Ts+Tp/n

Lo speed-up S(n) con n processori è pari a T1/Tn (Legge di Andahl)

T1

S ( n)

Tn

1

1

n

fp

1 f s nf s (1 f s )

f

fs

s

n

n