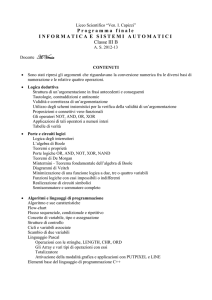

Aritmetica in virgola mobile

Algebra di Boole e reti logiche

Esercizi

Mercoledì 8 ottobre 2014

Notazione scientifica normalizzata

La rappresentazione in virgola mobile che adotteremo si basa sulla

notazione scientifica normalizzata

• Notazione scientifica normalizzata in base 2:

N= (-1) s M 2exp

s = segno positivo se s=0, negativo se s=1

M = Mantissa numero decimale con parte intera uguale a 1

exp = esponente opportuno (intero)

Esempi: +11,001 = (-1) 0 1,1001 21

- 1100,1 = (-1) 1 1,1001 23

+0,0011= (-1) 0 1,1 2-3

(senza polarizzazione)

polarizzazione = 127

: esempi

Aritmetica in virgola mobile

Algoritmo

Troppo difficile?

• Esiste anche la doppia precisione su 64 bit (1-1152) (double in C)

• Non studieremo moltiplicazione e divisione

• Le istruzioni MIPS che studieremo tratteranno

numeri rappresentati in complemento a 2.

Per esempio: add, sub,…

• Il MIPS supporta anche il formato IEEE 754 a

singola (e doppia) precisione con istruzioni

particolari:

Per esempio: add.s, sub.s,…

Riepilogo e riferimenti

• I numeri in virgola mobile; standard IEEE 754 a singola

precisione

• Somma in virgola mobile: [PH] par. 3.5 (fino a ‘La

somma in virgola mobile’)

• Abbiamo finito le rappresentazioni dell’informazione.

Adesso: algebra di Boole e circuiti combinatori

• Faremo un test sul programma fin qui svolto, cioè tutte

le rappresentazioni e conversioni studiate.

Mercoledì 15 ottobre?

Punto della situazione

• Abbiamo visto le varie rappresentazioni dei

numeri in binario e la loro aritmetica

• Adesso vedremo la logica digitale usata dal

calcolatore nell’ottica di

• Costruire l’ALU

• L’ALU è usata da quasi tutti i tipi di istruzioni

dell’architettura che studieremo

Algebra di Boole e reti logiche

AND ovvero il prodotto

AND(x,y) con x, y variabili che possono assumere valore

Vero o Falso.

Risultato Vero se entrambe le variabili sono poste a Vero,

Falso, altrimenti.

Interpretando Vero come 1 e Falso come 0

AND(x,y) corrisponde al prodotto x y.

x

y x*y

AND(F,F) = F

00=0

0

0

0

AND(F,V) = F

01=0

0

1

0

AND(V,F) = F

10=0

1

0

0

AND(V,V) = V

11=1

1

1

1

Tavola di verità

OR ovvero la somma

OR(x,y) con x, y variabili che possono assumere valore

Vero o Falso.

Risultato Vero se almeno una variabile è posta a Vero,

Falso, altrimenti.

Interpretando Vero come 1 e Falso come 0

OR(x,y) corrisponde alla somma x + y, in cui 1+1 = 1.

OR(F,F) = F

OR(F,V) = V

OR(V,F) = V

OR(V,V) = V

0+0=0

0+1=1

1+0=1

1+1=1

x

0

0

1

1

y

0

1

0

1

x+y

0

1

1

1

Tavola di verità

NOT ovvero la negazione

NOT(x) con x variabile che può assumere valore Vero o

Falso.

Risultato Vero se la variabile è posta a Falso;

Falso, altrimenti.

Interpretando Vero come 1 e Falso come 0

NOT(x) corrisponde alla negazione.

NOT(V) = F

NOT(F) = V

0 =1

1=0

x

0

1

x

1

0

XOR o OR esclusivo

XOR(x,y) con x, y variabili che possono assumere valore

Vero o Falso.

Risultato Vero se una variabile è posta a Vero, ma non

entrambe,

Falso, altrimenti.

Interpretando Vero come 1 e Falso come 0

XOR(x,y) corrisponde a x y + x y = x y

XOR(F,F) = F

XOR(F,V) = V

XOR(V,F) = V

XOR(V,V) = F

00=0

01=1

10=1

11=0

x

0

0

1

1

y

0

1

0

1

xy

0

1

1

0

La combinazione delle variabili e degli operatori

viene chiamata espressione logica.

Mappa di verità o tavola di verità: tabella che

definisce i valori dell’output per ogni possibile input

Circuito per l’ AND

Circuito per l’ OR

Circuito per lo XOR

Rete logica

Una rete logica è un’interconnessione di porte

logiche AND, OR, NOT, in modo che ogni uscita

da una porta alimenti al più un ingresso di una

porta a

Valori in uscita

x1= 0, x2= 0, x3= 1

Analisi di una rete: dalla rete alla funzione

• Ogni rete logica calcola una funzione booleana

dei suoi ingressi

f(x1,x2,x3) = x3 ( x1 . x2) + (x1+x3)

• Nota: vedremo che vale anche l’inverso (sintesi)

Risultato principale

Corrispondenza fra funzioni logiche e reti logiche:

• Per ogni funzione logica possiamo costruire una rete

logica che la realizza e viceversa

• Ogni funzione logica può essere espressa in termini

soltanto di AND, OR, NOT.

Analisi: data una rete determinare la funzione

calcolata

Sintesi: data una funzione logica costruire una rete

che la calcola

Riferimenti

Appendice C di [PH] «The Basic of Logic Design»:

Gates, Truth tables, and Logic Equations: C.1, C.2, C.3

Oppure [P] cap. 3 (in parte)