Fondamenti di Informatica

Ingegneria delle Comunicazioni ed Ingegneria Elettronica

Parte I - Architetture di Elaborazione

Prof. Silvio Salza

Programma svolto nell’a.a. 2012 -2032

Evoluzione dei sistemi di elaborazione.

Struttura a livelli dell’organizzazione hardware e software del sistema di elaborazione – Evoluzione

storica dei sistemi di elaborazione – Generazioni di sistemi di elaborazione – Dalla macchina di

Babbage al Personal Computer – Leggi di Moore e di Nathan – Tipologie di computer – Le famiglie

Intel e SPARC.

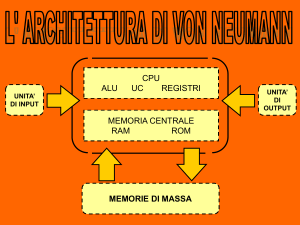

Struttura del sistema di elaborazione.

Il processore e la sua organizzazione interna – Esecuzione ed interpretazione delle istruzioni – Il

ciclo fetch-decode-execute – Architetture CISC e RISC – Forme di parallelismo, pipelining,

architetture superscalari – La memoria centrale, organizzazione interna, ordinamento dei dati –

Codici a rilevazione e correzione di errore – Gerarchie di memoria, memorie cache – Dischi

magnetici, dischi IDE, EIDE, Serial ATA e SCSI – Dischi RAID – Dischi ottici, CD ROM, DVD, DVD

Blue ray – Monitor e Display Flat-Panel – Terminali a mappa di caratteri e di bit – Stampanti ink-jet

e laser – Tastiere e mouse – Modem – Modem ADSL– Codifica di caratteri, codici ASCII e

UNICODE.

Logica digitale, memorie, microprocessori e bus.

Richiami sull’algebra booleana, porte logiche – Circuiti logici di base: multiplexer, decodificatori,

comparatori, PLA – I circuiti dell’Unità Aritmetico Logica, latch, flip-flop, registri, addizionatori –

Memoria centrale e sua organizzazione interna – Matrici di selezione bidimensionali – RAM

statiche e dinamiche, ROM, EPROM, memorie flash – Chip di memoria e schede di memoria,

SIMM e DIMM – Memorie SDRAM e DDR – Memorie Dual Channel – Dischi allo sto solido (SSD).

Bus e microprocessori

Architettura a bus – Prestazioni dei bus – Tipologie di bus: paralleli, seriali, sincroni ed asincroni –

Standardizzazione dei bus – Protocolli di bus sincroni ed asincroni – Arbitraggio dei bus – Pinout

del microprocessore – Esempi di microprocessori, il Pentium 4 – Architettura della piattaforma Intel

– Evoluzione della piattaforma Intel: Northbridge e Southbridge – Bus PCI, PCIMCIA, PCI Express

– Bus USB e USB 2, specifiche e struttura dei frame – Gestione delle interruzioni.

Microarchitetture, cache e pipeline.

La microarchitettura, il cammino dei dati – Ciclo di esecuzione delle microistruzioni – Accesso alla

memoria – Formato delle microistruzioni – La sezione di controllo – Memorie cache, memorie

associative pure, a mappa diretta, associative ad insiemi – Gestione della cache in lettura e

scrittura – Pipeline e architetture superscalari – Gestione dei salti, previsione statica e dinamica –

Esecuzione in-order e out-of-order – Microarchitettura del Pentium 4 – La microarchitettura

NetBurst – Architetture multi-core.

Il livello delle istruzioni macchina.

Registri, Program Status Word e modello della memoria – Il livello ISA del Pentium 4 – Formato

delle istruzioni – Espansione dei codici operativi – Formato delle istruzioni nel Pentium 4 – Modalità

di indirizzamento – Indirizzamento a stack – Ortogonalità – Gestione dell’I/O, I/O programmato, con

interruzioni e DMA – Repertorio di istruzioni del Pentium 4 – Gestione delle trap e delle interruzioni

- Architetture a 64 bit.

Traduzione e collegamento

Linguaggi macchina e linguaggi ad alto livello – Traduttori: interpreti compilatori ed assemblatori –

Linguaggi assemblativi – Istruzioni e pseudoistruzioni – Macro, macro con parametri procedure –

Funzionamento degli assemblatori – Assemblatori a due passate – Struttura del modulo oggetto –

Collegamento e aggiornamento degli indirizzi – Collegamento dinamico – Librerie DLL.

Sistemi di numerazione binaria.

Numeri e numerali – Rappresentazioni a precisione finita – Sistemi di numerazione posizionale –

Conversioni di base, binario, decimale esadecimale – Rappresentazione degli interi negativi,

notazioni in complemento a uno e a due, in eccesso 2e e relative conversioni – Addizioni e

moltiplicazioni fra interi – Rappresentazioni in virgola mobile, overflow, underflow – Addizioni e

moltiplicazioni in virgola mobile – Lo standard IEEE 754, numeri denormalizzati – Stima dell’errore

assoluto e relativo

RIFERIMENTI

A.S. Tanembaum, Architettura dei computer: un approccio strutturato, 5a Ed., Pearson Italia

2006.

Materiale distribuito dal docente

Materiale didattico in formato elettronico

Copia delle trasparenze, testi di esercizi di esame ed altro materiale didattico sono disponibili

all’indirizzo:

http://www.dis.uniroma1.it/~salza/FI-architetture.htm