Microprocessori

- Il microprocessore (μP) rappresenta la forma tecnologicamente più evoluta e

miniaturizzata dell' unità centrale di elaborazione (CPU: central processing unit):

è infatti una CPU integrata in un unico chip.

Il microcontrollore (μC) è un sistema di elaborazione costituito da un μP, memorie

e unità di ingresso/uscita (I/O), realizzato anch’esso in un unico circuito

integrato.

- Fra i parametri che caratterizzano un μP si possono distinguere: la frequenza del

clock (anche superiore al GHz), che determina la velocità di elaborazione; il

parallelismo ossia la larghezza della parola di dati (4, 8, 16,..., 64 bit); la capacità

di indirizzamento ossia il numero n di bit costituenti l’indirizzo (con n bit si

possono indirizzare 2n locazioni).

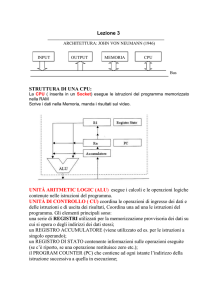

- Il struttura di un μP comprende essenzialmente: la ALU (unità aritmetico-logica), in

grado di eseguire operazioni aritmetiche e logiche; il contatore di programma (PC:

program counter), che contiene l’indirizzo dell’istruzione da prelevare ed

eseguire; il registro di stato (SR: status register), in cui vengono memorizzati i

bit di flag conseguenti un’operazione aritmetica o logica; il puntatore di stack

(SP: stack pointer), che punta alla cima dello stack (pila); i registri di lavoro, il cui

impiego è essenziale nella programmazione; l’unità di controllo, che provvede alla

decodifica delle istruzioni e alla temporizzazione dei segnali del μP. Tutte queste

parti sono interconnesse dal bus dei dati, dal bus degli indirizzi e dal bus di

controllo.

- L’elaborazione di una istruzione prevede una fase di prelievo o fetch, in cui il μP

preleva il codice operativo dell'istruzione dalla memoria, una fase interna al μP di

decodifica ed una fase di esecuzione (execute) nella quale il μP può compiere

operazioni: di lettura e scrittura in memoria, oppure di lettura e scrittura in

dispositivi di I/O, oppure interne alla CPU

oppure ancora di risposta a

segnalazioni esterne (richieste di interruzione e richieste di controllo dei bus).

- L’intervallo temporale in cui si svolge un’istruzione costituisce il ciclo istruzione.

Questo si compone di uno o più cicli macchina, dei quali il primo, sempre presente,

è il ciclo di lettura del codice operativo. Ogni ciclo macchina è costituito a sua

volta da un certo numero di cicli di clock.

- Il μP Z80 presenta un parallelismo di 8 bit dati con 16 linee indirizzo (64 kbyte di

memoria indirizzabili) ed una frequenza massima di clock di 8 MHz. Dispone di

due banchi di registri di lavoro (A accumulatore, B e C, D e E, H e L) e di ben 158

istruzioni. La tensione di alimentazione è +5V.

- I terminali dello Z80, in contenitore DIP, sono 40; oltre alle linee dati (D0 - D7) e

alle linee indirizzi (A0 - A15) si segnalano le seguenti linee (tutte attive basse):

- M1: è attivo (basso) nel primo ciclo macchina (CM1) in corrispondenza della

lettura del codice operativo (fase di fetch);

- MREQ: segnala attivandosi una operazione di lettura o di scrittura in memoria;

- IORQ: segnala una operazione di lettura o di scrittura in un dispositivo di I/O;

- RD: segnale un’operazione di lettura;

- WR: segnala una operazione di scrittura;

- RFSH: viene attivato insieme con MREQ durante il ciclo di rinfresco delle

memorie dinamiche in CM1.

- INT: segnala una richiesta di interruzione mascherabile da programma;

- NM1: segnala una richiesta di interruzione non mascherabile;

- RESET: inizializza il μP partendo dalla locazione 00H;

- BUSREQ: segnala la richiesta di un dispositivo esterno di gestire i bus dati e

indirizzi;

- BUSACK: segnala che il μP ha lasciato la gestione dei bus al dispositivo esterno.

- Dall’esame dei diagrammi di temporizzazione dello Z80 si nota che nel ciclo di

prelievo, gli indirizzi vengono posti sul bus subito dopo il fronte di salita del primo

ciclo di clock T1, mentre MREQ e RD vengono attivati sul fronte di discesa di T1.

I dati forniti dalla memoria vengono letti in corrispondenza del fronte di salita di

T3 e perciò devono risultare stabili prima di questo istante (tempo di set-up).

Nei cicli di lettura in memoria e nei dispositivi di I/O la lettura dei dati avviene

invece sul fronte di discesa di T3.

Nel ciclo di scrittura MREQ viene ancora attivata sul fronte di discesa di T1

mentre WR è attivata sul fronte di discesa di T2. I dati sono resi disponibili con

un certo ritardo rispetto al fronte di discesa di T1 ma con un certo anticipo

rispetto all’attivazione di WR.

- Le istruzioni sono espresse come una successione codificata di bit (codice

macchina); esse contengono sempre un codice operativo, che indica al μP le

operazioni da eseguire e, solitamente, uno o due operandi. Codice operativo e

operandi possono occupare la stessa locazione di memoria o più facilmente

locazioni successive.

Per facilitare il programmatore le istruzioni sono espresse in linguaggio

mnemonico o assembly. L’assembler o assemblatore è un programma che consente

di tradurre le istruzioni dalla forma mnemonica al linguaggio macchina.

- Il metodo di indirizzamento può essere implicito, immediato, diretto da memoria o

da registro, indiretto da memoria o da registro, relativo, indicizzato. Ad esempio

l’istruzione NEG (rendi negativo il contenuto dell’accumulatore ) è di tipo

implicito;

LD A, 22H (carica nell’accumulatore il dato esadecimale 22) è di tipo immediato;

LD A, B (carica in A il contenuto del registro B) è diretta da registro;

LD A, (4000H) (carica in A il contenuto della locazione 4000) è diretto da

memoria;

LD A, (HL) (carica in A il contenuto della locazione il cui indirizzo è contenuto nel

registro HL) è di tipo indiretto da registro.

- Le istruzioni, con riferimento allo Z80, possono essere del seguente tipo: di

trasferimento o caricamento, di trasferimento e ricerca di gruppo, aritmetiche e

logiche, di controllo della CPU, di rotazione o scorrimento, di manipolazione di bit,

di salto, di chiamata e ritorno, di ingresso e uscita.

- Il trasferimento dei dati fra CPU e dispositivi di I/O può avvenire essenzialmente

secondo tre modalità:

- Trasferimento iniziato dalla CPU, in cui lo scambio dei dati è controllato dalla

CPU e quindi dal programma;

- Trasferimento pilotato da interruzione, in cui ad innescare il trasferimento è il

dispositivo di I/O, che invia alla CPU un segnale di interruzione;

- DMA o accesso diretto alla memoria (direct memory access), in cui il

trasferimento dei dati fra memoria e periferiche avviene direttamente senza

transitare attraverso la CPU, che sospende momentaneamente la sua attività.