P10 – CONVERTITORI A/D E D/A

P10.1 – Calcolare l’intervallo di quantizzazione LSB, la risoluzione R e

l’errore massimo di quantizzazione ε di un convertitore A/D con n = 8 bit di

uscita e valore massimo della tensione d’ingresso Vmax = 4 V. Stabilire inoltre

come si modificano i risultati nei due casi in cui si raddoppi il valore

rispettivamente di Vmax o di n. Valutare infine il rapporto segnale/rumore di

quantizzazione del convertitore in esame.

Soluzione

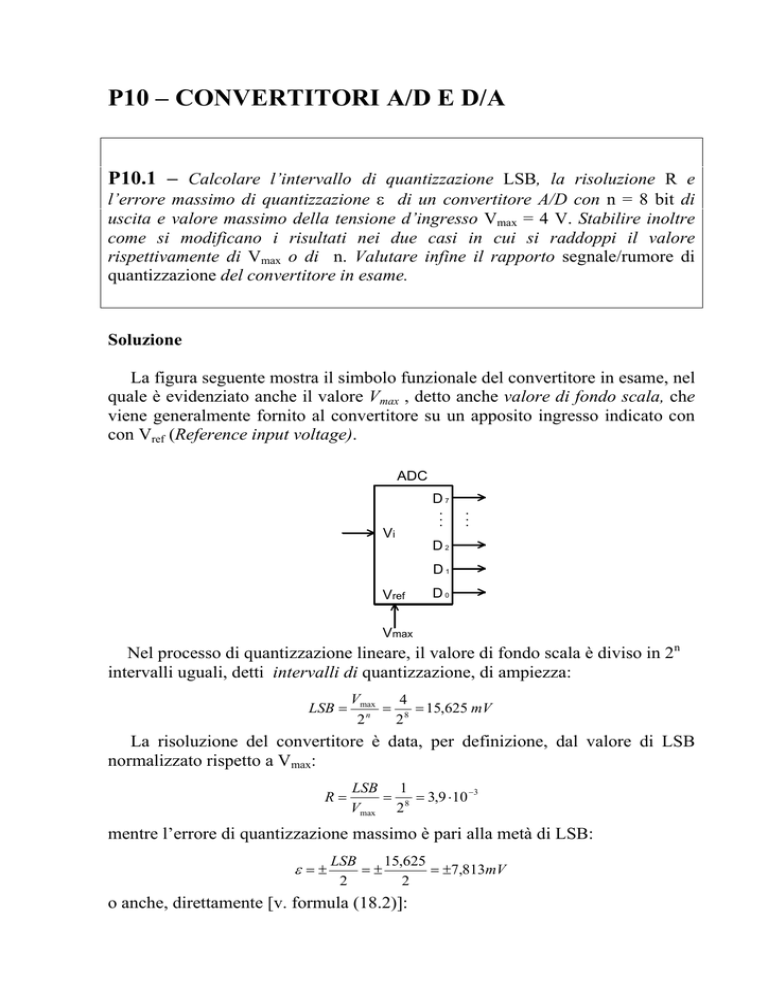

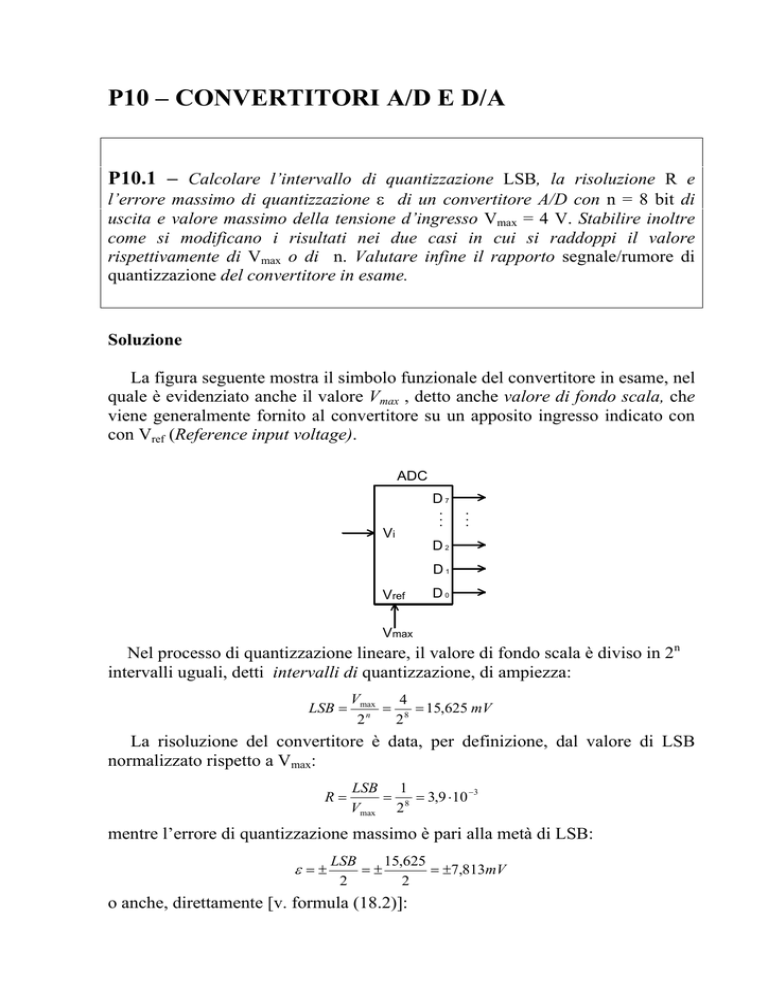

La figura seguente mostra il simbolo funzionale del convertitore in esame, nel

quale è evidenziato anche il valore Vmax , detto anche valore di fondo scala, che

viene generalmente fornito al convertitore su un apposito ingresso indicato con

con Vref (Reference input voltage).

ADC

Vi

D7

..

.

..

.

D2

D1

Vref

D0

Vmax

Nel processo di quantizzazione lineare, il valore di fondo scala è diviso in 2n

intervalli uguali, detti intervalli di quantizzazione, di ampiezza:

LSB =

Vmax

4

= 8 = 15,625 mV

n

2

2

La risoluzione del convertitore è data, per definizione, dal valore di LSB

normalizzato rispetto a Vmax:

R=

LSB 1

= 8 = 3,9 ⋅10 −3

Vmax 2

mentre l’errore di quantizzazione massimo è pari alla metà di LSB:

ε =±

LSB

15,625

=±

= ±7,813mV

2

2

o anche, direttamente [v. formula (18.2)]:

ε =±

Vmax

4

= ± 9 = ±7,813 mV

n +1

2

2

Se si raddoppia il valore di fondo scala, raddoppiano anche i valori di LSB e

di ε, mentre se si raddoppia il numero di bit del codice di uscita si ha una

drastica riduzione di LSB e di ε, nel rapporto di 2n. Nel primo caso si ha dunque:

LSB ' =

ε '= ±

2Vmax 2 × 4

= 8 = 31,25 mV

2n

2

LSB'

31,25

=±

= ±15,625 mV

2

2

e nel secondo caso:

LSB" =

ε"=

Vmax 15,625

=

= 61 µV

2 2n

216

LSB" 61

=

= 30,5 µV

2

2

Per quanto riguarda il rapporto segnale/rumore di quantizzazione, esso vale,

in base alla (18.3):

S / N q = 6 × 8 = 48 dB

nel caso di codice a 8 bit, e sale a 48 × 2 = 96 dB se si raddoppia il numero di bit

del codice di uscita, indipendentemente dal valore della tensione di fondo scala.

______________________________________________________________

P10.2 – Determinare il numero binario all’uscita di un convertitore A/D con

n = 8 bit e valore di fondo scala Vmax = 2 V, quando il segnale analogico in

ingresso vale Vi = 1,3 V.

Soluzione

Il valore del numero N in uscita, nell’ipotesi di codice binario naturale a 8

bit, è determinato dal rapporto tra il valore della tensione Vi d’ingresso e il valore

dell’intervallo di quantizzazione LSB. In formula:

V

N = INT ≅ i

LSB

dove la notazione INT ≅ (x) indica il numero intero più vicino a x.

Nel nostro caso si ha:

LSB =

Vmax

2

= 8 = 7,8125mV

n

2

2

e quindi:

1,3

N = INT ≅

= 166 = (10100110) 2

−3

7,8125 ⋅10

Ricordiamo la regola pratica per ottenere l’espressione binaria di un numero

decimale: si procede per successive divisioni per 2 e si segna 1 in

corrispondenza dei risultati dispari, e 0 in corrispondenza di quelli pari:

166 83

0

1

(LSB)

41

1

20 10

0

0

5

1

2

0

1

1

(MSB)

P10.3 – Utilizzando l’integrato 8-Bit A/D Converter ADC0802, di cui è fornito

il data sheet pag.607 del testo, si vuole convertire in numerico un segnale

analogico avente uno spettro di frequenza compreso nella banda fonica f1 ÷ f2 =

300 ÷ 3400 Hz. Stabilire se è necessario anteporre al convertitore un circuito

Sample and Hold (campiona e mantieni) ed eventualmente valutare il relativo

tempo di acquisizione.

Soluzione

Dal data sheet si desume per il tempo di conversione un valore massimo Ts

= 100 µs. Con tale valore, la massima frequenza che il convertitore a 8 bit

assegnato può convertire senza l’impiego del circuito S&H è data, in base alla

(18.4), da:

f max =

1

2 ⋅ π ⋅ Ts

n

=

1

= 12,43 Hz

2 ⋅ π ⋅100 ⋅10 −6

8

Essendo f max << 3400 Hz, l’impiego del circuito S&H è assolutamente

necessario.

Il tempo di acquisizione massimo Ta di tale circuito (= tempo di carica del

condensatore di memoria, con una tolleranza prestabilita) deve essere minore del

tempo di conversione Ts , e può essere determinato in base alla seguente

relazione, derivata dalla (18.4):

Ta ≤

1

2 ⋅π ⋅ f 2

n

=

1

= 0,4 µS

2 ⋅ π ⋅ 3400

8

____________________________________________________________

P10.4 - Calcolare l’intervallo di quantizzazione LSB di un convertitore A/D

flash a n=3 bit, per un valore della tensione di fondo scala Vmax = 4V.

Dimensionare il partitore di tensione per il prelievo delle tensioni di soglia e

determinare i valori di tali livelli di tensione ricavati dalla tensione di

riferimento del convertitore.

Soluzione

L’intervallo di quantizzazione è dato dal prodotto della tensione Vmax per la

risoluzione del convertitore. Quest’ultima, per n=3bit, vale:

Ris =

1 1

= = 0,125

23 8

pertanto si ottiene:

LSB = Ris ⋅ Vmax = 0,125 × 4 = 0,5 V

Dalla tensione di fondo scala, coincidente con la tensione di riferimento del

convertitore, si ricavano, mediante un partitore composto da 8 resistori, le 7

tensioni di soglia con le quali viene confrontata la tensione analogica d’ingresso

Vi , tramite altrettanti comparatori.

Il partitore di tensione è formato da un resistore finale di resistenza R, da un

resistore iniziale di resistenza 3R e da sei resistori intermedi di resistenza 2R.

Scegliendo per il resistore finale:

R = 1 kΩ

il resistore iniziale e quelli intermedi devono valere rispettivamente 3 kΩ e

2 kΩ.

Per quanto riguarda i livelli di tensione ottenuti dal partitore, i rispettivi valori

sono dati in successione dalla relazione:

x Vref / 2 n+1 , con x = 1,3,5, ... , (2 n+1 − 3)

che fornisce un primo valore pari alla metà del passo di quantizzazione:

Vref / 2 3+1 = 4 / 16 = 0,25 ≡ LSB / 2

un secondo valore incrementato di 1 LSB;

3 Vref / 2 3+1 = 13 × 4 / 16 = 0,75 V

e così via fino al settimo livello:

(2 3+1 − 3) Vref / 2 3+1 = 13 × 4 / 16 = 3,25 V

P10.5 – Calcolare il rapporto segnale/rumore di quantizzazione di un

convertitore A/D parallelo e di un convertitore A/D sigma-delta, aventi

risoluzione pari rispettivamente a:

R flash = 4 ⋅10 −3 ; RΣ∆ = 1,5 ⋅10 −5

Soluzione

La risoluzione di un convertitore A/D è legata al numero di bit del codice in

uscita dalla relazione (18.1):

R = LSB / Vmax = 1 / 2 n

Per i due convertitori assegnati si ha pertanto:

n flash = log 2

1

R flash

= − log 2 R flash = − log 2 (4 ⋅10 −3 ) = 8 bit

nΣ∆ = − log 2 RΣ∆ = − log 2 (1,5 ⋅10 −5 ) = 16 bit

Corrispondentemente, applicando la formula approssimata (18.3), si

ottengono i seguenti valori del rapporto segnale/rumore di quantizzazione:

( S / N q ) flash = 6 × 8 = 48 dB

( S / N q ) Σ∆ = 6 ×16 = 96 bit

Si vede dunque che il raddoppio del numero di bit di uscita da 8 a 16, reso

possibile dall’introduzione della tecnica sigma-delta, comporta un aumento di 48

dB del rapporto segnale/rumore di quantizzazione, vale a dire una potenza del

rumore di quantizzazione oltre sessantamila volte più piccola.

P10.6 – Verificare se un segnale analogico variabile nel tempo con una

velocità massima (dvi/dt)max = 0,5 mV/µs può essere correttamente convertito in

digitale mediante un ADC a 12 bit, privo di circuito S&H, avente un tempo di

conversione di 10 µs ed una escursione d’ingresso di ±10 V.

Soluzione

Nei convertitori che accettano in ingresso segnali bipolari, in luogo del valore

di fondo scala va considerato il range di ingresso FSR (Full-Scale Range), per

determinare l’intervallo di quantizzazione:

1 LSB =

FSR Vi max − Vi min

=

2n

2n

Nel nostro caso si ottiene:

1 LSB =

10 − (−10) 20

= 12 = 4,88 mV

212

2

In assenza di un circuito di Sample and Hold , in grado di acquisire il valore

della tensione di ingresso in un determinato istante e mantenerlo invariato

sull’uscita fino ad un nuovo campionamento, la conversione A/D di un segnale

variabile nel tempo richiede che durante il tempo di conversione Ts il segnale

non subisca una variazione superiore in valore assoluto a 1 LSB.

Nel nostro caso la massima variazione della tensione in ingresso, espressa in

mV, vale;

∆Vi max = (dvi / dt ) max ⋅ Ts = 0,5 ×10 = 5 mV

Poiché risulta ∆Vi max > 1 LSB , l’ADC assegnato non è idoneo ad eseguire

correttamente la conversione richiesta.

P10.7 – Un convertitore D/A ad 8 bit ha una tensione di uscita compresa fra 0

e 5V. Calcolare i valori della risoluzione e del LSB del convertitore, e

determinare il valore della tensione ottenuta in uscita in corrispondenza del

codice in ingresso 01100110.

Soluzione

In figura è rappresentato il simbolo funzionale del convertitore D/A

assegnato, con l’indicazione dell’ingresso di riferimento.

DAC

0

B3

1

B2

1

B1

0

B4

0

B3

1

B2

1

B1

0

B 0 Vref

Vu

+5V

La risoluzione del convertitore dipende esclusivamente dal numero di bit del

codice d’ingresso e vale, in base alla (19.1):

1

1

= 8

= 3,92 ⋅ 10 −3

2 −1 2 −1

R=

n

ovvero percentualmente:

R% =

100

= 0,392 %

2n −1

Il passo di quantizzazione si ottiene moltiplicando la variazione massima

della tensione di uscita per il valore della risoluzione:

LSB = Vmax R = 5 × 3,92 ⋅10 −3 = 19,6 mV

Per determinare la tensione di uscita del DAC in corrispondenza di una

determinata combinazione del codice di ingresso, nell’ipotesi di codifica in

binario puro a 8 bit, basta moltiplicare per LSB il valore numerico della

combinazione di codice assegnata:

(01100110) 2 = (102)10

Quindi:

Vu = 102 ⋅ LSB = 102 × 19,6 ⋅10 −3 ≅ 2 V

Ricordiamo la regola pratica per convertire in decimale un numero binario: si

procede per successive moltiplicazioni per 2 dei singoli bit, a partire da quello

più significativo, aggiungendo ogni volta il bit successivo. Nel nostro caso:

0

1

1

0

0

1

1

0

→ 3→ 6→12→25→51→102

P10.8 – In un DAC a n = 4 bit del tipo a resistenze pesate con R = 2 kΩ, la

tensione di riferimento, generata internamente al convertitore, è Vr = 5 V.

Calcolare la tensione di uscita in corrispondenza della combinazione di codice

in ingresso:

B3 B2 B1 B0 = 0 1 0 1

Soluzione

In figura è riportato lo schema di principio del DAC in esame, con gli switch

elettronici posizionati secondo la combinazione di codice assegnata.

R

16 R

8R

2R

4R

+

Vu

GND

0

1

Vr

0

1

LSB

MSB

GND

Poiché l’ingresso invertente dell’amplificatore operazionale è a massa

virtuale, la corrente Ii che scorre nell’i-esimo ramo della rete di pesatura quando

il corrispondente bit è a 1, vale:

Ii =

Vr

Ri

Nel nostro caso sono percorsi da corrente i resistori 16R e 4R, relativi

rispettivamente ai bit B0 e B2; pertanto la corrente totale vale:

I=

Vr

V

V

5×5

+ r = r (1 + 4) =

= 0,781 mA

16 R 4 R 16 R

16 × 2 ⋅ 103

Si osservi che 16 R=2n R e che 1+4=5 corrisponde al valore decimale N della

combinazione di codice in ingresso:

(0101) 2 = (5)10

L’espressione della I può pertanto essere generalizzata nella formula

seguente:

I=

NVr

2n R

La tensione in uscita dall’AO in configurazione invertente risulta:

Vu = − IR = −0,781 ⋅ 10 −3 × 2 ⋅ 103 = −1,562 V

e può dunque essere espressa dalla formula:

Vu = −

NVr

2n

che fornisce infatti:

Vu = −

5×5

25

=−

= −1,562 V

4

2

16

P10.9 – In un DAC a 4 bit del tipo a rete R-2R, realizzato secondo lo schema in

figura, si ha Vr=5 V, R= 4kΩ. Calcolare la corrente Ir fornita dal generatore

della tensione di riferimento. Determinare inoltre la tensione Vu all’uscita del

convertitore in corrispondenza della combinazione di codice in ingresso:

B3 B2 B1 B0 = 0 1 1 1

I3

Vr

R

I3

R

I1

I2

R

I0

I1

I0

2R

2R

2R

2R

0

1

1

1

MSB

GND

Soluzione

I2

2R

R

GND

LSB

+

GND

Vu

Si ha Ir=2 I3 , con I3 =Vr/2R, indipendentemente dalla posizione degli

interruttori della rete R-2R, dato che l’ingresso invertente dell’AO è a massa

virtuale.La corrente erogata dal generatore dell tensione di riferimento vale

dunque:

Ir = 2

Vr Vr

5

=

=

= 1,25 mA

2 R R 4 ⋅ 103

Con la combinazione di codice assegnata, la corrente all’ingresso invertente

dell’AO è espressa da:

I = I 2 + I1 + I 0 =

Ir Ir Ir Ir

7

7 Vr

+ +

= (4 + 2 + 1) = I r =

4 8 16 16

16

16 R

e la tensione all’uscita del convertitore risulta:

Vu = − RI = −

7

7

Vr = − 5 = −2,1875

16

16

Osservando che i numeri 16 e 7 corrispondono rispettivamente a 2n e al

valore decimale N della combinazione di codice assegnata:

(0111) 2 = (7)10

l’espressione della Vu può essere generalizzata scrivendo:

Vu = −

NVr

2n

come nei convertitori a resistenze pesate.

Da tale relazione si vede che il valore R della rete R-2R non influenza

direttamente la risposta del convertitore. E’ necessario però che esso sia

rispettato da tutti i resistori della rete, con la stessa precisione e con lo stesso

coefficiente di temperatura.

P10.10 – Determinare la risposta analogica di un convertitore D/A ad 8 bit nel

caso in cui sull’ingresso di riferimento venga posto il segnale:

vr = 4 sen 2π ⋅ 103 t

mentre sugli ingressi binari è applicata la combinazione di codice 10100000.

Soluzione

La relazione generale che lega la risposta analogica di un DAC alla tensione

di riferimento (v. Problema precedente), è valida anche se quest’ultima ha valore

variabile nel tempo. Possiamo pertanto scrivere, riferendoci ai valori istantanei:

vu = −

ovvero, nel nostro caso:

vu = −

N vr

2n

160 vr

= −0,625 vr

28

essendo N=160 il valore decimale della combinazione di codice ad 8 bit

assegnata:

(10100000) 2 = (160)10

Sostituendo abbiamo:

vu = −0,625 × 4 sen 2π ⋅ 103 t = −2,5 sen 2π ⋅ 103 t

cioè l’uscita del convertitore è una tensione sinusoidale, come quella applicata

all’ingresso di riferimento, avente la stessa frequenza (1 kHz), di fase opposta e

con ampiezza moltiplicata per N/2n = 0,625.

I convertitori D/A integrati destinati a funzionare con tensione di riferimento

variabile vengono detti multiplying DAC, poiché la loro uscita risulta

proporzionale al prodotto fra la tensione di riferimento ed il numero N presente

sugli ingressi digitali. La loro applicazione tipica è nella realizzazione di

amplificatori a controllo digitale, nei quali il segnale da amplificare viene

applicato all’ingresso di riferimento del convertitore, ed il guadagno viene

regolato cambiando la combinazione di codice sugli ingressi digitali.