Elementi di informatica

Architetture degli elaboratori

Il calcolatore

? Un calcolatore è sistema composto da un elevato

numero di componenti

? Il suo funzionamento può essere descritto se lo si

considera come un sistema strutturato in forma

gerarchica

? Ogni componente ha una sua funzione

1

Funzionalità di un calcolatore

Codifica dell'Informazione

3

Funzionalità di un calcolatore:

elaborazione

?Flessibilità

Adatta a svolgere diverse tipologie di compiti

?Modularità

Ogni componente ha una funzione specifica

?Scalabilità

Ogni componente può essere sostituito con uno

equivalente

?Standardizzazione

Componenti facilmente sostituibili in caso di

malfunzionamento

?Riduzione dei costi

Grazie alla produzione su larga scala

?Semplicità

Di installazione ed esercizio del sistema

2

Funzionalità di un calcolatore:

memorizzare dati

la memorizzazione dei dati:

? per brevi periodi (i risultati di operazioni

intermedie)

? per lunghi periodi (archivi elettronici che

sostituiscono quelli cartacei)

Funzionalità di un calcolatore:

trasferimento dati

Trasferimento dei dati:

? Comunicazione con l’ambiente esterno;

? Uso di dispositivi ausiliari “periferiche” che

svolgono operazioni di ingresso uscita.

3

Funzionalità di un calcolatore:

controllo

L’utente la realizza impartendo comandi al

calcolatore

Il calcolatore coordina le risorse al fine di

svolgere le operazioni corrispondenti ai

comandi

Il modello concettuale

4

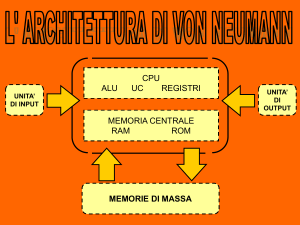

Il modello architetturale

L’architettura di riferimento

? Il componente principale è l’unità di

elaborazione centrale (central

( central processing unit

unit,,

CPU,, processore

CPU

processore)) a cui sono affidate le

operazioni di controllo e coordinamento;

? Per la memorizzazione dei dati è presente una

memoria (indirizzo);

? Il collegamento tra queste unità è realizzato da

un bus (master(master -slave)

5

Lo schema di riferimento

Lo schema di riferimento

RAM

CPU

Scheda madre

(motherboard

)

Bus dati

Bus

indirizzi

Bus di

controllo

Interfacce

di I/O

Interfaccia di

I/O

Schermo

Tastiera e

mouse

Altoparlanti

Interfacce

di I/O

Memoria di massa

6

Scheda madre

Connettori per

schede di I/O

aggiuntive

Zoccolo per

la CPU

Connettori

per la

memoria

Connettori per

dischi fissi

Caratteristiche del collegamento al Bus

? Semplicità

un’unica linea di connessione ? costi ridotti di produzione

? Estendibilit

Estendibilità

à

aggiunta di nuovi dispositivi molto semplice

? Standardizzabilit

Standardizzabilità

à

regole per la comunicazione da parte di dispositivi diversi

? Lentezza

utilizzo in mutua esclusione del bus

? Limitat

Limitatà

à capacit

capacità

à

al crescere del numero di dispositivi collegati

? Sovraccarico del processore (CPU)

perché

perch

é funge da master sul controllo del bus

7

Il bus

Il bus può essere suddiviso in tre componenti

? Bus dati

? Bus indirizzi

? Bus di controllo

L’esecutore

Un calcolatore esegue un programma sulla

base dei seguenti principi:

? Dati e istruzioni in memoria;

? I contenuti della memoria sono indirizzabili

in base alla posizione;

? Le istruzioni vengono eseguite in modo

sequenziale;

8

Tre tipologie di istruzioni

? Istruzioni aritmetico

aritmetico--logiche (Elaborazione dati)

Somma, Sottrazione, Divisione, ..

And, Or, Xor

Xor,….

,….

Maggiore, Minore, Uguale,…

? Controlo del flusso delle istruzioni

Sequenza

Selezione semplice, a due vie, a n vie, …

Ciclo a condizione iniziale, ciclo a condizione finale,..

? Trasferimento di informazione

Trasferimento dati e istruzioni tra CPU e memoria

Trasferimento dati e istruzioni tra CPU e dispositivi di

ingresso/uscita (attraverso le relative interfacce)

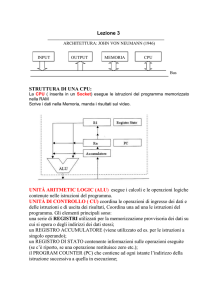

Elementi di una CPU

?Unità di controllo

legge le istruzioni dalla memoria e ne determina il tipo

?Unità aritmetico logica

esegue le operazioni necessarie per eseguire le istruzioni

?Registri

memoria ad alta velocità usata per risultati temporanei e

informazioni di controllo;

il valore massimo memorizzabile in un registro è determinato

dalle dimensioni del registro;

esistono registri di uso generico e registri specifici;

9

I registri sempre presenti:

PC (Program Counter

Counter)) indica la prossima istruzione da

eseguire

IR (Instruction Register) contiene una copia dell’istruzione

da eseguire

MAR (Memory Address Register

Register)) contiene l’indirizzi di

memoria dove estrarre il dato

MDR (Memory

(Memory Data Register

Register)) contiene una copia del dato

estratto dalla memoria

PSW (Processor

( Processor Status Word) codifica sullo stato di

esecuzione dell’istruzione

Struttura del data path

10

Struttura della CPU

Esecuzione delle istruzioni

Ciclo Fetch

Fetch--Decode

Decode--Execute

(leggi

leggi--decodifica

decodifica--esegui

esegui))

1. Prendi l’istruzione corrente dalla memoria e mettila nel

registro istruzioni(IR);

istruzioni(IR);

2. Incrementa in program counter (PC) in modo che contenga

l’indirizzo dell’istruzione successiva;

3. Determina il tipo dell’istruzione corrente (decodifica)

(decodifica);;

4. Se l’istruzione usa una parola in memoria determina dove si

trova;

5. Carica la parola se necessario, in un registro della CPU;

6. Esegui l’istruzione.

7. Torna al punto 1 e inizia a eseguire l’istruzione successiva;

11

Il clock

Le varie unità operano in modo coordinato dal punto di vista

della temporizzazione degli eventi.

Un orologio (clock) fornisce una cadenza temporale a cui tutte

le attività elementari sono sincronizzate

La frequenza di clock è il numero di attività elementari

nell’unità di tempo (Mhz)

Concorre a determinare la velocità di elaborazione

Evoluzione delle CPU

12

La memoria

Supporto alla CPU: deve fornire alla CPU dati e istruzioni il

più rapidamente possibile;

Archivio: deve consentire di archiviare dati e programmi

garantendone la conservazione e la reperibilità anche dopo

elevati periodi di tempo

Diverse esigenze:

?Velocità: per il supporto alla CPU

?Non volatilità ed elevate dimesioni per l’archivio

Diverse tecnologie

?Elettronica: veloce ma costosa e volatile

?Magnetica e ottica non volatile ed economica, ma molto

lenta

Criteri di caratterizzazione di una

memoria

Velocità

?Tempo di accesso (quanto passa tra una richiesta e la relativa risposta)

?Velocità di trasferimento (quanti byte al secondo si possono trasferire)

Volatilità

?Cosa succede quando la memoria non è alimentata?

?Per quanto tempo i dati vi rimangono memorizzati?

Capacità

?Quanti Byte può contenere? Qual è la dimensione massima?

Costo

(per bit)

Modalità di accesso

?Diretta (o casuale): il tempo di accesso è indipendente dalla posizione

?Sequenziale: il tempo di accesso dipende dalla posizione

?Mista: combinazione dei due casi precedenti

13

La memoria centrale (RAM)

Mantiene al proprio interno i dati e le istruzioni

dei programmi in esecuzione

Memoria ad accesso “casuale”

Tecnologia elettronica:

Veloce ma volatile e costosa

Due “eccezioni”

R.O.M. elettronica ma permanente e di sola lettura

Flash: elettronica ma permanente e riscrivibile

Indirizzi di memoria

I bit nelle memorie sono raggruppati in celle:

?Tutte le celle sono formate dallo stesso numero di bit;

?Una cella composta da K bit, è in grado di contenere una

qualunque tra 2k combinazioni diverse di bit;

Ogni cella ha un indirizzo:

?Serve come accesso all’informazione;

?In una memoria con N celle gli indirizzi vanno da 0 a N-1;

La cella è l’unità indirizzabile più piccola.

In quasi tutti i calcolatori è di 8 bit (un byte).

I byte vengono raggruppati in parole (che oggi sono di 32/64

bit), su cui la CPU esegue le operazioni.

14

Organizzazione della memoria

Anche gli indirizzi della memoria sono rappresentati come

numeri binari.

Un indirizzo di M bit consente di indirizzare 2M celle;

Per 6 o 8 celle bastano 3 bit, per 12 celle ne servono 4;

Il numero di bit nell’indirizzo determina il numero massimo di

celle indirizzabili nella memoria ed è indipendente dal

numero di bit per cella (una memoria con 212 celle richiede

sempre 12 bit di indirizzo, quale che sia la dimensione di una

cella).

La memoria può essere organizzata in diversi modi;

Con 96 bit possiamo avere 6 celle di 16 bit (6*16=96), o 8

celle di 12 bit (8*12=96) o 12 celle di 8 bit (12*8=96).

15

Memoria e collegamenti con

bus

•

•

•

Viene selezionata la

parola di indirizzo

0110 due

il contenuto è

01101100;

l’operazione è di

lettura (load) o di

scrittura (store ) a

seconda dei comandi

presenti sul bus di

controllo

0110

Bus indirizzi

D ECODIFICATORE

linee di

selezione parola

linea 0

0

linea 1

0

linea 2

0

linea 3

0

linea 4

0

linea 5

0

linea 6

1

linea 7

0

linea 8

0

linea 9

0

linea 10

0

linea 1 1

0

linea 1 2

0

linea 13

0

linea 14

0

linea 15

0

16 celle di memoria

di 8 bit ciascuna

0

1

1

0

1

1

0

0

0

1

1

0

1

1

0

0

parola

selezionata

leggi/scrivi

Bus di

controllo

Dato

(letto o da scrivere)

Bus dati

Memoria vs. CPU

? Le CPU sono sempre state più veloci delle memorie

? l’aumento di integrazione ha consentito di realizzare

CPU pipeline e super scalari, molto efficienti e veloci;

? nelle memorie è aumentata la capacità più che la

velocità.

? L’accesso alla memoria passa attraverso il bus

? la frequenza di funzionamento del bus è molto più

bassa di quella della CPU;

? il bus può essere impegnato ad effettuare

trasferimenti controllati da dispositivi di I/O

“autonomi” (e.g. DMA).

? È difficile riordinare le istruzioni in modo da poter

sfruttare i tempi di attesa della memoria.

? È possibile fare memorie molto veloci se stanno nel

chip della CPU, ma sono piccole e costose.

16

Le memorie gerarchiche

Memorie di gran capacità, relativamente lente,

economiche ed accessibili tramite il bus:

? MGL ovvero Memoria Grossa e Lenta;

? dimensioni pari a circa 10 unità;

? tempo di accesso (TA) di circa 10 unità.

Memorie veloci, integrate nello stesso chip della CPU,

ma costose:

? MPV ovvero Memoria Piccola e Veloce;

? dimensioni pari a circa 1 unità;

? tempo di accesso pari a circa 1 unità.

Obiettivo: realizzare una memoria grossa e veloce

? dimensioni pari a circa quelle della memoria grossa;

? prestazioni pari a circa quelle della memoria veloce.

Una gerarchia di memoria

Memoria formata da una MPV e una MGL:

? la MPV contiene una copia di alcune celle della MGL;

? quando la CPU chiede una particolare cella di memoria

la richiesta va ad entrambe le memorie:

?se il dato si trova nella MPV, viene passato

direttamente alla CPU;

?se il dato si trova nella MGL, viene anche caricato

nella MPV.

Ipotesi: distribuzione uniforme delle richieste

? la frequenza con cui si trova il dato cercato nella MPV

(hit ratio) sarà in media il 10% (1/10), in questi casi

il tempo di accesso (hit time) sarà pari a 1 unità;

? la frequenza con cui è necessario accedere alla MGL

(miss ratio) sarà in media il 90% (9/10), in questi

casi il tempo di accesso (miss penalty) sarà pari a 10

unità;

? il tempo medio di accesso sarà 0.1*1+0.9*10=9.1

unità!

17

Gerarchia di memoria

Sistema di

memoria

CPU

Memoria piccola

e veloce

Livello 1

Trasferimento

di dati

Livello 2

Memoria grande

e lenta

Il principio di località

Località spaziale:

quando si accede all’indirizzo A, è molto probabile che gli

accessi successivi richiedano celle vicine ad A.

? le istruzioni del codice vengono in genere lette da locazioni

consecutive della memoria;

? gli accessi ad array o a strutture dati sono “vicini”.

Località temporale:

quando si accede all’indirizzo A, è molto probabile negli

accessi successivi si richieda di nuovo la cella A.

? cicli di istruzioni accedono ripetutamente alle stesse locazioni

di memoria;

? istruzioni vicine tendono ad utilizzare le stesse variabili.

18

Come si sfrutta la località

Diversi approcci a seconda del tipo di località:

? località temporale

temporale: i dati prelevati dalla MGL vengono

conservati nella MPV il più a lungo possibile;

? località spaziale

spaziale: quando si copia un dato dalla MGL

alla MPV, si copiano anche i dati vicini (cache line o

blocco).

La frequenza di successo (hit ratio – h) cresce fino a

superare il 99%:

? in effetti h dipende da due caratteristiche contrastanti:

?la dimensione dei blocchi

un blocco grande sfrutta meglio la località spaziale;

?quanti sono i blocchi in memoria

se c’è spazio per tanti blocchi un dato resta in

memoria più a lungo e può sfruttare più a lungo la

località temporale;

? c’è anche il problema del costo della cache!

L’effetto della località

Effetto del principio di località sull’esempio di prima:

? tempo di accesso alla cache pari a 1 unità (TA

TAC = 1);

1

? tempo di accesso alla memoria (detto anche miss

penalty, ovvero penalità di fallimento) pari a 10 unità

(TAM

TAM = 10);

10

? frequenza di successo (hit ratio, h = 0.99);

0.99

? frequenza di fallimento (miss ratio, m = 1 – h =

0.01);

0.01

? tempo di accesso medio pari a:

TA = h * TAC + m * TAM

TA = 0.99 * 1 + 0.01 * 10 = 1.09

19

Packaging

Fino all’inizio degli anni ‘90 la memoria veniva

prodotta, acquistata e installata su chip singoli

? densità variabili da 1 Kbit a 1 Mbit;

? i PC avevano zoccoli vuoti dove inserire altri chip.

Oggi si monta un gruppo di chip, tipicamente 8 o 16,

su un piccola scheda stampata che si vende come

unità minima installabile nei PC

? SIMM (Single Inline Memory Module) se la fila di

connettori si trova da un solo lato della scheda;

? DIMM (Dual Inline Memory Module) se i connettori

si trovano su ambedue i lati della scheda

Sia SIMM che DIMM sono a volte dotate di un codice di

rilevazione o di correzione dell’errore.

20