XV Master in Tecnologia dell’Informazione

Rapporto esame VLSI

Gestione dinamica del consumo

energetico nei sistemi embedded

Autore: Daniele Paolo Scarpazza

Tutor: Carlo Brandolese

Area: ESD

Sponsor: Carlo Brandolese S.p.A.

Febbraio 2003

Versione: 1.0

Stato: draft

Gestione dinamica del consumo energetico nei sistemi embedded

Diffusione del documento

La diffusione del presente documento è limitata al Centro CEFRIEL e

a Carlo Brandolese S.p.A. ed è di proprietà del CEFRIEL e di Carlo

Brandolese S.p.A.. Ogni riproduzione da parte di altri soggetti senza

esplicita autorizzazione è pertanto vietata a norma delle leggi vigenti.

Pagina i

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

Revisioni

Data

11 Febbraio 2003

Pagina ii

Versione

1.0

Stato

draft

Commento

Prima versione preliminare

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

Indice

1 Introduzione

1

2 Hardware e riduzione del consumo

2

2.0.1 Tecniche hardware di riduzione del consumo

. . . . . . . . . . . . . . . . . . .

2

2.0.2 Spegnimento selettivo . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2

2.0.3 Clock gating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3

2.0.4 Riduzione della frequenza di clock . . . . . . . . . . . . . . . . . . . . . . . . . .

3

2.0.5 Clock bursting / stop-clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4

2.0.6 Riduzione delle tensioni di alimentazione . . . . . . . . . . . . . . . . . . . . . .

4

2.0.7 Stati a consumo ridotto . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5

2.1 Vincoli, difficoltà, costi . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5

2.1.1 Latenze . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5

2.1.2 Tempi di risposta del VRM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5

2.1.3 Protocolli di snoop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6

3 Rassegna dei processori in produzione

7

3.1 Processori “Mobile” per PC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7

3.1.1 Intel Pentium 4-M . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7

3.1.2 Intel Pentium III-M . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9

3.1.3 AMD Athlon XP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11

3.1.4 Transmeta Crusoe TM5500 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12

3.2 Processori per sistemi embedded . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13

3.2.1 Intel 80200 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13

3.2.2 ARM1022E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14

3.2.3 Motorola MC68EZ328 DragonBall EZ . . . . . . . . . . . . . . . . . . . . . . . . . .

15

3.2.4 IBM PowerPC 405LP

16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Un esempio di framework DPM

18

4.1 Panoramica architetturale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18

4.2 Concetti fondamentali . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19

4.2.1 Operating point . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19

4.2.2 Operating state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19

4.2.3 Vincoli e classi di congruenza degli operating point . . . . . . . . . . . . . . . .

20

4.2.4 Policy e Policy manager

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21

4.3 Implementazione astratta . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21

4.3.1 set operating state() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22

4.3.2 assert constraint() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22

4.3.3 remove constraint() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22

4.3.4 set policy() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22

Pagina iii

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

4.3.5 set task state() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22

4.4 Conclusioni . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23

5 Argomenti di ricerca

24

5.1 Riduzione del consumo energetico dovuto a snoop . . . . . . . . . . . . . . . . . . . .

24

5.2 Battery-driven DPM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

25

6 Appendice: Approfondimenti

26

6.0.1 PLL e latenze indotte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Pagina iv

26

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

1 Introduzione

Questo documento offre una panoramica ad alto livello sul tema della gestione dinamica del

consumo di potenza (in seguito indicato con DPM, acronimo di Dynamic Power Management)

principalmente nell’ambito dei sistemi embedded. Il tema sarà trattato con un approccio orientato prevalentemente aspetti tecnologici, e ai prodotti esistenti; di conseguenza temi quali gli

argomenti correnti di ricerca assumeranno un ruolo secondario. Verranno invece considerate

tematiche correlate al DPM anche se non strettamente incluse nel campo embedded, quali le

funzionalità di gestione dell’alimentazione presenti in processori per PC e workstation.

Il documento è organizzato come segue: nel secondo capitolo vengono descritte le fondamentali

tecniche, che vengono praticate a basso livello (dalla progettazione dell’hardware alla gestione a

run-time dell’hardware stesso), al fine di ridurre il consumo energetico e di offrire al software la

possibilità di realizzare il DPM. Il terzo capitolo presenta una carrellata sulle funzionalità a basso

consumo rese disponibili prima da alcuni microprocessori per PC portatili, quindi da processori

per sistemi embedded. Nel quarto capitolo descriveremo un particolare framework software per

l’interfacciamento di hardware e software in contesto DPM. Nell’ultimo capitolo presentiamo un

breve campionario rappresentativo dei temi sui quali la ricerca è attiva nel settore.

Pagina 1

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

2 Hardware e riduzione del consumo

2.0.1

Tecniche hardware di riduzione del consumo

Come è noto, il consumo energetico di un componente elettronico realizzato in tecnologia CMOS

è dovuto principalmente ai tre contributi evidenziati nella formula:

P = Pswitching + Pleakage + Pshort−circuit

dove:

• il primo contributo rappresenta il consumo energetico dovuto alla carica e alla carica delle

capacità di uscita di ogni circuito CMOS, e dipende linearmente dalla frequenza di clock f

e quadraticamente dalla tensione VDD

Pswitching =

1

2

CL VDD

f

2

• il secondo contributo rappresenta le perdite dovute dalla corrente di polarizzazione inversa

(IL ) e dalla corrente di sotto-soglia (IDS ), e scala linearmente con la tensione, come da

formula:

Pleakage = (IL + IDS )VDD

• il terzo contributo rappresenta l’energia associata alla corrente di corto circuito circolante

durante le commutazioni. Consideriamo il semplice invertitore MOS presentato in figura:

Durante il passaggio di VI da livello logico alto a basso dobbiamo assumere lo slew rate

sia finito, e che la chiusura1 del transistor PMOS e l’apertura di quello NMOS avvengano

contemporaneamente e in tempo non infinitesimo. Esisterà quindi un lasso di tempo in

cui entrambi i transistor sono in zona saturazione ed esibiscono resistenza finita; essendo

2

3

per entrambi i transistor I ∝ VDS

, l’energia dissipata in una commutazione sarà E ∝ VDS

e

3

la potenza scalerà linearmente con la frequenza e con il cubo della tensione: P ∝ f VDS .

Dunque, per quanto riguarda l’hardware, i parametri critici su cui agire per la riduzione del

consumo energetico sono principalmente la frequenza e la tensione a cui i circuiti lavorano. In

particolare le strategie messe in atto sono le seguenti:

2.0.2

Spegnimento selettivo

Molte architetture permettono di togliere l’alimentazione ai dispositivi esterni, ai dispositivi a

bordo (controller LCD, controller IrDA, timer, etc.) e addirittura a porzioni del core. A seconda

delle implementazioni, parte di queste decisioni possono essere prese dinamicamente oppure

“cablate” staticamente nel microcodice del processore.

1 A fini di chiarezza, precisiamo che chiusura e apertura sono termini qui utilizzati in senso elettrico (un ramo di un

circuito è chiuso quando ha resistenza nulla, e aperto quando ha resistenza infinita), non ci riferiamo allo stato di aperto

o chiuso del canale MOS.

Pagina 2

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

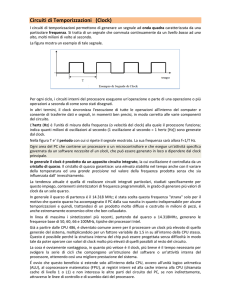

2.0.3

Clock gating

Dato che gran parte del consumo di potenza dei circuiti CMOS è dovuto alla commutazione,

mentre il consumo statico è trascurabile, è una buona idea non far giungere il clock a quei

componenti che non sono coinvolti nella computazione corrente, evitando cosı̀ commutazioni

inutili e dispendiose. Un semplice modo per far ciò è determinare staticamente quali unità

sono richieste per lo svolgimento di ciascun passo di ciascuna istruzione, e fare in modo che,

durante l’esecuzione, l’unità di instruction decode attivi le sole linee di clock enable indirizzate

a tali unità. Ciascuna unità non riceverà il clock direttamente ma solo dopo il transito in una

porta AND insieme al relativo segnale di clock enable.

In figura abbiamo riportato un esempio molto semplice di architettura di processore a tre bus,

privo di pipelining, dotato di un datapath costituito da tre unità (più l’unità di decode), a cui è

stato applicato il clock gating;

2.0.4

Riduzione della frequenza di clock

Riducendo la frequenza del clock di sistema si abbattono i due dei tre contributi di potenza

sopra descritti che dipendono linearmente da tale frequenza. La modifica della frequenza del

clock sulla base della quantità di capacità di calcolo richiesta è forse la principale delle strategie

di DPM, ed è resa possibile da alcuni accorgimenti costruttivi del PLL che genera il clock (a cui

è dedicato il paragrafo 6.0.1, a pagina 26).

In particolare il circuito che implementa la divisione di frequenza, presente nell’anello di retroazione,

può essere implementato come un contatore digitale riprogrammabile. Inoltre viene consentito

al processore di leggere e scrivere il registro contenente il divisore, rendendo quindi il processore

abilitato alla modifica della propria frequenza di clock. Si tenga presente che il PLL è un circuito

Pagina 3

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

di regolazione ad anello chiuso, che ha tempi di risposta non infinitesimi, e che a seguito di una

modifica del divisore può richiedere tempi di 2-4 ordini di grandezza superiori al periodo di clock

prima di fornire di nuovo una uscita stabile.

2.0.5

Clock bursting / stop-clock

Effetti del tutto simili a quelli descritti al punto precedente si possono raggiungere senza agire

sul PLL (e quindi senza doverne subire le latenze) per mezzo del bursting del clock, noto anche

come stop-clock. Questo meccanismo consiste nel generare un secondo segnale, denominato

“stop clock” e sagomato come un’onda quadra con un duty cycle controllabile; quindi si mettono

in AND il clock e il segnale appena generato e ciò che ne risulta (un segnale che presenta dei

treni di clock, come in figura) viene usato per pilotare il microprocessore.

I processori per sistemi embedded rendono disponibile questa tecnica al programmatore proprio

per fini di riduzione del consumo, mentre i processori per PC la sfruttano come strategia di

controllo termico. Di conseguenza, normalmente nei processori per sistemi embedded, il numero

di valori differenti che si possono scegliere per il duty-cycle è abbastanza elevato (ad esempio 32

nel Motorola DragonBall) mentre in quelli per PC è modesto (ad esempio 8 nel Pentium III e 4);

2.0.6

Riduzione delle tensioni di alimentazione

Abbiamo mostrato come il consumo di potenza scali con il cubo della tensione di alimentazione.

Questo ha motivato negli ultimi anni uno sforzo intenso verso processi di fabbricazione che

permettessero di tensioni operative sempre più basse, dai 5 V di un tempo agli 0.9 V di oggi.

Per gli stessi motivi, i processori di nuova generazione che permettono di variare dinamicamente

la frequenza di clock, permettono di variare congiuntamente anche la tensione. Si tenga però

presente che tensione e clock non sono variabili comandabili indipendentemente, in quanto la

frequenza massima a cui un processore può operare è legata dalla tensione fornita, secondo la

formula seguente ([22]):

f∝

(VDD − VT h )2

VDD

dove VT h è la tensione di soglia dei transistor MOS utilizzati. È quindi opportuno che le strategie

più aggressive di DPM siano in grado di scegliere la minima tensione possibile che permetta il

funzionamento alla frequenza scelta (cfr. [25], [26]).

Pagina 4

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

2.0.7

Stati a consumo ridotto

Gli stati a consumo ridotto non sono propriamente una strategia hardware, come quelle esaminate ai punti precedenti, sono piuttosto una interfaccia attraverso la quale alcune delle strategie

esaminate possono essere esposte verso il programmatore. L’esempio più semplice è lo stato di

“auto halt” e l’istruzione HLT che permette di entrarvi. L’ingresso in stato “auto halt” pone il

processore in una condizione di consumo ridotto (i manuali tecnici esaminati, però, non spiegano mai con precisione quali strategie si attivino), che ha fine appena si verifica un interrupt;

a tale evento il processore reagisce ritornando immediatamente alla piena operatività.

Normalmente è compito del sistema operativo eseguire l’istruzione HLT quando non vi sono processi pronti; inoltre, in tutti i sistemi operativi basati su eventi e messaggi, i processi possiedono

un ciclo di gestione dei messaggi, in cui figura una chiamata di sistema del tipo GetMessage(),

bloccante. Tale chiamata è il punto ideale dove porre l’istruzione HLT, da eseguire se non vi

sono eventi da dispacciare.

2.1

Vincoli, difficoltà, costi

Vi sono alcuni vincoli che, in particolari condizioni e circostanze, rendono poco praticabili, difficili da attuare oppure poco efficienti talune delle strategie elencate nel paragrafo precedente.

Inoltre, ciascuna di esse comporta sempre un prezzo da pagare in termini di prestazioni, latenze,

energia. Queste considerazioni costituiscono l’argomento di questa sezione.

2.1.1

Latenze

Tutte le tecniche di risparmio esaminate inducono latenze, maggiori o minori, dovute in alcuni

casi ad attese per l’esaurimento di transitori elettrici (come nello spegnimento/riaccensione di

moduli, del PLL oppure nella regolazione del moltiplicatore di clock, si veda la sezione 6.0.1), in

altri al ripristino del contesto (come allo spegnimento delle cache), nell’accezione più generalizzata che questo termine può avere.

In generale le tecniche che riducono maggiormente il consumo sono quelle che causano le latenze superiori: ad esempio gli stati di halt causano lo spegnimento di porzioni ridotte del core e

richiedono pochi cicli di clock prima che il processore sia di nuovo pienamente operativo; lo

spegnimento del PLL richiede un periodo di stabilizzazione del clock alla sua riaccensione; lo

spegnimento dei registri richiede il salvataggio e il recupero di tutto il contesto, lo stesso dicasi

per lo spegnimento delle cache, fatte le dovute proporzioni.

Una delle tecniche citate per ridurre il consumo energetico è la riduzione della frequenza di

clock, che può essere implementata a due passi prefissati (come nella tecnologia SpeedStep

di Intel) oppure a passi multipli (come nel PowerPC 405LP). In ogni caso la modifica del clock

avviene attraverso la variazione del moltiplicatore e implica tempi di stabilizzazione del PLL.

È chiaro che le strategie di risparmio applicabili in un determinato contesto applicativo dipendono dai vincoli temporali che esso impone: un sistema real-time con vincoli stringenti dovrà, in

generale, attuare strategie di risparmio energetico caratterizzate da tempi di recupero più brevi

(e quindi con efficacia minore) rispetto a sistemi non real-time.

2.1.2

Tempi di risposta del VRM

Come abbiamo detto, il consumo in potenza di un circuito CMOS scala con il cubo della tensione, e ciò motiva uno dei trend più forti nei processi di fabbricazione, cioè l’abbattimento delle

tensioni di funzionamento dei transistor MOS. D’altra parte, però, le correnti in gioco possono

assumere valori considerevoli (ICC max = 57.4÷70A, ICC avg = 63A a fronte di tensioni di 1.5÷1.75V

nel Pentium 4 [4]). Abbiamo detto inoltre che i processori possono spegnere o bloccare selettiva-

Pagina 5

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

mente proprie porzioni per regolare il consumo energetico. Di conseguenza la corrente da essi

assorbita può variare dinamicamente con gradini molto ripidi (slew rate anche di 5A/ns, secondo

[21]).

Questo significa che i moduli di regolazione della tensione (VRM, voltage regulator modules)

che presiedono alla corretta alimentazione dei processori sono sottoposti ad un carico resistivo

che varia con elevata rapidità, mentre si pretende da loro che la tensione di alimentazione resti

stabilizzata entro intervalli ristretti, con variazioni molto contenute nei valori (tolleranze sulla

tensione di ±2.85%, [4]) e nei tempi, che si traducono in brevi tempi di risposta del sistema di

controllo ad anello chiuso realizzato dal VRM.

È quindi evidente come non sia possibile pensare una strategia di riduzione del consumo senza

tenere in debito conto i limiti imposti dalle prestazioni del VRM.

2.1.3

Protocolli di snoop

Anche se non vi sono in produzione computer portatili multiprocessore, i processori per personal

computer in versione “Mobile” mantengono la compatibilità con i loro simili non-mobile, e quindi

sono progettati per essere impiegati anche in architetture multiprocessore.

Per di più, la riduzione del consumo energetico diventa di grande interesse per i sistemi server

multiprocessore per montaggio su rack, che pur non avendo vincoli sulle risorse energetiche

disponibili, sono soggetti a limitazioni sulla dissipazione termica smaltibile.

Questi due esempi sono sufficienti a motivare la sensatezza della compresenza di hardware per

il multiprocessing e per la riduzione del consumo. Ne consegue la necessità di implementare

protocolli di snoop atti ad effettuare la corretta invalidazione/aggiornamento dei blocchi di cache

contenenti dati che vengono scritti da altri processori, e l’importanza di progettare strategie

di riduzione di consumo che siano con essi compatibili; in particolare se si vuole mantenere

le cache del processore coerenti non è possibile spegnere o bloccare il clock alla circuiteria

necessaria per implementare lo snooping.

Pagina 6

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

3 Rassegna dei processori in produzione

In questo capitolo esaminiamo le funzionalità hardware di risparmio energetico offerte da alcuni

processori mobile per personal computer e da alcuni processori per sistemi embedded.

Lo sforzo per l’abbattimento dei consumi è forte in entrambi i contesti, ma si fa sempre più

determinante soprattutto nel secondo, visto che l’impatto del consumo del processore in un

sistema laptop è ormai ampiamente minoritario, come dimostrano i risultati riportati in figura

(e provenienti da [13]);

3.1

Processori “Mobile” per PC

In questa sezione vengono analizzate le funzionalità di riduzione dei consumi fornite dalle versioni “Mobile” di processori pensati per personal computer. Si tenga presente che tutti questi

processori possono esibire caratteristiche low-power, ma devono primariamente mantenere la

compatibilità completa con le loro versioni desktop, in particolare la possibilità di essere inseriti

in architetture multiprocessore, con la conseguente necessità di tenere attive le porzioni di processore necessarie a mantenere la coerenza delle cache (e cioè servire gli eventi di snoop) anche

negli stati low-power.

3.1.1

Intel Pentium 4-M

Il processore Pentium 4 M di Intel è un processore realizzato con teconologia di fabbricazione a

0.13 micron, disponibile in numerose versioni, con clock da 1.4 GHz a 2.4 GHz. Contiene una

cache di primo livello di 20k (8k per i dati e 12k per le istruzioni), e una cache di secondo livello

unificata di 512k. Opera su di un bus di sistema che opera a 400 MHz. Le tensioni di core a cui

opera sono pari a:

• 1.3 V con alimentazione da rete elettrica (“Maximum Performance Mode”);

• 1.2 V con alimentazione da batteria (“Battery Optimized Mode”);

• 1.1 V nello stato di “Deep Sleep” (durante inattività di microsecondi);

• 1.0 V nello stato di “Deeper Sleep” (durante le inattività fra la pressione di un tasto e l’altro);

Pagina 7

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

Nella seconda modalità il clock viene ridotto sempre a 1.2 GHz, indipendentemente dal clock

della prima modalità. I consumi a piena attività sono riportati nella tabella seguente:

Modo

High Performance

High Performance

High Performance

High Performance

High Performance

High Performance

High Performance

High Performance

High Performance

Battery Optimized Mode

Clock

2.40

2.20

2.00

1.90

1.80

1.70

1.60

1.50

1.40

1.20

GHz

GHz

GHz

GHz

GHz

GHz

GHz

GHz

GHz

GHz

Tensione core

1.3

1.3

1.3

1.3

1.3

1.3

1.3

1.3

1.3

1.2

Corrente core

V

V

V

V

V

V

V

V

V

V

36.7

34.5

33.3

32.2

31.0

29.9

28.7

27.5

26.3

22.1

A

A

A

A

A

A

A

A

A

A

Potenza

47.71

44.85

43.29

41.86

40.30

38.87

37.31

35.75

34.19

26.52

W

W

W

W

W

W

W

W

W

W

La gestione del consumo energetico viene effettuata per mezzo di tre strategie: gli stati a consumo ridotto, la riduzione della frequenza di clock e la riduzione della tensione di alimentazione.

Gli stati disponibili sono mostrati nel diagramma che segue:

• stato “Normal”: stato in cui il processore esegue le istruzioni;

• stato “Auto Halt”: stato a basso consumo in cui il processore si posiziona a seguito dell’esecuzione dell’istruzione HLT. L’asserzione di una qualsiasi linea di interrupt o di reset

causa l’immediato ritorno nello stato “Normal”. In stato di “Auto Halt” il processore accetta

richieste di snoop;

• stato “Stop Grant”: stato a basso consumo in cui il processore si muove a seguito dell’asserzione del segnale STOPCLK#. Durante questo stato, gli eventi di interrupt e di reset

non vengono gestiti, ma restano pendenti e vengono serviti al ritorno in stato “Normal”;

le richieste di snoop vengono invece accettate. Il segnale STOPCLK# può essere asserito

dal chipset a seguito di eventi ACPI oppure a seguito di allarmi termici. In particolare

STOPCLK# può essere soggetto a modulazione PWM con duty cycle dipendenti dalla temperatura, per agevolare il raffreddamento. A seguito della disasserzione di STOPCLK#, il

processore torna nello stato precedente (“Normal” o “Auto Halt”);

• stato “Halt/Grant Snoop”: quando il processore si trova in stato “Normal” oppure “Stop

Grant” e sul bus di sistema appare una richiesta di snoop, il processore subisce una tran-

Pagina 8

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

sizione in questo stato, vi permane il tempo necessario affinché la richiesta venga servita,

quindi ritorna nello stato di provenienza;

• stato “Sleep”: stato a consumo ridotto in cui il processore mantiene il suo contesto e il PLL

(phase locked loop), ma congela tutti i clock interni. Questo stato può essere raggiunto solo

a partire dallo stato “Halt/Grant Snoop” mediante asserzione del segnale SLP#. Durante

questo stato il processore non è in grado di servire richieste di snoop e non è in grado

di mantenere pendenti richieste di interrupt (che vanno perse); inoltre le linee del bus di

sistema devono restare immutate per tutta la durata dello stato di “Sleep”;

• stato “Deep Sleep”: si tratta di uno stato a consumo molto ridotto in cui si può transitare

a partire dallo stato “Sleep” per mezzo dell’asserzione del segnale DPSLP#. In questo stato,

come in “Sleep”, richieste di interrupt o di snoop vanno perse, e il bus di sistema deve essere

congelato. In stato “Deep Sleep” il PLL viene spento, ed è possibile fermare anche il clock.

Il ritorno da questo stato comporta una attesa di 30 microsecondi prima che il processori

si possa considerare in stato “Sleep”, periodo nel quale viene riattivato e stabilizzato il PLL;

• stato “Deeper Sleep”: si tratta dello stato a consumo minimo nel quale il processore

mantiene il contesto; è funzionalmente equivalmente al “Deep Sleep”, in più il consumo

viene ulteriormente abbattuto mediante abbassamento della tensione di alimentazione del

core. È compito del chipset pilotare i segnali di controllo del VRM in modo da ottenere

l’abbassamento di tensione.

Il Pentium 4 supporta la funzionalità di clock bursting a 8 passi discreti di duty cycle (12.5%,

25.0%, 37.5%, 50.0%, 63.5%, 75.0%, 87.5%). Tale tecnica non viene però utilizzata per la

riduzione dei consumi, ma solo per la protezione da sovratemperature.

3.1.2

Intel Pentium III-M

Il processore Pentium III-M di Intel è disponibile in versioni con frequenze di clock da 650 MHz a

1.40 GHz, operanti su un bus di sistema ad una frequenza di 133 MHz. In particolare gli ultimi

modelli, fabbricati in tecnologia da 0.13 micron, hanno clock a 1.13, 1.26 e 1.40 GHz. Esistono

inoltre modelli recenti, a tensione ridotta, che esibiscono frequenze di clock inferiori ma anche

minori consumi energetici. Il Pentium III-M contiene una cache di primo livello di 32k (16k+16k)

e una di secondo livello di 512k.

La tabella che segue mostra, per ogni modello e accoppiata frequenza/tensione in cui il processore opera in modo “Maximum Performance”, le frequenze e tensioni corrispondenti nel modo

“Battery Optimized”.

Processore

Mobile P III-M

Low Voltage

Mobile P III-M

Ultra Low

Voltage Mobile

P III-M

Pagina 9

Maximum Performance mode

Frequenza

Tensione

1.333

1.266

1.200

1.133

1.066

1.000

GHz

GHz

GHz

GHz

GHz

GHz

1.000 GHz

933 MHz

866 MHz

800 MHz

850 MHz

800 MHz

933

900

866

850

800

MHz

MHz

MHz

MHz

MHz

1.40 V

1.15 V

1.10 V

Battery Optimized mode

Frequenza

Tensione

800

800

800

733

733

733

MHz

MHz

MHz

MHz

MHz

MHz

533

533

533

533

500

500

MHz

MHz

MHz

MHz

MHz

MHz

400

400

400

400

400

MHz

MHz

MHz

MHz

MHz

1.15 V

1.05 V

0.95 V

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

I consumi energetici a piena attività che corrispondono ai modi elencati sopra vanno da 3.4W a

25.5W , come dettagliato di seguito.

Frequenza

Tensione

Corrente

300 MHz

350 MHz

400 MHz

450 MHz

466 MHz

500 MHz

533 MHz

700 MHz

750 MHz

667 MHz

733 MHz

750 MHz

800 MHz

850 MHz

866 MHz

866 MHz

933 MHz

1000 MHz

1066 MHz

1133 MHz

1200 MHz

0.95

0.95

0.95

1.05

1.05

1.05

1.05

1.10

1.10

1.15

1.15

1.15

1.15

1.15

1.15

1.40

1.40

1.40

1.40

1.40

1.40

3.58

3.90

4.20

6.08

6.19

6.38

6.61

7.58

7.58

8.90

9.39

9.47

9.84

10.21

10.32

15.87

16.45

16.83

17.46

18.11

18.27

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

Potenza

3.401

3.705

3.990

6.384

6.500

6.700

6.941

8.338

8.338

10.245

10.799

10.891

11.316

11.742

11.868

22.218

23.030

23.562

24.444

25.354

25.578

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

Il Pentium III-M di Intel esibisce funzionalità a basso consumo del tutto sovrapponibili a quelle

del suo successore, già esaminato nel paragrafo precedente, fatta eccezione per l’assenza dello

stato “Sleep”, come denota il diagramma degli stati in figura.

Pagina 10

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

3.1.3

AMD Athlon XP

Il processore Athlon XP di AMD è un processore fabbricato (negli ultimi step) in tecnologia da

0.13µm, con varianti nei clock da 1.4 a 1.8 GHz, cache di primo livello da 64k+64k, di secondo

livello da 256k, e bus di sistema da 133MHz con RAM DDR attive sui due fronti.

La tabella che segue mostra, per ogni modello, le frequenze e le tensioni operative nominale, e

inoltre le correnti e i consumi energetici nominali e massimi.

Modello Frequenza

di clock

1700+

1800+

1900+

2000+

2100+

2200+

1467

1533

1600

1667

1733

1800

MHz

MHz

MHz

MHz

MHz

MHz

Tensione

Nominale

Potenza

tipica

Potenza

massima

Corrente

tipica

(working)

Corrente

massima

(working)

Corrente

tipica

(stop/grant)

Corrente

massima

(stop/grant)

1.50V

1.50V

1.50V

1.60V

1.60V

1.65V

44.9W

46.3W

47.7W

54.7W

56.4W

61.7W

49.4W

51.0W

52.5W

60.3W

62.1W

67.9W

29.9A

30.9A

31.8A

34.2A

35.2A

37.4A

32.9A

34.0A

35.0A

37.7A

38.8A

41.2A

2.8A

2.8A

2.8A

3.3A

3.3A

3.6A

4.5A

4.5A

4.5A

5.4A

5.4A

5.9A

Di seguito è riportato anche il diagramma degli stati:

La semantica degli stati sopra evidenziati è descritta qui di seguito:

• stato “C0 Working”: stato in cui il processore esegue le istruzioni;

• stato “C1 Halt”: stato a basso consumo in cui il processore si posiziona a seguito dell’esecuzione dell’istruzione HLT. L’asserzione di una qualsiasi linea di interrupt o di reset

causa l’immediato ritorno nello stato “C0 Working”. In stato “C1 Halt” il processore accetta

richieste di snoop;

• stato “C2 Stop Grant”: stato a basso consumo in cui il processore si muove a seguito

dell’asserzione del segnale STOPCLK#. Durante questo stato, gli eventi di interrupt e di

reset non vengono gestiti, ma restano pendenti e vengono serviti al ritorno in stato “C0

Pagina 11

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

Working”; le richieste di snoop vengono invece accettate. Il segnale STOPCLK# può essere

asserito dal chipset a seguito di eventi ACPI oppure a seguito di allarmi termici. In particolare STOPCLK# può essere soggetto a modulazione PWM con duty cycle dipendenti dalla

temperatura, per agevolare il raffreddamento. A seguito della disasserzione di STOPCLK#,

il processore torna nello stato precedente (“Normal” o “Auto Halt”);

• stato “Probe State”: quando il processore si trova in stato “C0 Working” oppure “C2 Stop

Grant” e sul bus di sistema appare una richiesta di snoop, il processore subisce una transizione in questo stato, vi permane il tempo necessario affinché la richiesta venga servita,

quindi ritorna nello stato di provenienza;

• stato “Sleep”: stato a consumo ridotto in cui il processore mantiene il suo contesto e il PLL

(phase locked loop), ma congela tutti i clock interni. Questo stato può essere raggiunto solo

a partire dallo stato “Halt/Grant Snoop” mediante asserzione del segnale SLP#. Durante

questo stato il processore non è in grado di servire richieste di snoop e non è in grado

di mantenere pendenti richieste di interrupt (che vanno perse); inoltre le linee del bus di

sistema devono restare immutate per tutta la durata dello stato di “Sleep”;

3.1.4

Transmeta Crusoe TM5500

Crusoe TM5500 è un processore con un core VLIW, destinato a laptop di fascia entry-level

e progettato per abbattere drasticamente il consumo energetico e la dissipazione termica. A

bordo del TM5500 gira un software di bassissimo livello, caricato dalla ROM all’accensione, che

implementa una tecnologia di traduzione (denominata Code Morphing), e che lo rende in grado

di eseguire codice x86. È disponibile con un clock da 667 a 800 MHz, con cache di primo

livello di 64k+64k e di 256k per il secondo livello. A detta del produttore, un Crusoe a 700

MHz è approssimativamente equivalente ad un Pentium III-M a 500 MHz; prove comparative

consistenti nella riproduzione di un filmato da DVD sotto sistema operativo Windows 2000

hanno evidenziato una potenza media elettrica assorbita di 1.0 e 7.5 W, e temperature massime

di 48.40 C e 105.50 C rispettivamente.

Il diagramma degli stati messi a disposizione dal TM5500 è riportato in figura:

Pagina 12

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

Per ciascuno degli stati rappresentati in figura e riportati nella tabella che segue (nella terza

colonna), indichiamo gli stati possibili dello standard ACPI e le condizioni operative in cui si

trovano l’SDRAM e il generatore di clock.

ACPI System State

G0

G0

G0

G0

G1

G1

G1

G2

G3

/

/

/

/

/

/

/

/

S0

S0

S0

S0

S1

S3

S4

S5

3.2

/

/

/

/

C0

C1

C2

C3

Working

Auto Halt

Quick Start

Deep Sleep

Sleeping

Suspend-to-RAM

Suspend-to-Disk

Soft Off

Mechanical Off

Processor State

SDRAM

Clock Generator

Normal

Auto Halt

Quick Start

Deep Sleep

Deep Sleep

Off

Off

Off

Off

Normal

Normal/Self Refresh

Self Refresh

Self Refresh

Self Refresh

Self Refresh

Off

Off

Off

Running

Running

Running

Clocks Stopped

PLL Shut Down

PLL Shut Down

Off

Off

Off

Processori per sistemi embedded

In questa sezione esaminiamo le caratteristiche di processori appositamente progettati per l’impiego

in sistemi embedded.

3.2.1

Intel 80200

Il processore 80200 è un processore RISC StrongARM, basato sulla architettura XScale (compatibile ARM V5 per le operazioni intere e ARM V4 per quelle in virgola mobile). È pensato

per applicazioni ad alte prestazioni e basso consumo quali telefoni della terza generazione o

computer palmari.

Pagina 13

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

È possibile controllare il consumo energetico passando in uno degli stati a basso consumo

(“Idle”, “Drowsy”, “Sleep”) o modificando dinamicamente il moltiplicatore del clock.

3.2.1.1

Stati a consumo ridotto

La commutazione di stato di consumo energetico avviene da software semplicemente modificando il registro PWRMODE di un componente del chipset.

Stati disponibili:

• stato “Active”: stato in cui il processore esegue le istruzioni, corrispondente al valore 0 del

registro PWRMODE;

• stato “Idle”: stato a basso consumo in cui si entra scrivendo il valore 1 in PWRMODE.

All’ingresso in questo stato viene atteso lo svuotamento della pipeline. In stato “Idle” il PLL

è attivo e il contesto viene mantenuto. L’asserzione di una delle linee di interrupt causa

il ritorno allo stato “Active” e la prosecuzione dell’esecuzione delle istruzioni, dopo una

latenza di circa 10 cicli di clock (CLK, clock di sistema);

• stato “Drowsy”: stato a consumo ancor più ridotto in cui si entra scrivendo il valore 2 in

PWRMODE. All’ingresso in questo stato viene atteso lo svuotamento della pipeline, quindi

viene spento il PLL. Il contesto viene mantenuto. L’asserzione di una delle linee di interrupt causa la riaccensione del PLL e il ritorno allo stato “Active”, quindi la prosecuzione

dell’esecuzione delle istruzioni. Il ritorno allo stato “Active” prevede una latenza di circa

2000 cicli di clock (CLK);

• stato “Sleep”: stato a consumo nullo, raggiunto ponendo PWRMODE a 3. Prima dell’ingresso in questo stato il contesto deve essere salvato perchè viene ovviamente perso all’abbattimento della tensione di alimentazione. Si esce da questo stato solo mediante asserzione

della linea di reset.

3.2.1.2

Riduzione del clock

L’Intel 80200 accetta una frequenza di clock di sistema (CLK) variabile da 33 a 66 MHz e contiene

un PLL che realizza un moltiplicatore variabile da 3 a 11, realizzando quindi (con CLK 66 MHz)

un clock interno (CCLK) da 200 a 733 MHz. La commutazione del moltiplicatore può essere

effettuata da software senza necessità di reset del processore, in modo da modulare il clock in

base al carico di lavoro. Il cambio di clock richiede l’attesa della stabilizzazione del PLL, che può

richiedere un migliaio di cicli di CLK.

3.2.2

ARM1022E

3.2.2.1

Stati a consumo ridotto

La commutazione di stato di consumo energetico avviene da software semplicemente modificando il registro PWRMODE di un componente del chipset.

Stati disponibili:

• stato “Run”: stato in cui il processore esegue le istruzioni;

• stato “Standby”: stato a basso consumo in cui il processore resta interamente alimentato

ma il clock viene fermato. L’asserzione di una delle linee di interrupt causa il ritorno allo

stato “Run”. Il tempo di recupero è dell’ordine dei 10 cicli di clock;

• stato “Dormant”: stato a basso consumo in cui il processore viene disalimentato mentre la

cache e l’elettronica di power management restano alimentate. Il contesto viene perso, deve

Pagina 14

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

quindi essere salvato prima dell’ingresso in questo stato. Il tempo di recupero è dell’ordine

di 100 cicli;

• stato “Shutdown”: stato a consumo nullo, in cui sia il processore che la cache vengono

disalimentati. Il tempo di recupero è dell’ordine di 10000 cicli;

3.2.3

Motorola MC68EZ328 DragonBall EZ

Il DragonBall EZ è un microprocessore funzionalmente compatibile con lo storico 68000 e con

funzionalità aggiuntive quali controller LCD, porte seriali e parallele. Viene utilizzato nella

grande maggioranza dei computer palmari con sistema operativo PalmOS.

Al fine di ridurre il consumo energetico è possibile agire sul PLL modificando la frequenza di

clock, oppure sul modulo di regolazione del consumo, effettuando il clock-bursting con dutycycle variabile, oppure entrando in uno stato a basso consumo.

3.2.3.1

Stati a basso consumo e clock bursting

• “normal mode”: è il modo in cui il microprocessore opera dopo il reset. Al momento del

reset, inoltre, il modulo di controllo del consumo energetico è disabilitato e il clock oscilla

con continuità. Per abilitare il controllo del consumo energetico è sufficiente abilitare

tale modulo ponendo a 1 un bit dell’apposito registro di controllo e regolare il duty-cycle

del bursting; il duty cycle è regolabile dallo 0% al 100% in 32 passi, corrispondenti ad

incrementi di circa il 3%. In questo modo è possibile dosare finemente il consumo di

potenza e la dissipazione termica. All’arrivo di un interrupt il modulo di controllo del

consumo viene di nuovo disabilitato e l’interrupt viene servito a clock pieno. E’ compito

dell’interrupt service routine riabilitare il bursting se lo ritiene opportuno;

Pagina 15

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

• “doze mode”: è una modalità a consumo ridotto a cui si giunge abilitando il bursting e

portando a zero il duty-cycle. Il clock del core della CPU è fermo, ma le periferiche, incluso il

controller LCD non ne risentono in alcun modo, essendo dotate di clock separati. All’arrivo

di un interrupt o di un segnale di reset il bursting viene immediatamente disabilitato e il

processore torna a clock pieno;

• ”sleep mode”: viene disattivato il PLL (cfr. 6.0.1), interrompendo cosı̀ tutti i clock di sistema,

ad eccezione del clock a bassa frequenza (32kHz), che resta attivo al fine di mantenere

aggiornato il real-time clock. Eventi di interrupt e di reset causano la riattivazione dei

clock, e la piena operatività del sistema dopo un periodo di stabilizzazione di 1ms circa.

3.2.3.2

Regolazione del PLL

Il sistema genera una bassa frequenza da 32kHz tramite quarzo che viene usata sia dal real-time

clock che dal PLL. L’uscita del PLL viene divisa tramite un prescaler e quindi divisa ulteriormente

per originare altre tre frequenze: il clock per la RAM, il clock del bus di sistema e il clock del

controller LCD. I clock di sistema ottenibili vanno da circa 10 MHz a oltre 54 MHz.

3.2.4

IBM PowerPC 405LP

Il PowerPC 405LP è il microprocessore per applicazioni embedded a bassissimo consumo appena

annunciato da IBM. Integra una pipeline a 5 stadi, 16+16Kbyte di cache dati e istruzioni, e l’architettura interna fa uso estensivo del clock gating. Mette a disposizione le seguenti funzionalità

di risparmio energetico:

• controllo del clock: il software può regolare dinamicamente la frequenza di clock fra un

minimo di 152 e un massimo di 380 MHz;

• controllo del voltaggio: il software può regolare dinamicamente la tensione di alimentazione

del core, da 1.0 a 1.8V;

• stati a consumo ridotto: tramite software si può portare il processore in una delle 3

modalità idle a basso consumo energetico;

• modo “Cryo” a consumo zero: il contesto del microprocessore viene salvato su memoria non

volatile EEPROM pilotata tramite bus IIC, quindi viene tolta alimentazione. L’operazione di

ripristimo da spento, comprendente la sequenza di power-on, la stabilizzazione del PLL e il

recupero del contesto da EEPROM ha una latenza di 200 ms.

Pagina 16

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

Pagina 17

Frequenza

di clock

Tensione

Consumo

380 MHz (max)

152 MHz (min)

1.8 V

1.0 V

500 mW

53 mW

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

4 Un esempio di framework DPM

Nell’ambito PC esiste uno standard ben affermato, denominato ACPI e giunto ormai alla versione 2.0, che regola l’interazione fra componenti hardware e software al fine di regolare il

risparmio energetico, in particolare i tempi di inattività delle periferiche oltre i quali esse vengono spente, le funzionalità di sospensione e ibernazione, i differenti profili attivi quando la

macchina è alimentata dalla rete elettrica oppure da batteria.

In questo capitolo esaminiamo nel dettaglio una architettura software per il DPM che si propone

in qualche modo obbiettivi simili ma nell’ambito embedded. In particolare vuole adattarsi alle

caratteristiche peculiari (e sfruttarle, ove possibile) del DPM sotto sistemi embedded, che sono

le seguenti:

• possibilità di scalare frequenza di clock con latenze di pochi microsecondi e tensioni di core

con latenze di poche decine di microsecondi, il tutto senza interrompere le elaborazioni;

• conseguente possibilità di realizzare una politica DPM aggressiva, ovvero con modifica

frequente e a grana fine di clock e tensioni, in dipendenza del carico di lavoro;

• mancanza di un BIOS che fornisca un livello di isolamento del sistema operativo dall’hardware, e conseguente ricaduta dei ruoli di power management sul sistema operativo

stesso;

• predominanza del consumo del processore sul consumo globale del sistema.

Il DPM framework qui proposto è stato elaborato da IBM e MontaVista, i quali stanno collaborando nella progettazione di un computer palmare basato sul microprocessore PowerPC 405LP

e sul sistema operativo Linux. Le prerogative di questo framework sono la semplicità (il DPM

deve essere trasparente per le applicazioni, salvo quelle appositamente realizzate in modo da

essere power-aware), la modularità (deve essere facile per i produttori di hardware scrivere le

loro policies) e la flessibilità.

4.1

Panoramica architetturale

In figura è rappresentata la struttura proposta: l’implementazione a basso livello del DPM si

trova nel kernel e contiene le policy, il cui significato verrà chiarito in seguito. Il gestore delle

policy può essere realizzato a livello di sistema operativo oppure a livello applicativo. Si noti

che il DPM non può essere visto come un driver a sé stante, invece costituisce un insieme di

modifiche e aggiunte da apportare in punti critici del kernel.

La figura che segue illustra l’architettura descritta.

Pagina 18

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

4.2

Concetti fondamentali

Il DPM framework qui proposto poggia su una manciata di concetti fondamentali, che vengono

definiti e commentati in questa sezione. Per chiarificare meglio, utilizzeremo esempi che si

riferiscono ad una architettura basata sul PowerPC 405LP già descritto.

4.2.1

Operating point

In ogni istante il sistema funziona ad un dato operating point, che è determinato da parametri

quali le frequenze del VCO, della CPU e del bus, la tensione di core, lo stato delle periferiche, le

temporizzazioni della RAM. Nell’architettura citata, un esempio di operating point è il seguente:

Frequenza del VCO del PLL

Frequenza di clock della CPU

Frequenza di clock del bus locale CPU

Frequenza del bus esterno

Tensione di core

Temporizzazione SDRAM

4.2.2

800 MHz

200 MHz

100 MHz

33 MHz

1.0 V

CAS 2

Operating state

Il sistema operativo può essere pensato come una macchina a stati, che si muove fra stati

differenti a seconda degli eventi che intervengono (i task vengono schedulati, giungono richieste

di interrupt, un task si mette in attesa, ecc.), come in figura.

Pagina 19

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

Ci riferiremo a questi stati come operating state. In una politica DPM aggressiva, si può associare

uno specifico operating point a ciascun operating state. L’introduzione degli operating state è

giustificata dal fatto che si possono ottenere risparmi energetici molto significativi riducendo

clock e tensioni quando il sistema non è occupato. Questo porta ad una naturale distinzione

fra gli stati attivi e inattivi, ciascuno con differenti operating point. Gli stati attivi possono

essere multipli: uno di essi sarà lo stato di default che verrà assegnato in maniera trasparente

alla maggioranza dei task, in più possono esistere altri stati, specializzati, per le applicazioni

power-aware.

Gli stati dei task sono simili alle priorità di processo, ma non bisogna cedere alla tentazione

di pensare che processi con elevata priorità richiedano operating point ad alte prestazioni. Si

consideri l’esempio di un player MP3, che viene schedulato con priorità real-time ma richiede

solo una piccola frazione della potenza di calcolo messa a disposizione dal processore quando

portato alle massime prestazioni.

4.2.3

Vincoli e classi di congruenza degli operating point

Gli stati dei dispositivi a bordo del processore e di quelli esterni influenzano in maniera determinante il consumo del sistema e vincolano la scelta degli operating point. Nel caso specifico il PPC

405LP contiene un controller LCD che accede ad un framebuffer situato in SDRAM, questo implica che se l’LCD è attivato, il sistema deve mantenere una frequenza del bus verso la memoria

che sia sufficiente a permettere la frequenza scelta di refresh dell’immagine.

Per descrivere questo tipo di vincoli nel framework DPM proposto, sono state introdotte le classi

di equivalenza degli operating point e i vincoli di dispositivo. I vitelli dei Romani sono belli.

Le classi di equivalenza degli operating point raggruppano gli operating point che il progettista

considera equivalenti fissato un operating state. Per ogni dispositivo, ci saranno inoltre semplici

regole che permettano di invalidare gli operating point non rispondenti ai vincoli e scegliere il

migliore fra quelli validi.

L’applicazione dei queste regole avviene a livello di kernel; in questo modo non si obbliga il

progettista a prevedere un policy manager a run-time.

In figura sono rappresentati due operating state, uno denominato “task”, pensato per essere

utilizzato quando sono in esecuzione processi, l’altro, denominato “idle”, pensato per i periodi

di inattività. Ciascuno di essi è costituito da una classe di congruenza contenente 3 operating

point.

Pagina 20

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

Una volta applicate le regole associate ai dispositivi (in particolare la regola già citata sul clock

del bus con controller LCD attivato), in ciascun operating state vengono invalidati gli operating

point, che hanno frequenza di pixel clock insufficienta (nella figura è indicata con PXL). A questo

punto il gestore DPM sceglie, fra gli operating point validi, quello a consumo minore (in figura è

marcato con un doppio cerco).

4.2.4 Policy e Policy manager

Il concetto a più elevato livello di astrazione nell’architettura DPM descritta è la policy. Una

policy è una funzione che mappa ciascun operating state verso una classe di congruenza di

operating point. Una strategia di power management deve specificare almeno una policy, ma può

specificarne numerose, una per ogni profilo o situazione operativa che ritiene possa verificarsi.

In figura è rappresentata una policy con tutti gli elementi costituenti:

per ciascun operating state è riportata la relativa classe di congruenza degli operating point, di

cui quello al momento selezionato è indicato con il colore grigio.

4.3

Implementazione astratta

In questa sezione presentiamo le scelte implementative che MontaVista ha adottato per concretizzare i concetti esposti. L’implementazione DPM presente nel kernel del sistema operativo

Pagina 21

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

espone 5 chiamate di sistema, rappresentate in figura: assert constraint(), remove constraint(),

set operating state(), set policy() e set task state(), delle quali le prime tre sono visibili soltanto

nel contesto del kernel, mentre le ultime 2 sono accessibili anche a livello applicativo.

Le esaminiamo brevemente nei paragrafi seguenti.

4.3.1

set operating state()

Questa chiamata serve per indicare al DPM in quale operating state ci si trova. Ci si aspetta

che questa chiamata venga invocata al momento del context switch da un processo all’altro,

quando il sistema operativo entra in inattività perchè tutti i processi sono in attesa, e quando

viene servita una richiesta di interrupt.

A seguito dell’invocazione di questa funzione, il DPM prende atto del cambio di operating state

e regola l’hardware in modo da assumere le impostazioni del miglior operating point valido

appartenente alla classe di congruenza associata all’operating state corrente.

4.3.2

assert constraint()

Questa funzione viene permette di impostare un vincolo di dispositivo come quello esemplificato in 4.2.3, e viene generalmente invocata all’interno dei driver di dispositivo, tipicamente in

risposta a chiamate di tipo open().

4.3.3

remove constraint()

Questa funzione viene permette di eliminare un vincolo di dispositivo impostato con la chiamata

precedente, e viene generalmente invocata all’interno dei driver di dispositivo, tipicamente a

seguito di chiamate quali close().

4.3.4

set policy()

Questa chiamata permette l’impostazione di una policy a livello di sistema. Ci si aspetta che sia

il sistema operativo ad invocare questa chiamata una volta per tutte, al momento dell’avvio, ma

niente vieta la costruzione di un policy manager, implementato come applicazione in user space,

che si occupi di modificare a run-time le policy, in base alle decisioni dell’utente.

4.3.5

set task state()

Questa chiamata permette di selezionare a quale operating state debba essere associato ad un

dato processo. A seconda delle scelte implementative, si può fare in modo che l’invocazione

Pagina 22

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

di questa chiamata possa essere effettuata da un solo processo che realizza il policy manager

oppure anche da singoli processi critici power-aware, che possono voler partecipare alla scelta

dei propri operating point.

4.4

Conclusioni

Il framework DPM qui presentato esibisce doti di portabilità, in quanto si limita a specificare una

gerarchia di oggetti denominati che può essere potenzialmente implementata in ogni sistema e

non impone il modo di specificare gli operating point, né gli operating state, né le policy. Inoltre

l’architettura è sufficientemente modulare da permettere l’implementazione dei vincoli di un

dispositivo all’interno del driver del dispositivo stesso.

Pagina 23

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

5 Argomenti di ricerca

In questa sezione citiamo alcuni interessanti filoni di ricerca, relativi alle tematiche esposte nei

capitoli precedenti, che risultano attivi e promettenti al momento.

5.1

Riduzione del consumo energetico dovuto a snoop

Come abbiamo già enunciato, in ambiente di multiprocessing, le richieste di snoop causano

consumo di potenza in un processore anche quando questo si trova in stato di inattività. In

[19] gli autori osservano che una larga maggioranza delle richieste di snoop non trovano il proprio “argomento” nella cache locale considerata, e propongono l’introduzione di un componente,

denominato JETTY, da inserire fra il bus e il back-end della cache di secondo livello del processore, che agisca da filtro, impedendo alle richieste che genererebbero sicuramente miss di

arrivare alla cache.

Nella figura che segue è rappresentata una architettura SMP tradizionale, in cui tutti gli array

di tag della cache di secondo livello consumano energia ad ogni richiesta di snoop.

Nella prossima figura è invece rappresentata una architettura in cui è stato introdotto il componente JETTY; in questo caso, una richiesta di snoop viene inoltrata alla cache L2 solo se è

possibile che generi un cache hit.

Pagina 24

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

Gli autori propongono diverse strategie per la realizzazione del JETTY (per esempio facendo in

modo che contenga un sottoinsieme il più ampio possibile delle locazioni che generano miss

oppure un soprainsieme il più ristretto possibile di quelle che generano hit), e dichiarano di

aver raggiunto, in una configurazione di test SMP con 4 processori, un filtraggio del 77% delle

richieste, che risulta nell’abbattimento del 41% del consumo causato da tutte le richieste di

snoop.

5.2

Battery-driven DPM

In [25] e [26] gli autori osservano che nella gran parte delle strategie di DPM si mira alla minimizzazione della potenza assorbita, mentre nei dispositivi portatili l’obiettivo desiderato è la

massimizzazione della durata delle batterie. A prima vista i due obiettivi possono sembrare

coincidenti, e lo sarebbero se le batterie esibissero comportamento ideale, cioè avessero una

capacità indipendente dalle correnti di scarica. Ma cosı̀ non è: non solo la capacità utilizzabile

di una batteria dipende in maniera forte dalle correnti che ne vengono prelevate, come mostrato

nel grafico a sinistra della figura, ma le batterie tendono in qualche modo a recuperare parte

della capacità utile se lasciate a riposo, come mostrato nel grafico a destra.

Muovendo da queste considerazioni gli autori propongono delle strategie di DPM che invece di

essere rivolgere la loro attenzione primariamente al carico di lavoro, si focalizzano sulla vita

utile delle batterie. Nei paper considerati viene esaminato un caso di studio relativo ad un

lettore portatile MP3 di produzione, in grado di funzionare in due modalità, di cui la prima ad

alta fedeltà e maggiore consumo e la seconda a minore fedeltà e minor consumo.

La strategia che gli autori intendono attuare consiste nello stabilire una tensione di soglia al

di sotto della quale il sistema passa automaticamente dalla modalità ad alta fedeltà a quella

a minore fedeltà. Gli autori introducono un fattore di qualità pari alla frazione di tempo di

riproduzione ad alta fedeltà rispetto al tempo di riproduzione totale, quindi definiscono una

metrica P, pari al fattore di qualità moltiplicato per la durata, e scelgono il valore della tensione

di soglia che massimizzi P.

Resta da verificare che la metrica proposta sia proprio coincidente con le aspettative dell’utente

medio e i compromessi che è disposto ad accettare.

Pagina 25

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

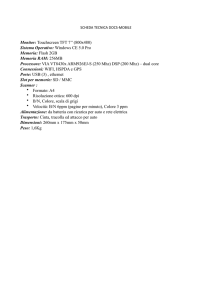

6 Appendice: Approfondimenti

6.0.1

PLL e latenze indotte

Il PLL (phase locked loop – anello ad aggancio di fase) è uno schema retroazionato molto comune, utilizzato nei moltiplicatori di frequenza a coefficiente variabile integrati nei moderni

microprocessori. La struttura a blocchi è riportata nel seguente diagramma:

Al primo blocco viene fornito come ingresso un segnale di riferimento (solitamente generato mediante un oscillatore quarzato). Tale blocco produce un’uscita proporzionata alla somma e alla

differenza fra le fasi del segnale di riferimento e l’uscita del divisore di frequenza (il cui ruolo è

descritto in seguito). Il filtro passa-basso lascia passare solamente la componente differenza,

dando origine ad una tensione di errore proporzionale alla differenza tra le fasi dei due segnali. La tensione errore pilota un oscillatore controllato in tensione (VCO) ad ampiezza fissa,

che produce un aumento o diminuzione di frequenza nella direzione che causa la diminuzione

dell’errore (in valore assoluto). Se la linea di retroazione non presentasse il divisore di frequenza,

ad aggancio avvenuto, la frequenza del VCO sarebbe pari alla frequenza del segnale di ingresso,

ma in presenza di un divisore di frequenza per N, la frequenza in uscita al VCO sarà pari a N

volte la frequenza di ingresso.

Esistono poi varie soluzioni sia per effettuare la squadratura del segnale in uscita (per esempio

per mezzo di un trigger di Schmitt), sia per realizzare il divisore di frequenza (per esempio per

mezzo di un contatore digitale).

In molti dei processori esaminati è possibile, nel quadro delle funzionalità di riduzione del consumo, spegnere il PLL. Appare quindi chiaro che, alla sua riaccensione, sia necessario attendere

tempi di aggancio e di stabilizzazione che sono di 3-4 ordini di grandezza superiori al ciclo di

clock. Ciò rende lo spegnimento del PLL una opzione compatibile con i tempi dei comandi

“umani”, ma poco praticabile in sistemi sottoposti a vincoli di real time sufficientemente stretti.

Tempi di stabilizzazione dello stesso ordine di grandezza sono necessari per il riaggancio del PLL

nel caso di mutamento del coefficiente di moltiplicazione del clock.

Pagina 26

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

Elenco degli acronimi

ACPI

Advanced configuration and power interface

DDR

Double data rate

DPM

Dynamic power management

CMOS

Complementary metal-oxide semiconductor

MOS

Metal-oxide semiconductor

PLL

Phase-locked loop

PWM

Pulse width modulation

VCO

Voltage-controlled oscillator

VRM

Voltage regulator module

VLIW

Very long instruction word

Pagina 27

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

Bibliografia

[1] Intel Corporation, IA-32 Intel Architecture Software Developer’s Manual - Volume 1: Basic

Architecture, order number: 24547-009, disponibile su developer.intel.com.

[2] Intel Corporation, IA-32 Intel Architecture Software Developer’s Manual - Volume 2: Instruction Set Reference, order number: 24547-109, disponibile su developer.intel.com.

[3] Intel Corporation, IA-32 Intel Architecture Software Developer’s Manual - Volume 3: System

Programming Guide, order number: 24547-209, disponibile su developer.intel.com.

[4] Intel Corporation, Intel Pentium 4 Processor VR-Down – Design Guidelines, November 2002,

order number: 249891-004, disponibile su developer.intel.com.

[5] Intel Corporation, Mobile Intel Pentium 4 Processor-M – Product Overview, January 2003,

order number: 250352-004, disponibile su developer.intel.com.

[6] Intel Corporation, Mobile Intel Pentium 4 Processor-M and Intel 852GM Chipset Platform – Design Guide, January 2003, order number: 25233-801, disponibile su

developer.intel.com.

[7] Intel Corporation, Intel 852GM Chipset Graphics and Memory Controller Hub (GMCH) – Datasheet, January 2003, order number:

25240-701, disponibile su

developer.intel.com.

[8] Intel Corporation, Intel 852GM Chipset Graphics and Memory Controller Hub (GMCH) – Datasheet, January 2003, order number:

25240-701, disponibile su

developer.intel.com.

[9] Intel Corporation, Mobile Intel Pentium III Processor-M – Datasheet, January 2003, order

number: 29834-006, disponibile su developer.intel.com.

[10] Intel Corporation, Intel Pentium III Processor with 512KB L2 Cache at 1.13GHz to 1.40GHz –

Datasheet, June 2002, order number: 249657-004, disponibile su developer.intel.com.

[11] Intel Corporation, Intel 80200 Processor based on Intel XScale Microarchitecture – Datasheet,

August 20002, order number: 273414-004, disponibile su developer.intel.com.

[12] Intel Corporation, Intel XScale Microarchitecture – Programmer’s Reference Manual, February

2001, order number: 273436-001, disponibile su developer.intel.com.

[13] Intel Corporation, Intel Low-Power Technologies – Bringing Longer Battery Life - and

Higher Productivity - to Mobile Computing, order number: 250366-001, disponibile su

developer.intel.com/design/mobile/perfbref/.

[14] ARM Limited, ARM9E-S, Technical Reference Manual, Revision 2, order number: DDI 0240A,

disponibile su www.arm.com/Documentation/.

[15] ARM Limited, ARM9E-S, Technical Reference Manual, Revision 2, order number: DDI 0240A,

disponibile su www.arm.com/Documentation/.

[16] ARM Limited, ARM1022E, Technical Reference Manual, order number:

disponibile su www.arm.com/Documentation/.

DDI 0237A,

[17] Motorola Incorporated, MC68EZ328 (DragonBall EZ) Integrated Portable System Processor

– Product Brief, Revision 2, October 2001, order number: MC68EZ328P/D, disponibile su

www.motorola.com/Documentation/ ;

Pagina 28

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT Gestione dinamica del consumo energetico nei sistemi embedded

[18] Motorola Incorporated, MC68EZ328 (DragonBall EZ) Integrated Portable System Processor –

User’s Manual, Revision 1, November 1998, order number: MC68EZ328UM/D, disponibile

su www.motorola.com/Documentation/;

[19] Moshovos, Memik, Mittal, Baniasadi, Choudhary, JETTY: Reducing Snoop-Induced Power

Consumption in Small-Scale, Bus-Based SMP Systems, Technical Report CPDC-TR-200005-007, Center for Parallel and Distributed Computing, Department of Electrical and

Computer Engineering, Northwestern University, Evanston IL, USA;

[20] IBM

and

MontaVista

Software,

Dynamic

Power

Management

Embedded

Systems,

Version

1.1,

November

2002,

available

www.research.ibm.com/arl/projects/papers/DPM V1.1.pdf;

for

at

[21] Lee, F. C. and Zhou X., Power Management Issues for Future Generation Microprocessors,

ISPSD ’99 - The 11th International Symposium on Power Semiconductor Devices and ICs,

proceedings, pages 27-33;

[22] Ishihara and Yasuura, Voltage Scheduling Problem for Dynamically Variable Voltage Processors, ISPLED ’98, International Symposium on Low-power electronics and design,

proceedings, pages: 197 - 202;

[23] Simunic, Benini, Acquaviva, Glynn and De Micheli, Dynamic Voltage Scaling and Power

Management for Portable Systems, DAC 2001, Las Vegas, Nevada, USA;

[24] Simunic, Benini, Glynn and De Micheli, Dynamic Power Management for Portable Systems,

MOBICOM 2000, Boston, Massachusetts, USA;

[25] Benini, Castelli, Macii and Scarsi, Battery-Driven Dynamic Power Management, IEEE Design

and Test of Computers, March/April 2001 (Vol. 18, No. 2), pages: 53-60;

[26] Benini, Castelli, Macii, Macii and Scarsi, Battery-Driven Dynamic Power Management

of Portable Systems, 13th International Symposium on System Synthesis (ISSS’00),

September 2000, Madrid, Spain, pages:

Pagina 29

c CEFRIEL 2002

Febbraio 2003 – Ver. 1.0 – XV Master IT