16/11/2007

Informatica

Pietro Storniolo

[email protected]

http://www.pa.icar.cnr.it/storniolo/info200708

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

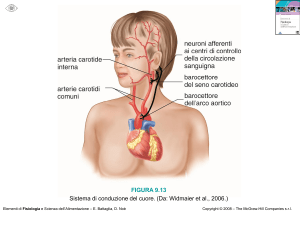

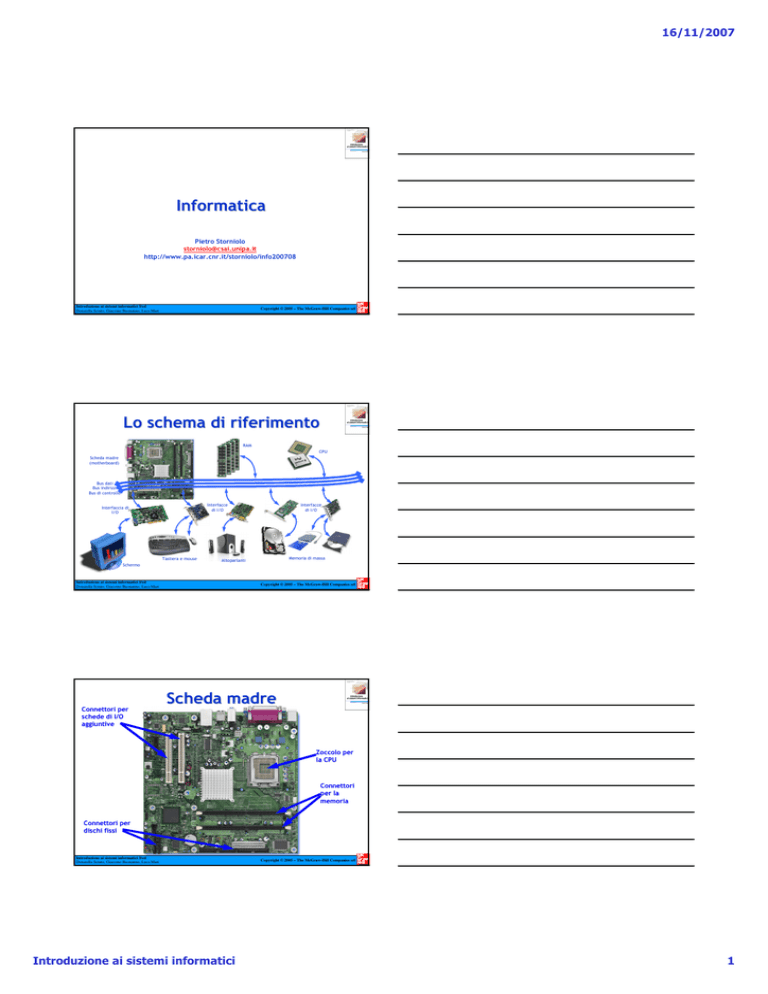

Lo schema di riferimento

RAM

CPU

Scheda madre

(motherboard)

Bus dati

Bus indirizzi

Bus di controllo

Interfacce

di I/O

Interfaccia di

I/O

Tastiera e mouse

Interfacce

di I/O

Memoria di massa

Altoparlanti

Schermo

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

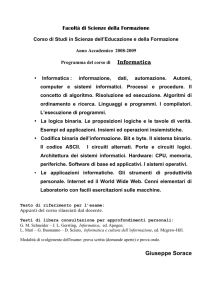

Connettori per

schede di I/O

aggiuntive

Copyright © 2005 – The McGraw-Hill Companies srl

Scheda madre

Zoccolo per

la CPU

Connettori

per la

memoria

Connettori per

dischi fissi

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Introduzione ai sistemi informatici

Copyright © 2005 – The McGraw-Hill Companies srl

1

16/11/2007

Collegamento a BUS

☺

Semplicità

Semplicità

•

☺

•

☺

utilizzo in mutua esclusione del bus

Limitatà

Limitatà capacità

capacità

•

regole per la comunicazione da parte di dispositivi diversi

Lentezza

•

aggiunta di nuovi dispositivi molto semplice

Standardizzabilità

Standardizzabilità

•

un’unica linea di connessione costi ridotti di produzione

Estendibilità

Estendibilità

al crescere del numero di dispositivi collegati

Sovraccarico del processore (CPU)

•

perchè funge da master sul controllo del bus

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Le infrastrutture HardWare

Il processore

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

CPU – Central Processing Unit

Unità

Unità Centrale di Elaborazione

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Introduzione ai sistemi informatici

Copyright © 2005 – The McGraw-Hill Companies srl

2

16/11/2007

Organizzazione tipica di un

calcolatore “bus oriented”

oriented”

CPU

Dispositivi di I/O

Unità di

controllo

Unità

aritmetico

logica (ALU)

Terminale

Stampante

Registri

CPU

Memoria

centrale

Unità

disco

Bus

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

L’ “esecutore”

esecutore”

Un calcolatore basato sull’

sull’architettura di Von Neumann esegue un

programma sulla base dei seguenti principi:

• dati e istruzioni sono memorizzati in una memoria unica che permette sia la

scrittura che la lettura;

• i contenuti della memoria sono indirizzati in base alla loro posizione,

indipendentemente dal tipo di dato o istruzione contenuto;

• le istruzioni vengono eseguite in modo sequenziale.

Il linguaggio per cui la CPU si comporta da esecutore è detto linguaggio

macchina.

macchina. Le istruzioni scritte in linguaggio macchina sono piuttosto

rudimentali:

• il concetto di tipo di dato è quasi assente,

• il numero di operandi è limitato (in genere non più di due),

• il numero di operazioni previste è ridotto.

Struttura istruzione

codice operativo

dest

src1

src2

Linguaggio assemblatore

add

R01

R02

R03

Linguaggio macchina

000000 00000 100000 00001 00010 00011

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Ciclo Fetch–

Fetch–Decode–

Decode–Execute

Fetch

Decode

Execute

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Introduzione ai sistemi informatici

Copyright © 2005 – The McGraw-Hill Companies srl

3

16/11/2007

Le parti di una CPU

Data path (o percorso dei dati)

dati)

• è la parte che si occupa dell’effettiva elaborazione dei dati;

• comprende dispositivi diversi

• una o più unità aritmetico-logiche, dette ALU (Arithmetic Logic Unit);

• alcune unità di memorizzazione temporanea, i registri, memoria ad alta velocità

usata per risultati temporanei e informazioni di controllo (il valore massimo

memorizzabile in un registro è determinato dalle dimensioni del registro).

Unità

Unità di controllo

• coordina le operazioni di tutto il processore (anche quelle del data path!);

• regola il flusso dei dati e indica quali registri debbano essere collegati agli

ingressi e all’uscita dell’ALU;

• invia all’ALU il codice dell’operazione da eseguire;

• riceve indicazioni sull’esito dell’operazione appena eseguita dall’ALU e

gestisce opportunamente queste informazioni;

• comprende alcuni registri di uso specifico

• Program Counter (PC) – qual è l’istruzione successiva;

• Instruction Register (IR) – istruzione in corso d’esecuzione;

• …

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Data Path

Registri

… … … …

R00 R01 R02 R03

X

Registri

ingresso ALU

add

Registro

uscita ALU

X

Y

A

L

U

X

+

Y

esito

X

+

Y

Y

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Unità di

controllo

PSW

Bus dati

Data path

Bus indirizzi

CPU

Bus controllo

Unità

Unità di controllo

IR

PC

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Introduzione ai sistemi informatici

Memoria

Copyright © 2005 – The McGraw-Hill Companies srl

4

16/11/2007

CPU

In grado di eseguire solo istruzioni

codificate in linguaggio macchina

Ciclo Fetch – Decode - Execute

1. Prendi l’istruzione corrente dalla memoria (quella individuata dal

contenuto del PC) e mettila nell’IR (Instruction Register),

contemporaneamente incrementa il Program Counter (PC) in modo che

contenga l’indirizzo dell’istruzione successiva (fetch)

2. Determina il tipo di istruzione da eseguire (decode)

3. Se l’istruzione usa dei dati presenti in memoria, determinane la

posizione;

4. Carica la parola, se necessario, in un registro della CPU;

5. Esegui l’istruzione (execute)

6. Torna al punto 1 e inizia a eseguire l’istruzione successiva.

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Tre tipologie di istruzioni

Istruzioni aritmeticoaritmetico-logiche (Elaborazione dati)

• Somma, Sottrazione, Divisione, …

• And, Or, Xor, …

• Maggiore, Minore, Uguale, Minore o uguale, …

Controllo del flusso delle istruzioni

• Sequenza

• Selezione semplice, a due vie, a n vie, …

• Ciclo a condizione iniziale, ciclo a condizione finale, …

Trasferimento di informazione

• Trasferimento dati e istruzioni tra CPU e memoria

• Trasferimento dati e istruzioni tra CPU e dispositivi di

ingresso/uscita (attraverso le relative interfacce)

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Migliorare le prestazioni di una CPU

La frequenza di clock

• influenza direttamente il tempo di ciclo del data path e

quindi le prestazioni di un calcolatore;

• è limitata dalla tecnologia disponibile.

Il parallelismo permette di migliorare le prestazioni

senza modificare la frequenza di clock. Esistono

due forme di parallelismo:

• parallelismo a livello delle istruzioni

(architetture pipeline o architetture superscalari);

• parallelismo a livello di processori

(Array computer, multiprocessori o multicomputer).

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Introduzione ai sistemi informatici

Copyright © 2005 – The McGraw-Hill Companies srl

5

16/11/2007

Evoluzione delle CPU Intel

CPU

Anno

Frequenza Dim. registri Numero di

(MHz)

bus dati

transistor

MHz)

8086

1978

4.77 — 12

8/16

29 000

80286

1982

8 — 16

16/16

134 000

80386

1986

16 — 33

32/32

275 000

80486

1989

33 — 50

32/32

1 200 000

Pentium

1993

60 — 200

32/64

3 100 000

Pentium II

1997

233 — 400

32/64

7 500 000

Pentium III

(Willamette)

Pentium 4

1999

450 — 1133

32/64

24 000 000

2000

1300 — 2000

32/64

42 000 000

(Northwood)

2002

2000 — 3400

32/64

55 000 000

(Prescott)

2004

2800 — 3800

32/64

125 000 000

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Legge di Moore

Osservazione fatta da Gordon Moore nel 1965:

il numero dei transistor per cm2

raddoppia ogni X mesi

In origine X era 12. Correzioni successive hanno

portato a fissare X=18. Questo vuol dire che c’è un

incremento di circa il 60% all’anno.

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

# Transistor [CPU Intel]

Intel]

100 000 000

10 000 000

1 000 000

100 000

1989

1991

1993

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Introduzione ai sistemi informatici

1995

1997

1999

Copyright © 2005 – The McGraw-Hill Companies srl

6

16/11/2007

Legge di Moore e progresso

Il progresso della tecnologia provoca un aumento

del numero di transistor per cm2 e quindi per chip.

Un maggior numero di transistor per chip permette

di produrre prodotti migliori (sia in termini di

prestazioni che di funzionalità

funzionalità) a prezzi ridotti.

ridotti.

I prezzi bassi stimolano la nascita di nuove

applicazioni (e.g. non si fanno video game per

computer da milioni di $).

Nuove applicazioni aprono nuovi mercati e fanno

nascere nuove aziende.

aziende.

L’esistenza di tante aziende fa crescere la

competitività

competitività che, a sua volta, stimola il progresso

della tecnologia e lo sviluppo di nuove tecnologie.

tecnologie.

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Le infrastrutture HardWare

La memoria centrale

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

La memoria

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Introduzione ai sistemi informatici

Copyright © 2005 – The McGraw-Hill Companies srl

7

16/11/2007

La memoria

Supporto alla CPU:

CPU: deve fornire alla CPU dati e

istruzioni il più

più rapidamente possibile

Archivio:

Archivio: deve consentire di archiviare dati e

programmi garantendone la conservazione e la

reperibilità

reperibilità anche dopo elevati periodi di tempo

Diverse esigenze:

• velocità per il supporto alla CPU

• non volatilità ed elevate dimensioni per l’archivio

Diverse tecnologie

• elettronica: veloce, ma costosa e volatile

• magnetica e ottica: non volatile ed economica, ma molto

lenta

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Criteri di caratterizzazione di una memoria

Velocità

Velocità

Volatilità

Volatilità

Capacità

Capacità

Costo (per bit)

Modalità

Modalità di accesso

•

•

•

•

diretta (o casuale)

sequenziale

mista

associativa

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

La memoria centrale

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Introduzione ai sistemi informatici

Copyright © 2005 – The McGraw-Hill Companies srl

8

16/11/2007

La memoria centrale (RAM)

Mantiene

al proprio interno i dati e

le istruzioni dei programmi in esecuzione

Memoria ad accesso “casuale”

casuale”

Tecnologia elettronica

• veloce ma volatile e costosa

Due

“eccezioni”

eccezioni”

• ROM: elettronica ma permanente e di sola lettura

• Flash: elettronica ma non volatile e riscrivibile

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Memoria vs. CPU

Le CPU sono sempre state più

più veloci delle memorie

• l’aumento di integrazione ha consentito di realizzare CPU

pipeline e super scalari, molto efficienti e veloci;

• nelle memorie è aumentata la capacità più che la velocità.

L’accesso alla memoria passa attraverso il bus

• la frequenza di funzionamento del bus è molto più bassa

di quella della CPU;

• il bus può essere impegnato ad effettuare trasferimenti

controllati da dispositivi di I/O “autonomi” (e.g. DMA).

È difficile riordinare le istruzioni in modo da poter

sfruttare i tempi di attesa della memoria.

È possibile fare memorie molto veloci se stanno nel

chip della CPU, ma sono piccole e costose.

costose.

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Le memorie gerarchiche

Memorie di gran capacità

capacità, relativamente lente,

economiche ed accessibili tramite il bus:

• MGL ovvero Memoria Grossa e Lenta;

• dimensioni pari a circa 10 unità;

• tempo di accesso (TA) di circa 10 unità.

Memorie veloci, integrate nello stesso chip della

CPU, ma costose:

• MPV ovvero Memoria Piccola e Veloce;

• dimensioni pari a circa 1 unità;

• tempo di accesso pari a circa 1 unità.

Obiettivo: realizzare una memoria grossa e veloce

• dimensioni pari a circa quelle della memoria grossa;

• prestazioni pari a circa quelle della memoria veloce.

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Introduzione ai sistemi informatici

Copyright © 2005 – The McGraw-Hill Companies srl

9

16/11/2007

La memoria centrale

Tecnologia

elettronica (veloce ma volatile)

volatile)

di memoria:

memoria:

ai livelli più

più alti corrispondono le tecnologie

più

più veloci ma anche più

più costose

Gerarchia

• cache interna (Static RAM – SRAM)

• cache esterna (SRAM)

• memoria RAM

(Dynamic RAM – DRAM e sue varianti)

• area di swap su memoria di massa

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Memoria cache: SRAM

Interna (L1) stessa frequenza della CPU

Esterna (L2 e/o L3)

• Tre diverse posizioni/configurazioni

• Saldata sulla motherboard

• Card Edge Low Profile (CELP) socket

• COAST (Cache On A STick) module

• Diverse tipologie

• Asynchronous SRAM (più economica),

TA compreso tra 12 e 20ns, OK per bus tra 50 e 66 MHz

• Synchronous Burst SRAM (Synch SRAM)

Bus fino a 66 MHz

Bus oltre i 66 MHz

• Synchronous Pipelined Burst SRAM (PB SRAM)

TA compreso tra 4.5 e 8ns, OK per bus fino a 133 MHz

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Memoria centrale – DRAM

Fast Page Mode DRAM (FPM DRAM)

DRAM)

• TA=70-60ns

• Per la lettura si attiva la riga, la colonna, si validano i dati, si

trasferiscono i dati, poi si disattiva la colonna

• I miglioramenti di velocità nascono dal progresso della tecnologia di

integrazione.

Extended Data Out DRAM (EDO DRAM)

DRAM)

• TA = 70-50ns

• Non richiede la disattivazione della colonna e del buffer di uscita; 60ns

è il minimo per bus a 66MHz

Burst EDO DRAM (BEDO DRAM)

DRAM)

• Evoluzione di EDO DRAM

(pipeline + 2-bit burst counter)

• Mai davvero supportata.

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Introduzione ai sistemi informatici

Copyright © 2005 – The McGraw-Hill Companies srl

10

16/11/2007

Memoria centrale – DRAM

Synchronous DRAM (SDRAM)

SDRAM)

• Sfrutta la sequenzialità delle richieste: una volta trovato il primo dato

gli altri vengono recuperati velocemente.

• Fornisce dati fino a 10ns (100MHz)

PC133 SDRAM

• Evoluzione della SDRAM per bus a 133MHz

• Trasferimento dati fino a 1.6GBps

Double Data Rate DRAM (DDR

(DDR DRAM)

DRAM)

• Sfrutta entrambi i fronti del clock per trasferire dati: raddoppia la

frequenza efficace non quella effettiva.

Direct Rambus DRAM (DRDRAM

(DRDRAM))

• Risultato della collaborazione tra Intel e Rambus

• Nuova architettura: 600-800MHz (1000MHz nel 2001)

con bus di sistema a 133MHz.

• 1 canale arriva fino a 1.6GBps (4 canali 6.4 GBps)

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Packaging

Fino all’

all’inizio degli anni ‘90 la memoria veniva

prodotta, acquistata e installata su chip singoli

• densità variabili da 1 Kbit a 1 Mbit;

• i PC avevano zoccoli vuoti dove inserire altri chip.

Oggi si monta un gruppo di chip, tipicamente 8 o

16, su un piccola scheda stampata che si vende

come unità

unità minima installabile nei PC

• SIMM (Single Inline Memory Module) se la fila di connettori

si trova da un solo lato della scheda;

• DIMM (Dual Inline Memory Module) se i connettori si

trovano su ambedue i lati della scheda

Sia SIMM che DIMM sono a volte dotate di un codice

di rilevazione o di correzione dell’

dell’errore.

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Memoria centrale – Chip

Single Inline Memory Module (SIMM)

SIMM)

• 30/72 pin sullo stesso lato della scheda;

• trasferimento dati a 8/32 bit per volta;

• utilizzabili “a coppie”.

Dual InIn-line Memory Module (DIMM

(DIMM))

• 168 pin su due lati;

• 64 bit alla volta;

• utilizzabili anche singolarmente

RIMM

• Moduli di RDRAM;

• interfaccia DIMM 100MHz.

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Introduzione ai sistemi informatici

Copyright © 2005 – The McGraw-Hill Companies srl

11

16/11/2007

Le infrastrutture HardWare

La memoria di massa

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

La memoria di massa

(magnetica)

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Una gerarchia di memoria

Ottenuta per “generalizzazione”

generalizzazione” dell’

dell’applicazione

del principio di località

località e tipicamente costituita da

1.

2.

3.

4.

5.

registri contenuti nella CPU (qualche KB)

cache (da circa 32KB a circa 1024KB)

memoria principale (da circa 64MB a qualche GB)

dischi fissi (da qualche GB a qualche TB)

nastri magnetici e dischi ottici (da qualche GB a qualche

TB per ogni supporto)

Man mano che ci si sposta verso il basso nella

gerarchia aumenta il valore dei parametri

fondamentali:

•

•

•

aumenta il tempo di accesso;

aumenta la capacità di memorizzazione;

ma diminuisce il costo per bit.

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Introduzione ai sistemi informatici

Copyright © 2005 – The McGraw-Hill Companies srl

12

16/11/2007

Cache II liv

Scheda madre (motherboard)

Cache I liv

RAM

Supporti esterni

tecnologia

magnetica

(HD esterni)

tecnologia

ottica

(CD, DVD)

tecnologia

elettronica

(flash disk)

Involucro esterno del calcolatore (case)

CPU

Registri

Circuito Integrato (chip)

Una gerarchia di memoria

Disco fisso (hard disk)

tecnologia magnetica

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Caratteristiche dei diversi livelli

Livello

Capacità

Capacità

Tempo di accesso

Transfer rate

(GB/s)

Registri

~ 1 KB

~ 0.2 ns

(1 ciclo di clock)

–

~ 32 KB

~ 0.4 ns

(2/4 cicli di clock)

–

~ 100

Cache I livello

Cache II livello

~ 1/2 MB

~ 1/2 ns

(5/10 cicli di clock)

Cache III livello

~ 2/8 MB

~ 5 ns

~ 50

Memoria

centrale

~ 2/8 GB

~ 50 ns (1ª parola richiesta)

~ 10 ns (parole successive)

~ 5/10

Dischi interni

> 300 GB

~ 10 ms

0.15/0.6

Dischi esterni

> 300 GB

~ 10 ms

~ 0.05

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Dischi magnetici

Sono piatti d’alluminio (o di altro materiale)

ricoperti di materiale ferromagnetico.

ferromagnetico.

Fattore di forma (diametro)

• sempre più piccolo (consente velocità di rotazione

maggiori);

• 3.5 pollici per i sistemi desktop e fino a 1 pollice per i

mobili.

Testina di un disco (strumento di lettura/scrittura)

• è sospesa appena sopra la superficie magnetica

• scrittura: il passaggio di corrente positiva o negativa

attraverso la testina magnetizza la superficie

• lettura: il passaggio sopra un’area magnetizzata induce

una corrente positiva o negativa nella testina.

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Introduzione ai sistemi informatici

Copyright © 2005 – The McGraw-Hill Companies srl

13

16/11/2007

Tracce e settori

Traccia (track):

(track): sequenza circolare di bit scritta mentre il

disco compie una rotazione completa

Settore (sector)

sector): parte di una traccia corrispondente a un

settore circolare del disco

Formattazione:

Formattazione: operazione che predispone tracce e settori

per la lettura/scrittura

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Spazi tra

tracce

Copyright © 2005 – The McGraw-Hill Companies srl

Settore

Tracce

e

settori

Tracce

Spazi tra

record

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Copyright © 2005 – The McGraw-Hill Companies srl

Schema di un Hard Disk

Superficie 7

Testina di

lettura/scrittura

(una per superficie)

Superficie 6

Superficie 5

Superficie 4

Superficie 3

Superficie 2

Superficie 1

Superficie 0

Direzione del

movimento

Le tracce in grigio formano un “cilindro”

Introduzione ai sistemi informatici 3/ed

Donatella Sciuto, Giacomo Buonanno, Luca Mari

Introduzione ai sistemi informatici

Copyright © 2005 – The McGraw-Hill Companies srl

14