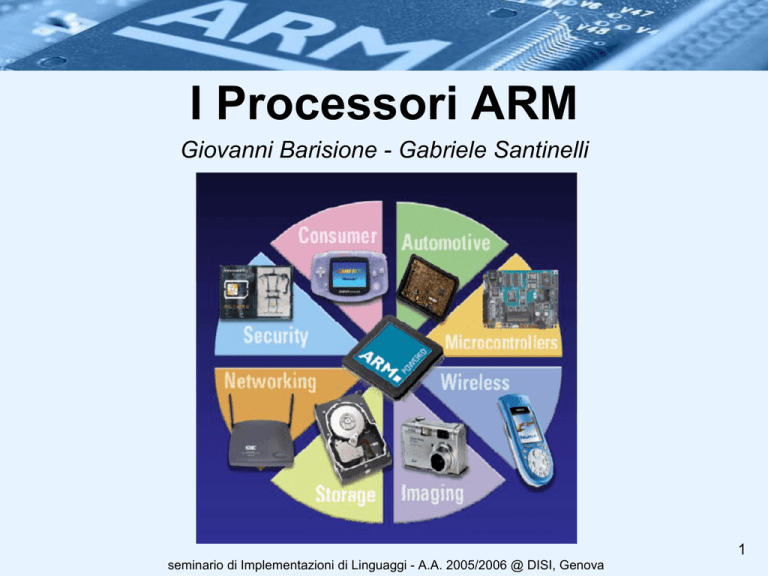

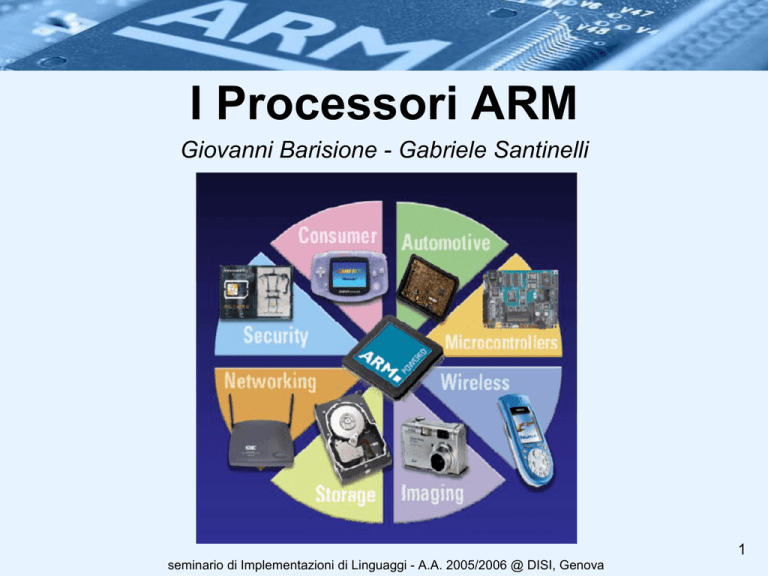

I Processori ARM

Giovanni Barisione - Gabriele Santinelli

seminario di Implementazioni di Linguaggi - A.A. 2005/2006 @ DISI, Genova

1

ACORN Atom (1981) & BBC Micro (1982)

Primi home computer della Acorn, usciti nei primi anni ‘80.

Entrambi basati sul processore MOS Technology 6502 del 1975:

• 8bit

• economico: costava 1/6 rispetto ai concorrenti (Motorola, Intel)

• ottime prestazioni rispetto ai concorrenti

2

ARM1 (1985) (#1)

Nel 1983 il 6502 è piuttosto datato: i personal

computer concorrenti ormai sfoggiano CPU a 16bit.

Acorn testa tutte le CPU a 16 e 32bit presenti sul

mercato ma nessuna la soddisfa appieno. Decide

quindi di crearsi il proprio processore da zero,

basandosi sul set di istruzioni del ben noto 6502.

La ora decantata semplicità del nascente processore ARM1, era in

principio una neccessità. Si narra, infatti, che i progettisti incaricati

fossero alle prime armi nella progettazione di processori; fu questo che

impedì all’ARM1 di diventare troppo complesso, decretandone così la

sua fortuna.

Si decide di puntare su un processore con un set di istruzioni a

lunghezza fissa e un modello load/store.

3

ARM1 (1985) (#2)

Il team di sviluppo è composto da 6 persone.

Il primo set di istruzioni viene scritto in BASIC, cosa che permette di

sviluppare un prototipo in tempi molto brevi.

In BASIC è anche il simulatore event-driven che permette il supporto

dei chip, e dei vari controller della macchina.

L’ARM1 viene commercializzato come coprocessore aggiuntivo per il

BBC Micro.

Nell’attesa di un computer basato su ARM, Acorn produce una

versione “home” del BBC Micro ma si rivela un flop. In seguito alla crisi

economica, Acorn viene acquistata da Olivetti.

4

ARM2 (1987)

Ci vogliono altri due anni prima che

Archimedes, il primo computer basato

sul processore ARM (in realtà ARM2),

veda la luce.

Primo processore ARM immesso sul

mercato.

• 32bit data bus

• 26bit address space

• 16 registri a 32bit

• 30 000 transistors (contro i 68 000 del

Motorola 68000)

• no microcodice (RISC)

• no cache (cosa abbastanza comune

all’epoca)

5

Da Acorn a ARM Ltd (fine ‘80)

Alla fine degli anni ‘80 inizia una

collaborazione con Apple per la nuova

versione dell’ARM.

Il lavoro Diventa così importante che nel

1990 viene creata una nuova società:

ARM Ltd (qui ARM assume il significato

di Advanced RISC Machines, sostituendo

il precedente di Acorn RISC Machines) che contiene il team del design.

L’ARM Ltd non produce microprocessori ma progetta e vende

proprietà intellettuale.

Cambia così la numerazione: vengono saltati gli ARM4 e 5 e si passa

direttamente all’ARM6 e alle sue varianti.

6

ARM3 (1990)

Successore dell’ARM2, prima CPU della ARM Ltd.

• 4Kb di cache.

ARM 610 (1991)

Nel 1991 Apple usa una versione dell’ARM6

la 610 per le prime serie di PDA come l’Apple

Newton, conosciuti anche come

MessagePad.

Nel 1994 verrà poi utilizzato anche dalla

Acorn per le cpu dei suoi RiscPC.

Questa versione introduceva un

indirizzamento a 32 bit con 4K di cache e con

la possibilità di passare dalla modalità bigendian alla little-endian; fu prodotto a diverse

velocità: 20Mhz, 30Mhz e 33Mhz.

7

Evoluzione (#1)

8

Evoluzione (#2)

9

RISC vs CISC (#1)

RISC (Reduced Instruction Set Computer)

• il concetto nasce nel 1974 da John Cocke (IBM)

• solo il 20% delle istruzioni macchina sono molto usate

• la complessità si sposta dall’HW al SW (compilatore)

• meno istruzioni significa meno transistor

• richiede più linee di codice di un CISC (più memoria)

CISC (Complex Instruction Set Computer)

• definizione retroattiva introdotta per distinguerli dai RISC

• microcodice, risiede in una ROM e traduce ogni singola istruzione

• istruzioni più vicine a quelle dei linguaggi di alto livello

MIPS (Microprocessor without Interlocked Pipeline Stages)

• minimizza le chiamate alla memoria esterna arricchendo la CPU di

registri

10

RISC vs CISC (#2)

11

Post-RISC

Oggi la distinzione tra RISC e CISC è molto meno marcata. Le CPU

RISC sono diventate molto più complesse mentre i CISC sono

diventati più efficienti. Infatti:

• il PPC 601 (RISC) supporta più istruzioni di un Pentium (CISC)!

• la famiglia Pentium II è definita da Intel come CRISC

12

Il mercato dei processori RISC

Per motivi di retrocompatibilità, i

processori RISC non sono mai entrati

negli home-computer.

Sono invece stati introdotti fin da subito nel mondo dei

cellulari/palmari, perchè in forte espansione proprio in quel periodo.

Oggi la stessa Intel dichiara di produrre più CPU ARM che x86.

13

Acorn VS Apple (1994)

As a founder member,

Acorn is delighted

to welcome Apple

to the RISC Club.

After 11 years of development and 7 years of production, we at Acorn are still

marveling at the sheer power, performance and potential of 32-bit RISC

technology.

Our ARM 32-bit RISC processors have delivered these capabilities to our

many customers in education, the home and industry worldwide, in our products

since 1987.

So it comes at little surprise to hear that Apple's new desktop range also

incorporates 32-bit RISC technology.

Oh well. Better late than never.

Dal Times, 15 marzo 1994

14

ARMv4 - Memoria

ARM è un processore a 32 bit ma è anche in grado di manipolare

dati a 8bit (byte) e a 16bit (halfword).

• Le word a 32 bit sono allineate in memoria ad indirizzi multipli di 4.

• Le halfword sono allineate ad indirizzi multipli di 2 mentre i byte sono

singolarmente indirizzabili in memoria.

15

ARMv4 - Modi Operativi

Esistono sette modi di funzionamento supportati dal processore

Il modo può essere cambiato via software, in modalità privilegiata oppure

attraverso un’eccezione.

16

ARMv4 - Registri (#1)

Il processore ARM è dotato di 37 registri:

• 31 registri generici

•R13 corrisponde allo Stack Pointer (SP)

•R14 corrisponde al Link Register (LR)

•R15 corrisponde al Program Counter (PC)

• 6 registri di stato (di cui 5 di salvataggio)

I registri sono divisi in banchi parzialmente sovrapposti, uno per

ogni modo operativo esistente (System e User usano lo stesso

banco).

Quindi ci sono 15 registri d’uso generale (da R0 a R14), uno o due

registri di stato (quello corrente ed eventualmente quello di

salvataggio) ed il PC. Tutti i registri tranne quelli di stato possono

essere utilizzati da tutte le istruzioni di tipo generale.

17

ARMv4 - Registri (#2)

18

ARMv4 - Registri (#3)

La presenza di una coppia specifica di registri SP e LR per ogni

modo operativo facilita l’associazione ai singoli modi di uno stack

privato e rende più efficiente il ritorno da eccezione.

Nel modo FIQ esiste una copia fisica anche dei registri da R8 a

R12: permette di servire una chiamata ad una interruzione veloce

senza dover salvare quei registri, ottenendo una migliore efficienza

nella realizzazione della corrispondente routine di servizio.

19

ARMv4 - CPSR (#1)

Il Current Program Status Register è il registro di stato. Include i

bit di condizione (i 4 bit più significativi), le maschere per le

interruzioni e la codifica del modo operativo.

•bit da 0 a 4 (M): modo operativo

•bit 5 (T): set di istruzioni Thumb a 16bit, on-off

•bit 6 (F): interruzioni “fast” (FIQ), on-off

•bit 7 (I): interruzioni generiche (IRQ), on-off

•bit 28 (V): indica errore di overflow

•bit 29 (C): indica il riporto

•bit 30 (Z): indica un risultato zero

•bit 31 (N): indica un risultato negativo

20

ARMv4 - CPSR (#2)

• C, Z e N possono essere modificati in base al risultato di una

istruzione di elaborazione dei dati. I bit di condizione vengono modificati

solo se il bit S (Set Condition Code) è impostato a 1. Questo si ottiene

postponendo la lettera S al nome dell’istruzione. (Es. ADD→ADDS,

SUB→SUBS)

• V (Overflow) è modificabile solo dalle operazioni aritmetiche.

• C, le istruzioni additive (ADDS, CMN...) lo impostano a 1 se nella

somma risulta un riporto dal bit più significativo. Le istruzioni sottrattive

(CMP, SUBS...) lo impostano a 0 se nella differenza risulta un “prestito”

nel bit più significativo.

Il registro SPSR (Saved Program Status Register) ha il compito di

preservare il valore di CPRS durante la gestione di un’eccezione. C’è

un SPSR per ogni modo operativo tranne che per il modo User/System

durante il quale non è prevista la gestione di un’eccezione.

21

ARMv4 - Stack (#1)

Nei processori ARM gli stack vengono gestiti tramite le istruzioni

LDM (Load Multiple Register) e STM (Store Multiple Register).

Sono supportati quattro formati diversi di stack, ognuno dei quali

viene specificato attraverso una sigla di due caratteri preposta al

nome dell’istruzione LDM o STM.

Questi sono i tipi di stack:

•Full Stack: SP punta all’ultimo dato inserito

•Empty Stack: SP punta alla prima posizione di memoria libera

•Ascendente: SP viene incrementato per effetto dell’inserimento

•Discendente SP viene decrementato per effetto dell’inserimento

22

ARMv4 - Stack (#2)

23

ARMv4 - Eccezioni (#1)

Sono previsti 8 tipi d’eccezione, ad ognuno è associato un hard

vector. L’elaborazione di un’eccezione forza il PC ad assumere il

valore del corrispondente vettore.

Di norma a quell’indirizzo è collocata un’istruzione di salto alla

corrispondente routine di servizio, tranne per l’ultima eccezione,

dove può tranquillamente iniziare la routine.

24

ARMv4 - Eccezioni (#2)

25

ARMv4 - Gestione delle priorità dei dispositivi

Essendo le linee di ingresso IRG e FIQ uniche, i dispositivi di

ciascuna delle due classi di interruzioni devono essere identificati in

una fase iniziale delle rispettive routine di servizio.

Al fine di velocizzare tale fase di identificazione e gestire

correttamente le priorità dei dispositivi, il sistema può includere

hardware aggiuntivo (interrupt controller).

ARMv4 - Priorità delle eccezioni

Nel caso che più eccezioni siano

contemporaneamente pendenti, il

processore ARM utilizza la seguente

tabella delle priorità.

26

ARMv4 - Istruzioni Condizionali

Perchè ogni singola istruzione venga effettivamente eseguita devono

essere preliminarmente soddisfatte alcune condizioni, valutando i bit

di condizione. Il nome di ogni istruzione può essere esteso:

27

ARMv4 – Pipeline (#1)

A partire dall’ARM2 il processore è dotato di una pipeline a 3 stadi.

• Fetch: copia il codice dell’istruzione dalla memoria

• Decode: decodifica l’istruzione leggendone gli operandi

• Execute: l’ALU esegue l’istruzione ed effettua il write-back

Si ottiene quindi una latenza di tre cicli, mentre il throughput è di una

istruzione per ciclo.

28

ARMv4 – Pipeline (#2)

Il PC è sempre due istruzioni avanti rispetto all’istruzione in

esecuzione.

Nel caso di branch due cicli di istruzioni vanno persi (perchè la

pipeline deve nuovamente riempirsi), per questo è preferibile l’uso di

istruzioni condizionali.

con “branch”

con istruzione condizionale

CMP

BEQ

MOV

MOV

CMP R0,#0

MOVNE R1,#1

MOVNE R2,#2

R0,#0

<offset>

R1,#1

R2,#2

29

ARMv4 – Istruzioni (#1)

Possiamo dividere le istruzioni in categorie funzionali:

3) Istruzioni per l’elaborazione dei dati

Le regole base per questo tipo di istruzioni sono:

3 operandi: 2 sorgenti, 1 destinatario

tutti gli operandi sono a 32bit, sia i registri che le costanti

il risultato è a 32bit ed è posto in un registro

In questa classe troviamo le operazioni aritmetiche e logiche (ADC,

ADD, AND, BIC, EOR,MUL,ORR, RSB, RSC, SBC, SUB), quelle per

il movimento tra i registri (MOV, MVN) e quelle di confronto (CMN,

CMP, TEQ, TST)

30

ARMv4 – Istruzioni (#3)

2) Istruzioni per l’accesso alla memoria

In questa classe vi sono le istruzioni per il movimento dei dati da

memoria a registro (load) e viceversa (store). Vi sono poi alcune

varianti per il caricamento di dati da 8 e 16bit con e senza segno e

per il movimento multiplo che coinvolge più registri.

Le istruzioni sono: LDR, LDRB, STR, STRB, LDRH, LDRSB,

LDRSH, STRH, LDMxx, STMxx

31

ARMv4 - Istruzioni (#2)

Aritmetiche e logiche:

ADD

SUB

RSB

MUL

ORR

BIC

r0,

r0,

r0,

r0,

r0.

r0,

r1,

r1,

r1,

r1,

r1.

r1,

r2

r2

r2

r2

r2

r2

//

//

//

//

//

//

r0=r1+r2

r0=r1-r2

r0=r2-r1

r0=r1*r2

r0=r1 or r2

r0=r1 and not

ADC

SBC

RSC

AND

EOR

r2

r0,

r0,

r0,

r0,

r0,

r1,

r1,

r1,

r1,

r1,

r2

r2

r2

r2

r2

//

//

//

//

//

r0=r1+r2+C

r0=r1-r2+C-1

r0=r2-r1+C-1

r0=r1 and r2

r0=r1 xor r2

Movimento tra i registri

MOV r0, r2

// r0=r2

MVN r0, r2

// r0= not r2

Operazioni di confronto

CMP r1, r2

TST r1, r2

//set cc on r1-r2

CMN r1, r2 //set cc on r1+r2

//set cc on r1 and r2 TEQ r1, r2 //set cc on r1 xor r2

Con queste ultime vengono modificati solo i bit di condizione(cc) del

CPSR

32

ARMv4 – Istruzioni (#4)

3) Istruzioni di salto

Queste istruzioni hanno l’effetto di caricare un nuovo valore nel

registro PC(R15), valore che viene calcolato come somma del PC

corrente e dell’offset relativo specificato nella codifica dell’istruzione.

Di questa classe fanno parte 2 tipologie di istruzioni B(branch) e

BL(branch and link)

B <indirizzo>

BL <indirizzo>

//PC<-indirizzo

//LR<-PC-4 (salva PC in LR)

PC<-indirizzo

B Lab1 //salta al label “lab1”

BEQ Lab2

//se z=1 allora salta al label “lab2”, altrimenti prosegue

BLVC SUBR1

//se V=0 chiama la subroutine “SUBR1”

33

Tecnologie Proprietarie

A cominciare con ARMv4 sono stati

introdotti:

• Thumb

• Thumb-2

Mentre a partire da ARMv5 sono

state aggiunte le estensioni:

• Jazelle

• TrustZone

• IEM (Intelligent Energy Manager)

• SIMD

• NEON

34

Thumb Technology (#1)

Thumb è un estensione all’architettura

ARM a 32bit che permette una densità di

codice molto elevata.

Il set di istruzioni Thumb (ISA) contiene un

sottoinsieme delle istruzioni ARM a 32bit

più comunemente usate ma, a differenza di

queste, si tratta di istruzioni compresse a 16bit.

In esecuzione le istruzioni Thumb a 16bit vengono decodificate,

svolgendo così lo stesso lavoro dei loro equivalenti ARM a 32bit.

Vantaggi:

• L’aumento di densità del codice è stimato intorno al 30% e non comporta

peggioramento delle prestazioni.

• Usando una combinazione di codice ARM e Thumb, il programmatore è

in grado di bilanciare costi, performance e consumi.

35

Thumb Technology (#2)

Svantaggi:

• Il programmatore deve essere in grado di identificare le routines veloci

(che sfrutteranno le istruzioni ARM a 32bit) da quelle ottimizzabili mediante

le istruzioni Thumb.

• Molte istruzioni ARM non hanno equivalenti in Thumb (per esempio

quelle per l’accesso a funzioni speciali come SIMD/DSP, o le istruzioni

privilegiate). In questi casi il codice Thumb deve chiamare una funzione

contenente il codice ARM da eseguire, prima di poter tornare al codice

Thumb.

• 16bit non sono abbastanza per mantenere la capacità di eseguire in

modo condizionale ogni istruzione.

36

Thumb-2 Technology

Aggiunge diversi miglioramenti alla tecnologia Thumb:

• nuove istruzioni a 16bit per migliorare il flusso del programma

• nuove istruzioni a 32bit per sopperire alle istruzioni ARM ancora mancanti

• nuove istruzioni a 32bit che migliorano il set di istruzioni di ARM

Nella maggior parte delle applicazioni le istruzioni Thumb-2

diventano lo standard, specialmente nelle situazioni in cui il rapporto

costi, performance e consumi è poco chiaro.

• Non c’è più bisogno di mescolare istruzioni ARM e Thumb.

• Ritorno all’esecuzione condizionale delle istruzioni (IT).

37

StrongARM (1995)

Era una delle più veloci versioni

dell’architettura ARM. Creato dalla

Digital è stato disegnato soprattutto per

l’uso negli strumenti portabili nei quali

occorreva un basso consumo

energetico, era usato in palmari e anche

in decoder e box digitali per la

televisione.

Lo StrongArm portò i RiscPC da 40 a 200-300Mhz e fu il primo a

dividere tra instruction e data cache con entrambe le cache di 16Kb.

La pipeline viene portata da 3 a 5 stadi.

Nel 1995 l’SA-100 viene immediatamente incorporato nei nuovi modelli

dell’Apple Newton.

38

Da StrongARM a XScale (2000)

Successivamente la Digital Semiconductor, viene ceduta alla Intel

che usa lo StrongARM per sostituire i suoi i960 che avevano

dominato il mercato dei processori RISC fino ai tardi anni ‘90.

Con XScale nasce la generazione v5 di ARM che sostituisce gli

StrongARM ancora basati sulla v4. Tutti i processori di questo tipo

sono basati su un processore a 32 bit con Thumb e hanno 2 cache

da 32kb di tipo instruction e data e anche 2 mini-cache da 2kb.

E’ usato come processore in tantissimi tipi di palmari e anche sui pc

desktop RISC Iyonix della Acorn e su molti media-player portabili e

grazie alla collaborazione con Apple anche sui prossimi Ipod.

39

XScale (2000)

La pipeline si suddivide in 3 sotto pipeline: Main Execution, Memory e

MAC con in tutto 7/8 stadi, con di norma 1 ciclo per stadio.

40

XScale

I tre pipeline possono essere occupati

simultaneamente (comportamento di tipo

superscalare).

I tre pipeline funzionano in maniera asincrona.

Conclusione: le istruzioni possono completare

l’esecuzione fuori ordine se non ci sono

dipendenze tra i dati.

Per ottimizzare l’uso delle pipeline: la predizione dei salti.

PXA255 effettua una predizione dinamica basata sulla “storia

passata” di ciascun salto, la storia è memorizzata nel BTB (Branch

Target Buffer), la storia di un salto può assumere 4 possibili stati:

Strongly Not Taken, Weakly Not Taken, Weakly Taken e Strongly

Taken.

41

Prodotti ARM - Gaming

Nintendo DS

Sony PSP

ARM7 / ARM9

ARM9

Nintendo GB Advance

ARM7 / ARM9

42

Prodotti ARM - Personal Media Players

Apple Ipod

Creative ZEN Micro

Epson P-2000

ARM7

ARM7

ARM7

43

Prodotti ARM - Personal Digital Assistants

HP iPaq 4150/4350

Intel XScale

Acer N40

Panasonic CF-P1

ARM9 (S3C2410)

Xscale (PXA-263)

44

Prodotti ARM - Smart Phones

Nokia N70 3G

Motorola A780

ARM9

Xscale (PXA271)

Sony Ericsson P910

ARM7 / ARM9

45

Riferimenti

ARM Ltd - http://www.arm.com/

Wikipedia - http://en.wikipedia.org/wiki/ARM_architecture

The history of the ARM CPU - http://www.ot1.com/arm/armchap1.html

ARM Assembler - http://www.heyrick.co.uk/assembler/

Introduzione al processore ARM - http://www.dei.unipd.it/didattica/ae1/web/materiale.htm#u03

ARM, The first encounter - http://galeb.etf.bg.ac.yu/~vm/tutorial/ARM.ppt

Ars Technica: RISC vs CISC - http://arstechnica.com/cpu/4q99/risc-cisc/rvc-1.html

A Brief History of RISC - http://www.aallison.com/history.htm

46

I Processori ARM

Giovanni Barisione - Gabriele Santinelli

1

seminario di Implementazioni di Linguaggi - A.A. 2005/2006 @ DISI, Genova

•picole dimensioni

•bassi costi

•bassi consumi

•no dissipatori/ventole

1

ACORN Atom (1981) & BBC Micro (1982)

Primi home computer della Acorn, usciti nei primi anni ‘80.

Entrambi basati sul processore MOS Technology 6502 del 1975:

• 8bit

• economico: costava 1/6 rispetto ai concorrenti (Motorola, Intel)

• ottime prestazioni rispetto ai concorrenti

2

•Importanza Acorn in UK (Sinclair, spectrum)

•Acorn leader nel settore dell’Education

•BBC Micro: richiesto dalla BBC per la trasmissione televisiva The Micro

Program (Beeb, soprannome affettivo)

•BBC Micro: vendite sopra le aspettative (2 milioni/100k)

2

ARM1 (1985) (#1)

Nel 1983 il 6502 è piuttosto datato: i personal

computer concorrenti ormai sfoggiano CPU a 16bit.

Acorn testa tutte le CPU a 16 e 32bit presenti sul

mercato ma nessuna la soddisfa appieno. Decide

quindi di crearsi il proprio processore da zero,

basandosi sul set di istruzioni del ben noto 6502.

La ora decantata semplicità del nascente processore ARM1, era in

principio una neccessità. Si narra, infatti, che i progettisti incaricati

fossero alle prime armi nella progettazione di processori; fu questo che

impedì all’ARM1 di diventare troppo complesso, decretandone così la

sua fortuna.

Si decide di puntare su un processore con un set di istruzioni a

lunghezza fissa e un modello load/store.

3

•In quello stesso periodo Intel migliora le proprie CPU CISC, passando dall’8088

all’80186, 80286... fino ai processori odierni.

•Grazie ai guadagni derivanti dal BBC Micro, hanno un ottimo laboratorio di

ricerca

3

ARM1 (1985) (#2)

Il team di sviluppo è composto da 6 persone.

Il primo set di istruzioni viene scritto in BASIC, cosa che permette di

sviluppare un prototipo in tempi molto brevi.

In BASIC è anche il simulatore event-driven che permette il supporto

dei chip, e dei vari controller della macchina.

L’ARM1 viene commercializzato come coprocessore aggiuntivo per il

BBC Micro.

Nell’attesa di un computer basato su ARM, Acorn produce una

versione “home” del BBC Micro ma si rivela un flop. In seguito alla crisi

economica, Acorn viene acquistata da Olivetti.

4

•Lo stesso simulatore, convertito in Modula-2 (prima) e in C (dopo) è ancora

usato da Acorn e ARM Ltd per design e testing

•Per far sì che all’uscita di un PC basato sull’ARM1 i programmatori

sapessero usarlo

4

ARM2 (1987)

Ci vogliono altri due anni prima che

Archimedes, il primo computer basato

sul processore ARM (in realtà ARM2),

veda la luce.

Primo processore ARM immesso sul

mercato.

• 32bit data bus

• 26bit address space

• 16 registri a 32bit

• 30 000 transistors (contro i 68 000 del

Motorola 68000)

• no microcodice (RISC)

• no cache (cosa abbastanza comune

all’epoca)

5

•Primo PC con processore RISC

•Archimedes (ARM2): all’inizio non ha molto SW: prima emulatori BBCM/IBM;

in 1-2 anni viene sviluppato SW Educational

5

Da Acorn a ARM Ltd (fine ‘80)

Alla fine degli anni ‘80 inizia una

collaborazione con Apple per la nuova

versione dell’ARM.

Il lavoro Diventa così importante che nel

1990 viene creata una nuova società:

ARM Ltd (qui ARM assume il significato

di Advanced RISC Machines, sostituendo

il precedente di Acorn RISC Machines) che contiene il team del design.

L’ARM Ltd non produce microprocessori ma progetta e vende

proprietà intellettuale.

Cambia così la numerazione: vengono saltati gli ARM4 e 5 e si passa

direttamente all’ARM6 e alle sue varianti.

6

•(foto) quartier generale in Cherry Hinton, Cambridge

6

ARM3 (1990)

Successore dell’ARM2, prima CPU della ARM Ltd.

• 4Kb di cache.

ARM 610 (1991)

Nel 1991 Apple usa una versione dell’ARM6

la 610 per le prime serie di PDA come l’Apple

Newton, conosciuti anche come

MessagePad.

Nel 1994 verrà poi utilizzato anche dalla

Acorn per le cpu dei suoi RiscPC.

Questa versione introduceva un

indirizzamento a 32 bit con 4K di cache e con

la possibilità di passare dalla modalità bigendian alla little-endian; fu prodotto a diverse

velocità: 20Mhz, 30Mhz e 33Mhz.

7

Evoluzione (#1)

8

Evoluzione (#2)

9

RISC vs CISC (#1)

RISC (Reduced Instruction Set Computer)

• il concetto nasce nel 1974 da John Cocke (IBM)

• solo il 20% delle istruzioni macchina sono molto usate

• la complessità si sposta dall’HW al SW (compilatore)

• meno istruzioni significa meno transistor

• richiede più linee di codice di un CISC (più memoria)

CISC (Complex Instruction Set Computer)

• definizione retroattiva introdotta per distinguerli dai RISC

• microcodice, risiede in una ROM e traduce ogni singola istruzione

• istruzioni più vicine a quelle dei linguaggi di alto livello

MIPS (Microprocessor without Interlocked Pipeline Stages)

• minimizza le chiamate alla memoria esterna arricchendo la CPU di

registri

10

Quando i transistor disponibili su un solo chip erano pochi e i calcolatori

venivano spesso programmati in assembler, era naturale sfruttarli in modo

tale da avere CPU con istruzioni potenti, evolute e complesse: più queste

erano vicine alle istruzioni dei linguaggi di programmazione ad alto livello più il

computer sarebbe stato facile da programmare, e i programmi avrebbero

occupato poco spazio in memoria (anch'essa poca e preziosa). Le CPU

progettate secondo questo approccio sono dette CISC ed avevano unità di

controllo complesse capaci di sfruttare al meglio pochi registri e i cui

programmi erano di dimensioni relativamente piccole. A cavallo fra gli anni '70

e gli '80 però la situazione era in gran parte cambiata: la RAM era molto più

economica ed erano ormai disponibili ottimi compilatori in grado di generare

linguaggio macchina molto efficiente: per questo si iniziò a pensare ad un

nuovo modo di progettare le CPU, prendendo in esame la possibilità di usare i

transistor disponibili per avere invece molti registri e un set di istruzioni

elementare, molto ridotto, che delegasse al compilatore il lavoro di tradurre le

istruzioni complese in serie di istruzioni più semplici, permettendo così di

avere unità di controllo particolarmente semplici e veloci. Oramai però la

distinzione fra queste due architetture è venuta in gran parte meno: il numero

di transistor disponibili su un solo chip è aumentato tanto da poter gestire

molti registri ed anche set di istruzioni complesse.

Un compilatore che genera codice per CPU RISC deve affrontare un duro

lavoro per generare codice compatto ed efficiente, che in ogni caso sarà più

grande ed occuperà più memoria dell'equivalente per CISC.

10

RISC vs CISC (#2)

11

Post-RISC

Oggi la distinzione tra RISC e CISC è molto meno marcata. Le CPU

RISC sono diventate molto più complesse mentre i CISC sono

diventati più efficienti. Infatti:

• il PPC 601 (RISC) supporta più istruzioni di un Pentium (CISC)!

• la famiglia Pentium II è definita da Intel come CRISC

12

Il mercato dei processori RISC

Per motivi di retrocompatibilità, i

processori RISC non sono mai entrati

negli home-computer.

Sono invece stati introdotti fin da subito nel mondo dei

cellulari/palmari, perchè in forte espansione proprio in quel periodo.

Oggi la stessa Intel dichiara di produrre più CPU ARM che x86.

13

•Fino al 1998 MIPS era leader, grazie alla console Nintendo

•Dal 1999, grazie all’espansione del mercato dei cellulari, la ARM diventa

dominante

•Il RISC di ARM è particolare, non punta alle prestazioni, ma alla semplicità

13

Acorn VS Apple (1994)

As a founder member,

Acorn is delighted

to welcome Apple

to the RISC Club.

After 11 years of development and 7 years of production, we at Acorn are still

marveling at the sheer power, performance and potential of 32-bit RISC

technology.

Our ARM 32-bit RISC processors have delivered these capabilities to our

many customers in education, the home and industry worldwide, in our products

since 1987.

So it comes at little surprise to hear that Apple's new desktop range also

incorporates 32-bit RISC technology.

Oh well. Better late than never.

Dal Times, 15 marzo 1994

14

ARMv4 - Memoria

ARM è un processore a 32 bit ma è anche in grado di manipolare

dati a 8bit (byte) e a 16bit (halfword).

• Le word a 32 bit sono allineate in memoria ad indirizzi multipli di 4.

• Le halfword sono allineate ad indirizzi multipli di 2 mentre i byte sono

singolarmente indirizzabili in memoria.

15

ARMv4 - Modi Operativi

Esistono sette modi di funzionamento supportati dal processore

Il modo può essere cambiato via software, in modalità privilegiata oppure

attraverso un’eccezione.

16

ARMv4 - Registri (#1)

Il processore ARM è dotato di 37 registri:

• 31 registri generici

•R13 corrisponde allo Stack Pointer (SP)

•R14 corrisponde al Link Register (LR)

•R15 corrisponde al Program Counter (PC)

• 6 registri di stato (di cui 5 di salvataggio)

I registri sono divisi in banchi parzialmente sovrapposti, uno per

ogni modo operativo esistente (System e User usano lo stesso

banco).

Quindi ci sono 15 registri d’uso generale (da R0 a R14), uno o due

registri di stato (quello corrente ed eventualmente quello di

salvataggio) ed il PC. Tutti i registri tranne quelli di stato possono

essere utilizzati da tutte le istruzioni di tipo generale.

17

ARMv4 - Registri (#2)

18

ARMv4 - Registri (#3)

La presenza di una coppia specifica di registri SP e LR per ogni

modo operativo facilita l’associazione ai singoli modi di uno stack

privato e rende più efficiente il ritorno da eccezione.

Nel modo FIQ esiste una copia fisica anche dei registri da R8 a

R12: permette di servire una chiamata ad una interruzione veloce

senza dover salvare quei registri, ottenendo una migliore efficienza

nella realizzazione della corrispondente routine di servizio.

19

ARMv4 - CPSR (#1)

Il Current Program Status Register è il registro di stato. Include i

bit di condizione (i 4 bit più significativi), le maschere per le

interruzioni e la codifica del modo operativo.

•bit da 0 a 4 (M): modo operativo

•bit 5 (T): set di istruzioni Thumb a 16bit, on-off

•bit 6 (F): interruzioni “fast” (FIQ), on-off

•bit 7 (I): interruzioni generiche (IRQ), on-off

•bit 28 (V): indica errore di overflow

•bit 29 (C): indica il riporto

•bit 30 (Z): indica un risultato zero

•bit 31 (N): indica un risultato negativo

20

ARMv4 - CPSR (#2)

• C, Z e N possono essere modificati in base al risultato di una

istruzione di elaborazione dei dati. I bit di condizione vengono modificati

solo se il bit S (Set Condition Code) è impostato a 1. Questo si ottiene

postponendo la lettera S al nome dell’istruzione. (Es. ADD→ADDS,

SUB→SUBS)

• V (Overflow) è modificabile solo dalle operazioni aritmetiche.

• C, le istruzioni additive (ADDS, CMN...) lo impostano a 1 se nella

somma risulta un riporto dal bit più significativo. Le istruzioni sottrattive

(CMP, SUBS...) lo impostano a 0 se nella differenza risulta un “prestito”

nel bit più significativo.

Il registro SPSR (Saved Program Status Register) ha il compito di

preservare il valore di CPRS durante la gestione di un’eccezione. C’è

un SPSR per ogni modo operativo tranne che per il modo User/System

durante il quale non è prevista la gestione di un’eccezione.

21

21

ARMv4 - Stack (#1)

Nei processori ARM gli stack vengono gestiti tramite le istruzioni

LDM (Load Multiple Register) e STM (Store Multiple Register).

Sono supportati quattro formati diversi di stack, ognuno dei quali

viene specificato attraverso una sigla di due caratteri preposta al

nome dell’istruzione LDM o STM.

Questi sono i tipi di stack:

•Full Stack: SP punta all’ultimo dato inserito

•Empty Stack: SP punta alla prima posizione di memoria libera

•Ascendente: SP viene incrementato per effetto dell’inserimento

•Discendente SP viene decrementato per effetto dell’inserimento

22

Utile in particolare per il registro LR (R14) che deve essere salvato prima che

dall’interno di una subroutine se ne chiami un’altra, al fine di ottenere il

corretto ripristino della successione di indirizzi di ritorno alle subroutine

chiamanti. Il registro SP (R13) viene utilizzato per identificare l’indirizzo della

testa di uno stack.

22

ARMv4 - Stack (#2)

23

ARMv4 - Eccezioni (#1)

Sono previsti 8 tipi d’eccezione, ad ognuno è associato un hard

vector. L’elaborazione di un’eccezione forza il PC ad assumere il

valore del corrispondente vettore.

Di norma a quell’indirizzo è collocata un’istruzione di salto alla

corrispondente routine di servizio, tranne per l’ultima eccezione,

dove può tranquillamente iniziare la routine.

24

La Address Exception si riferisce ad una particolare modalità operativa con

address space ridotto a 26bit.

24

ARMv4 - Eccezioni (#2)

25

ARMv4 - Gestione delle priorità dei dispositivi

Essendo le linee di ingresso IRG e FIQ uniche, i dispositivi di

ciascuna delle due classi di interruzioni devono essere identificati in

una fase iniziale delle rispettive routine di servizio.

Al fine di velocizzare tale fase di identificazione e gestire

correttamente le priorità dei dispositivi, il sistema può includere

hardware aggiuntivo (interrupt controller).

ARMv4 - Priorità delle eccezioni

Nel caso che più eccezioni siano

contemporaneamente pendenti, il

processore ARM utilizza la seguente

tabella delle priorità.

26

ARMv4 - Istruzioni Condizionali

Perchè ogni singola istruzione venga effettivamente eseguita devono

essere preliminarmente soddisfatte alcune condizioni, valutando i bit

di condizione. Il nome di ogni istruzione può essere esteso:

27

ARMv4 – Pipeline (#1)

A partire dall’ARM2 il processore è dotato di una pipeline a 3 stadi.

• Fetch: copia il codice dell’istruzione dalla memoria

• Decode: decodifica l’istruzione leggendone gli operandi

• Execute: l’ALU esegue l’istruzione ed effettua il write-back

Si ottiene quindi una latenza di tre cicli, mentre il throughput è di una

istruzione per ciclo.

28

ARMv4 – Pipeline (#2)

Il PC è sempre due istruzioni avanti rispetto all’istruzione in

esecuzione.

Nel caso di branch due cicli di istruzioni vanno persi (perchè la

pipeline deve nuovamente riempirsi), per questo è preferibile l’uso di

istruzioni condizionali.

con “branch”

con istruzione condizionale

CMP

BEQ

MOV

MOV

CMP R0,#0

MOVNE R1,#1

MOVNE R2,#2

R0,#0

<offset>

R1,#1

R2,#2

29

•istruzioni condizionali da usare se la condizione riguarda tre o meno istruzioni

CMP: compare, allows you to compare the contents of a register with another

register or an immediate value, updating the status flags to allow conditional

execution to take place. condizio

BEQ: branch, solo se sono uguali (differenza=0, Z=1)

MOV: move, sposta il valore # dentro al registro R

29

ARMv4 – Istruzioni (#1)

Possiamo dividere le istruzioni in categorie funzionali:

3) Istruzioni per l’elaborazione dei dati

Le regole base per questo tipo di istruzioni sono:

3 operandi: 2 sorgenti, 1 destinatario

tutti gli operandi sono a 32bit, sia i registri che le costanti

il risultato è a 32bit ed è posto in un registro

In questa classe troviamo le operazioni aritmetiche e logiche (ADC,

ADD, AND, BIC, EOR,MUL,ORR, RSB, RSC, SBC, SUB), quelle per

il movimento tra i registri (MOV, MVN) e quelle di confronto (CMN,

CMP, TEQ, TST)

30

ARMv4 – Istruzioni (#3)

2) Istruzioni per l’accesso alla memoria

In questa classe vi sono le istruzioni per il movimento dei dati da

memoria a registro (load) e viceversa (store). Vi sono poi alcune

varianti per il caricamento di dati da 8 e 16bit con e senza segno e

per il movimento multiplo che coinvolge più registri.

Le istruzioni sono: LDR, LDRB, STR, STRB, LDRH, LDRSB,

LDRSH, STRH, LDMxx, STMxx

31

ARMv4 - Istruzioni (#2)

Aritmetiche e logiche:

ADD

SUB

RSB

MUL

ORR

BIC

r0,

r0,

r0,

r0,

r0.

r0,

r1,

r1,

r1,

r1,

r1.

r1,

r2

r2

r2

r2

r2

r2

//

//

//

//

//

//

r0=r1+r2

r0=r1-r2

r0=r2-r1

r0=r1*r2

r0=r1 or r2

r0=r1 and not

ADC

SBC

RSC

AND

EOR

r2

r0,

r0,

r0,

r0,

r0,

r1,

r1,

r1,

r1,

r1,

r2

r2

r2

r2

r2

//

//

//

//

//

r0=r1+r2+C

r0=r1-r2+C-1

r0=r2-r1+C-1

r0=r1 and r2

r0=r1 xor r2

Movimento tra i registri

MOV r0, r2

// r0=r2

MVN r0, r2

// r0= not r2

Operazioni di confronto

CMP r1, r2

TST r1, r2

//set cc on r1-r2

CMN r1, r2 //set cc on r1+r2

//set cc on r1 and r2 TEQ r1, r2 //set cc on r1 xor r2

Con queste ultime vengono modificati solo i bit di condizione(cc) del

CPSR

32

ARMv4 – Istruzioni (#4)

3) Istruzioni di salto

Queste istruzioni hanno l’effetto di caricare un nuovo valore nel

registro PC(R15), valore che viene calcolato come somma del PC

corrente e dell’offset relativo specificato nella codifica dell’istruzione.

Di questa classe fanno parte 2 tipologie di istruzioni B(branch) e

BL(branch and link)

B <indirizzo>

BL <indirizzo>

//PC<-indirizzo

//LR<-PC-4 (salva PC in LR)

PC<-indirizzo

B Lab1 //salta al label “lab1”

BEQ Lab2

//se z=1 allora salta al label “lab2”, altrimenti prosegue

BLVC SUBR1

//se V=0 chiama la subroutine “SUBR1”

33

Tecnologie Proprietarie

A cominciare con ARMv4 sono stati

introdotti:

• Thumb

• Thumb-2

Mentre a partire da ARMv5 sono

state aggiunte le estensioni:

• Jazelle

• TrustZone

• IEM (Intelligent Energy Manager)

• SIMD

• NEON

34

•Jazelle: accelera l’esecuzione del Java bytecode, aumentando notevolmente

le performance rispetto a un SW basato sulla JVM. Fino a 8 volte più veloce,

80% di consumi in meno.

•TrustZone: estensione che fornisce il supporto hardware per due spazi di

indirizzamento separati. Il codice in esecuzione nello spazio “non sicuro” non

può avere accesso agli spazi di indirizzamento marcati come “sicuri”.

•IEM: implementa dei particolari algoritmi in grado di bilanciare il lavoro del

processore e il consumo di energia. In coordinamento col SO e le applicazioni

si preoccupa di aggiustare dinamicamente il livello di performance della CPU.

•SIMD: istruzioni aggiuntive che supportano il Single Instruction Multiple Data

(SIMD). Utile per codec audio e video.

•NEON: architettura sviluppata per venire incontro alla richiesta di alte

performance per applicazioni multimediali.

34

Thumb Technology (#1)

Thumb è un estensione all’architettura

ARM a 32bit che permette una densità di

codice molto elevata.

Il set di istruzioni Thumb (ISA) contiene un

sottoinsieme delle istruzioni ARM a 32bit

più comunemente usate ma, a differenza di

queste, si tratta di istruzioni compresse a 16bit.

In esecuzione le istruzioni Thumb a 16bit vengono decodificate,

svolgendo così lo stesso lavoro dei loro equivalenti ARM a 32bit.

Vantaggi:

• L’aumento di densità del codice è stimato intorno al 30% e non comporta

peggioramento delle prestazioni.

• Usando una combinazione di codice ARM e Thumb, il programmatore è

in grado di bilanciare costi, performance e consumi.

35

•The difference between two equivalent instructions lies in how the

instructions are fetched and interpreted prior to execution, not in how they

function. Since the expansion from 16-bit to 32-bit instruction is accomplished

via dedicated hardware within the chip, it doesn't slow execution even a bit.

But the narrower 16-bit instructions do offer memory advantages.

35

Thumb Technology (#2)

Svantaggi:

• Il programmatore deve essere in grado di identificare le routines veloci

(che sfrutteranno le istruzioni ARM a 32bit) da quelle ottimizzabili mediante

le istruzioni Thumb.

• Molte istruzioni ARM non hanno equivalenti in Thumb (per esempio

quelle per l’accesso a funzioni speciali come SIMD/DSP, o le istruzioni

privilegiate). In questi casi il codice Thumb deve chiamare una funzione

contenente il codice ARM da eseguire, prima di poter tornare al codice

Thumb.

• 16bit non sono abbastanza per mantenere la capacità di eseguire in

modo condizionale ogni istruzione.

36

Thumb-2 Technology

Aggiunge diversi miglioramenti alla tecnologia Thumb:

• nuove istruzioni a 16bit per migliorare il flusso del programma

• nuove istruzioni a 32bit per sopperire alle istruzioni ARM ancora mancanti

• nuove istruzioni a 32bit che migliorano il set di istruzioni di ARM

Nella maggior parte delle applicazioni le istruzioni Thumb-2

diventano lo standard, specialmente nelle situazioni in cui il rapporto

costi, performance e consumi è poco chiaro.

• Non c’è più bisogno di mescolare istruzioni ARM e Thumb.

• Ritorno all’esecuzione condizionale delle istruzioni (IT).

37

StrongARM (1995)

Era una delle più veloci versioni

dell’architettura ARM. Creato dalla

Digital è stato disegnato soprattutto per

l’uso negli strumenti portabili nei quali

occorreva un basso consumo

energetico, era usato in palmari e anche

in decoder e box digitali per la

televisione.

Lo StrongArm portò i RiscPC da 40 a 200-300Mhz e fu il primo a

dividere tra instruction e data cache con entrambe le cache di 16Kb.

La pipeline viene portata da 3 a 5 stadi.

Nel 1995 l’SA-100 viene immediatamente incorporato nei nuovi modelli

dell’Apple Newton.

38

Da StrongARM a XScale (2000)

Successivamente la Digital Semiconductor, viene ceduta alla Intel

che usa lo StrongARM per sostituire i suoi i960 che avevano

dominato il mercato dei processori RISC fino ai tardi anni ‘90.

Con XScale nasce la generazione v5 di ARM che sostituisce gli

StrongARM ancora basati sulla v4. Tutti i processori di questo tipo

sono basati su un processore a 32 bit con Thumb e hanno 2 cache

da 32kb di tipo instruction e data e anche 2 mini-cache da 2kb.

E’ usato come processore in tantissimi tipi di palmari e anche sui pc

desktop RISC Iyonix della Acorn e su molti media-player portabili e

grazie alla collaborazione con Apple anche sui prossimi Ipod.

39

XScale (2000)

La pipeline si suddivide in 3 sotto pipeline: Main Execution, Memory e

MAC con in tutto 7/8 stadi, con di norma 1 ciclo per stadio.

40

XScale

I tre pipeline possono essere occupati

simultaneamente (comportamento di tipo

superscalare).

I tre pipeline funzionano in maniera asincrona.

Conclusione: le istruzioni possono completare

l’esecuzione fuori ordine se non ci sono

dipendenze tra i dati.

Per ottimizzare l’uso delle pipeline: la predizione dei salti.

PXA255 effettua una predizione dinamica basata sulla “storia

passata” di ciascun salto, la storia è memorizzata nel BTB (Branch

Target Buffer), la storia di un salto può assumere 4 possibili stati:

Strongly Not Taken, Weakly Not Taken, Weakly Taken e Strongly

Taken.

41

Prodotti ARM - Gaming

Nintendo DS

Sony PSP

ARM7 / ARM9

ARM9

Nintendo GB Advance

ARM7 / ARM9

42

Prodotti ARM - Personal Media Players

Apple Ipod

Creative ZEN Micro

Epson P-2000

ARM7

ARM7

ARM7

43

Prodotti ARM - Personal Digital Assistants

HP iPaq 4150/4350

Intel XScale

Acer N40

Panasonic CF-P1

ARM9 (S3C2410)

Xscale (PXA-263)

44

Prodotti ARM - Smart Phones

Nokia N70 3G

Motorola A780

Sony Ericsson P910

ARM9

Xscale (PXA271)

ARM7 / ARM9

45

Riferimenti

ARM Ltd - http://www.arm.com/

Wikipedia - http://en.wikipedia.org/wiki/ARM_architecture

The history of the ARM CPU - http://www.ot1.com/arm/armchap1.html

ARM Assembler - http://www.heyrick.co.uk/assembler/

Introduzione al processore ARM - http://www.dei.unipd.it/didattica/ae1/web/materiale.htm#u03

ARM, The first encounter - http://galeb.etf.bg.ac.yu/~vm/tutorial/ARM.ppt

Ars Technica: RISC vs CISC - http://arstechnica.com/cpu/4q99/risc-cisc/rvc-1.html

A Brief History of RISC - http://www.aallison.com/history.htm

46