Sistemi - Classe Terza

robertomana.it

Il Personal Computer

Il Personal Computer

Rev. Digitale 1.0 del 01/09/2016

Introduzione ……………………………………………………..………... 2

Breve storia dei Sistemi di Elaborazione ……………….………………….

2

Breve storia dei principali Sistemi Operativi …………..………………….

4

Compilazione e lancio di un programma …………………………………... 6

Architettura del Sistema Calcolatore ………………………….……………. 6

Sequenza di Avvio del Personal Computer ………………………………... 10

Il microprocessore 8086 …..…………………………….………………...

Registri …………………………………….………………………………

Ciclo da caricamento ed esecuzione delle istruzioni ………………………

La segmentazione della memoria ….………………………………………

Piedinatura del processore 8086 ……….…………………………….……...

Il Ciclo macchina …………………………………………………………...

Processori della famiglia Intel ……………………………………………...

Evoluzione dei processori Intel ……………………………………………...

11

11

12

13

15

18

19

20

Componenti di un Personal Computer …….………….………………...

Main Board ………………..…….………………….…….…………..…….

Memoria Centrale ………………….……………….…….…………..…….

Memorie Persistenti …………………….…………………………………..

I Bus Interni: ISA, PCI, PCI Express …………..………..…………………..

I Bus Esterni: IDE/ATA, SCSI, Serial ATA, USB ………………………….

Memorie di Massa ….…………………..………………………………...…

PenDrive ……………………………….………………………..…………..

CD …………………………………….………………………..…………..

DVD …….…………………………..……….……………………………..

SD …………………………………….………………………..…………..

Schede e Porte di Comunicazione ………………..…………………….…..

Periferiche Esterne: Tastiera, Mouse, Scanner, Monitor e Stampanti .……

28

28

30

33

34

36

40

43

43

46

47

49

52

Gestione delle Periferiche di un Personal Computer …….…….………...

Interfacciamento Hardware delle periferiche ……………..………………..

Tecniche di Comunicazione tra CPU e Periferica ………..………………..

Classificazione delle interruzioni ………..………………………………...

55

55

57

58

pag 1

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

Breve Storia dei Sistemi di elaborazione

1640

Blaise Pascal, scienziato e filosofo francese, inventa e produce una macchina di calcolo, interamente

meccanica, detta pascalina, in grado di eseguire addizioni, sottrazioni, parziali moltiplicazioni e divisioni. E‟

basata su una sequenza di ruote dentate che effettuano il riporto delle addizioni ed il prestito delle sottrazioni.

1930 - 1940

Nascono i primi calcolatori elettromeccanici, in grado di eseguire calcoli logaritmici, esponenziali,

trigonometrici, leggendo i dati di input da apposite “schede perforate”. La scelta dell‟operazione avviene

mediante interruttori azionati manualmente. Durante la seconda guerra mondiale viene prodotta la cosiddetta

macchina di Touring mirata a decodificare i messaggi cifrati tedeschi prodotto tramite la macchina

ENIGMA. Primo esempio di sistema di elaborazione dati, però non programmabile.

1937

Nell‟ambito della ricerca per le trasmissioni radio, nascono le valvole termoioniche (triodi), che consentono

di eliminare definitivamente tutte le parti meccaniche, con notevolissimo aumento delle velocità

1943

Su progetto dello scienziato ungherese John Von Neumann, viene realizzato a Philadelphia il primo

esempio di sistema di elaborazione programmabile. Scopo principale del progetto era la realizzazione di

calcoli per armamenti sempre più sofisticati (studio di traiettorie, bomba all‟idrogeno).

Macchina interamente realizzata mediante valvole termoioniche (triodi). Due innovazioni fondamentali:

Primo esempio di macchina programmabile, in grado cioè di eseguire programmi differenti scritti

dall‟utente e codificato su apposite schede perforate. Il programmatore scrive il programma direttamente

in codice binario creando una apposita scheda perforata costituita da una sequenza di istruzioni da 8 bit

ciascuna. Un apposito pulsante consente di leggere la scheda perforata e caricare il programma

all‟interno di una memoria centrale . La cpu provvede ad eseguire il programma “leggendo” una

istruzione alla volta e provvedendo alla sua esecuzione

Per la prima volta si utilizza nella pratica la logica binaria.

- Memoria Centrale e CPU sono interamente realizzate mediante valvole termoioniche.

- Periferiche di input, di output e di memoria di massa sono tutte realizzate tramite schede perforate.

Le istruzioni hanno la possibilità di operare su dati memorizzati su schede perforate differenti rispetto alla

scheda in cui si trova il programma, per cui lo stesso programma può essere eseguito più volte su dati

differenti. Nasce il concetto di macchina programmabile, con piena indipendenza tra programma e dati.

Nasce anche il concetto di diagramma di flusso per la stesura di un programma.

Sulla base della macchina di Von Neumann, nel 1953 l‟IBM realizza il primo elaboratore commerciale.

Nascono così i primi computer della prima generazione, completamente realizzati tramite valvole

termoioniche.

L‟architettura della macchina di Von Neumann, seppur infinitamente potenziata dal punto di vista

tecnologico, è rimasta sostanzialmente la stessa fino ai calcolatori moderni.

1947

Bardeen, Brattain, Shockey, (premi nobel) realizzano il primo transistor allo stato solido, che ha stessa

funzione della valvola termoionica ma occupa uno spazio infinitamente inferiore ed è molto più veloce.

Anni 60 Computer della seconda generazione realizzati a transistor (IBM 1401). Dimensioni molti inferiori

rispetto alla macchina di Von Neumann, ma molto maggiori rispetto alle macchine attuali.

Nascono i primi supporti magnetici (floppy) di memorizzazione con apposite testine di lettura.

Nascono i primi linguaggi Assembly che consentono la realizzazione dei primi Sistemi Operativi.

Oltre all‟assembly nascono anche i primi linguaggi di programmazione avanzati (linguaggi di seconda

generazione) quali Fortran = FORmula TRANstation (1957) per applicazioni scientifiche ed il Cobol =

Common Business Oriented Language (1960) per applicazioni gestionali.

1965

Nascono i circuiti integrati, che raggruppano al loro interno migliaia di transitor.

pag 2

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

Anni 70 Computer della terza generazione, sempre meno ingombranti, realizzati mediante circuiti integrati

(micro-chip. Chip = scheggia). Nascono anche i primi Hard Disk. Gli elaboratori sono tipicamente

mainframe ad alta velocità ed elevate capacità di memoria, in grado di fornire servizi interattivi a centinaia di

terminali privi di capacità di elaborazione autonoma. Elaboratori tipici IBM 360 e VAX della Digital. Il loro

costo arriva a centinaia di migliaia di dollari. Utilizzati nei sistemi di archiviazione statali e delle banche.

1968 nasce presso l'Università di Dartmouthil linguaggio BASIC (Beginners‟ All purpose Symbolic Instruction

Code) più semplice e flessibile di Fortran e Cobol. Da questo Basic deriverà il Microsoft Basic (1975)

1969 Ken Thompson e Dennis Ritchie scrivono la pria versione di Unix (che significa semplicemente

unico, ad evidenziare la semplicità del sistema), interamente scritto in Assembler.

1971 DEC (Digital Equipment Corporation), fondata nel 1957 da Kenneth Olsen, realizza il PDP-11,

primo vero esempio di mini-calcolatore basato su circuiti integrati con dimensioni e costi decisamente

inferiori al mainframe. Il computer diventa accessibile anche ad organizzazioni più piccole.

1974 Ken Thompson e Dennis Ritchie creano un nuovo linguaggio detto C Language con lo scopo di

utilizzarlo per una nuova versione del SO Unix. Unix viene installato prima su PDP7 poi su PDP 11.

1977 Steve Jobs (oggi Apple) e Stephan Wozniak realizzano il primo prototipo di Personal Computer,

denominato APPLE 1, basato su tecnologia VLSI (Very Large Scale Integration) e su processore Intel 8080.

Ad APPLE1 fa seguito APPLE 2, dotato di tastiera, video, memoria di massa (costituita da un floppy disk da

5 ¼ pollici) direttamente programmabile in linguaggio Basic. Nasce l‟era dei Personal Computer.

1979 Intel produce i microprocessori 8086 e 8088. 8086 è un processore con struttura a 16 bit (bus e registri interni),

in grado di indirizzare 220 postazioni di memoria. 8088 è una versione a 8 bit con la stessa architettura e lo

stesso set di istruzioni, ma con bus dati a 8 bit.

1981 Il 12 agosto 1981 IBM realizza il primo Personal Computer Desktop (così piccolo da poter stare su una

scrivania), basato su microprocessore Intel 8088 poi 8086,. Computer della Quarta Generazione. Le

specifiche del Personal Computer IBM vengono rese pubbliche. Sistema aperto su cui possono essere

aggiunte svariate schede elettroniche accessorie realizzate da produttori differenti. SO : CP/M (Digital)

Negli stessi anni una piccola software house che nel 1979 contava 3 dipendenti e 16.000 $ di fatturato, fondata da

Bill Gates e Paul Allen e denominata Micrsoft inc. intuisce la bontà del progetto IBM. Grazie al senso degli

affari di Bill Gates e alle abilità tecniche di Paul Allen, Microsoft acquista le licenze di un piccolo SO

denominato QDOS molto più semplice di Unix (e quindi più veloce), lo modifica facendolo diventare MSDOS (MicroSoft - Disk Operating System) e stipula con IBM un contratto secondo il quale IBM dovrà

riconoscere a Microsoft una licenza sulla vendita di ogni PC contenente MS-DOS. Il contratto viene poi esteso

a tutti gli altri venditori di PC.

Il PC IBM utilizza un Hard Disk da 20 MBytes ed un lettore di Floppy Disk da 5° ¼. Nascono molti nuovi

costruttori di parti di PC o di PC completi, con la caduta dei prezzi ed una enorme diffusione del PC IBM

compatibile che diventa strumento di massa, tale da produrre una vera rivoluzione culturale in tutte le

società avanzate. Oggi molte aziende producono PC, ed il temine IBM compatibile è obsoleto.

1983

Nasce TCP / IP destinato a diventare il protocollo base della rete Internet

1984

Apple presenta Macintosh, il primo Personal Computer con interfaccia interamente grafica.

1985

Richard Stallman presenta il progetto GNU con l‟obiettivo di sviluppare un SO Unix-like per PC

completamente libero (open-source) in grado di ospitare applicazioni a loro volta open source.

1991

Linus Torvalds aderisce al progetto GNU e scrive il primo kernel di Linux, versione ridotta di Unix per

Personal Computer con processore 80386 o superiori. Problemi legali con Novell divenuta proprietaria del

marchio Unix.

1991

Nasce HTTP, protocollo per l‟accesso alle pagine web. Data di nascita di Internet.

pag 3

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

Evoluzione dei processori Intel (Anno / Processore)

1981

1983

1986

1990

1994

1997

1999

8086

80286

80386

80486

Pentium

Pentium 2

Pentium 3

2001

2003

2005

2006

2007

2009

Pentium 4

Pentium M (Piattaforma Centrino per Notebook)

Pentium D (PC Desktop)

Core Duo (Notebook e Desktop)

Core 2 Duo (Notebook e Desktop)

i3 i5 i7

Breve storia dei principali Sistemi Operativi

Il SO è il software che controlla l’hardware della macchina e gestisce l’utilizzo del software applicativo.

Senza il SO la macchina sarebbe un insieme di rame e silicio inutilizzabili. La prima cosa da installare sul Disco

Fisso di una macchina è il SO. I principali SO, riportati in ordine cronologico di comparsa, sono i seguenti:

Unix

MS DOS

MacOs

Windows

Linux

Sistema operativo dei computer Macintosh, di tipo Unix Like, cioè derivato da Unix

Unix

Nasce agli inizi degli anni 70 nei laboratori AT&T (telecomunicazioni USA) la quale ne consentì la diffusione

gratuita (anche dei sorgenti) fino al 1984 quando, con la scissione di AT&T in sette diverse società, Unix System III

(in realtà alla release 7) divenne a pagamento. Alcune università continuarono a sviluppare loro versioni di Unix.

Fu appunto da questa derivazione che Bill Joy creò SunOS (ora Solaris e OpenSolaris) e fondò Sun Microsystems.

Primo SO modulare, multiutente e multitasking. Oggi utilizzato soprattutto nelle workstation ad elevate prestazioni

msDOS e Windows

MS-DOS è un sistema operativo a linea di comando, nel senso che i comandi devono essere digitati dall‟utente in

corrispondenza di un apposito PROMPT. DOS 1.0 gestisce soltanto Floppy Disk da 5 1/4 , mentre DOS 2.0 (1983

computer IBM XT basato su 8086) per la prima volta gestisce anche un disco fisso.

A metà degli anni 80 un nuovo sistema operativo, MacOs, installato sui computer Macintosh della APPLE,

comincia ad assumere una certa diffusione tanto da diventare reale antagonista di MS-DOS. I sistemi Macintosh

presentano per la prima volta una interessante interfaccia grafica, in cui l‟utente interagisce direttamente con il

mouse senza dover digitare manualmente ogni comando.

Microsoft intuisce la bontà del nuovo sistema e crea una applicazione simile denominata Windows che arriva fino

alla versione 3.11. Queste prime versioni sono a 16 bit,installate su sistema operativo MS-DOS 6.22 (ultima versione

di MS-DOS), utilizzano un formato eseguibile proprio diverso da quello di ms-dos, driver specifici per la gestione

delle periferiche e supportano l‟esecuzione multitask (preemptive solo da Windows 3 su Processore Intel 80386).

Nel 1995 Microsoft decide di mettere insieme ms-dos e windows creando un nuovo sistema operativo visuale a 32

bit denominato Windows 95 (Windows 2) con file system di tipo FAT32 e gestione dei long file names.

La compatibilità con i vecchi programmi DOS risulta abbastanza debole. Con WIN95 2nd edition viene aggiunto un

applicativo denominato PROMPT di MSDOS che consente di lanciare in esecuzione i vecchi eseguibili DOS come

se si stesse utilizzando un computer DOS e al contempo inviare i comandi DOS al Sistema Operativo.

Windows 98 (Windows 3) è molto più stabile di Windows 95, introduce il supporto AGP e USB ed il protocollo ICS

per la condivisione di Internet

Windows ME (Millenium) (Windows 4 – anno 2000) è di nuovo poco affidabile. Viene subito tolto dal mercato.

A fine 2001 nasce Windows XP (Windows 5) con cui viene introdotto NTFS e si ritorna alla stabilità di Wndows 98

pag 4

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

Nella primavera del 2007 viene presentato Windows Vista (Windows 6), dotato di una nuova interfaccia grafica

user friendly e mirato ad ottimizzare l‟utilizzo dei nuovi processori Intel DUAL CORE. Versione 64 bit (calcoli a 64)

Nell‟autunno 2009 esce Windows 7, che snellisce l‟interfaccia grafica potenziando la shell.

Nell‟autunno 2012 arriva Windows 8,.

Linux ed il progetto GNU - Gnu is Not Unix

Nel 1985 Richard Stallman presenta il progetto GNU con l‟obiettivo di sviluppare un ambiente Unix-like per PC

open source e completamente libero su cui poter eseguire applicazioni anch‟esse open-source.

Per libero si intende (manifesto GNU) la libertà di :

eseguire il programma per qualsiasi scopo

accedere ai sorgenti e poterli studiare

modificare i sorgenti per migliorne le caratteristiche

Concetto di free software

ridistribuire le copie modificate

GNU GPL (General Public License) documento che specifica le condizioni a cui può essere ridistribuito il software

I redistributori non possono porre alcuna restrizione nel momento in cui modificano e/o ridistribuiscono il

software. Ogni copia deve essere sempre free software. Il distributore può però farsi pagare l‟installazione e/o la

configurazione delle macchine, la documentazione, il supporto tecnico (call senter), eventuali pacchetti aggiuntivi.

Il nome LINUX deriva dal finlandese Linus Torvalds, colui che, nel 1991, ha maggiormente contribuito alla

scrittura del kernel. La x è un richiamo al genitore Unix. Torvalds si pose come obiettivo la realizzazione di un

sistema operativo simile a Unix che funzionasse su computer Intel 80386, ed iniziò a sviluppare un kernel chiamato

Linux, inizialmente ispirato a Minix di Andrew Tanenbaum, primo tentativo di realizzazione,verso la metà degli anni

80, di un sistema operativo Unix like in grado di funzione sui nascenti Personal Computer IBM 8086.

Il kernel Linux fu poi unito al Sistema GNU creando GNU/Linux. Il logo ufficiale è costituito dal pinguino TUX

(Torvalds UniX). Sistema aperto, in cui ognuno può aggiungere un suo contributo. Linux è oggi supportato anche da

grandi industrie come IBM e Hewlett-Packard che lo hanno reso un degno antagonista di Windows.

Si contano ad oggi più di 40 distribuzioni differenti, fra cui Red Hat (di Alan Cox) e UBUNTU (del giovane

sudafricano Mark Shuttleworth) sono fra le più conosciute. UBUNTU è un'espressione in lingua bantù che indica

"benevolenza verso il prossimo". La distribuzione di Ubuntu è arrivata oggi (settembre 2012) alla release 12.04

Esistono anche Live CD che consentono di avviare il SO direttamente da CD senza doverlo installare sul disco fisso.

Copyright e Licenze d’uso

Anche il software, come i film e i CD musicali, sono considerati Opere dell‟Ingegno e dunque legalmente protetti dal

Diritto d‟Autore (copyright). Il software coperto da diritto d‟autore contiene il simbolo ©, il nome del proprietario

dei diritti e l‟anno di pubblicazione. Questo significa che chi acquista un software (o un CD musicale o video) stipula

formalmente un contratto di Licenza d’uso singola o multipla che consente l‟installazione del sw su un singolo PC

ed una eventuale copia di sicurezza. Ulteriori installazioni o diffusioni sono perseguibili penalmente con pene che

vanno fino a 3 anni di carcere !! (Legge 248 del 2000). L‟installazione del sw richiede in genere una esplicita

accettazione delle condizioni relative alla Licenza d‟uso. Le stesse pene valgono per chi condivide file musicali su

Internet ma anche per chi li scarica (reato di ricettazione).

Licenze particolari

prodotti freeware : software compilati distribuiti con licenza d‟uso gratuito ma senza codice sorgente. Ad

esempio : browser, acrobat reader, etc. (ware significa merce)

prodotti shareware : software dotati di licenza d‟uso gratuita per un certo periodo di prova (es 2 mesi) dopo di

che, se si continua nell‟utilizzo, occorre procedere al pagamento. Si tratta in genere di versioni simili agli originali

ma non identici e che in genere continuano a funzionare anche dopo il periodo di prova, però il loro uso è

comunque NON LECITO. (Paint Shop, Winzip, Nero)

prodotti evaluation software identici agli originali, sempre con durata temporale limitata (cuteFTP, McAfee).

In ambiente Linux con il termine restricter si intende un driver free ma non open source (cioè freeware)

Con il termine Patch (pezza) si indica un aggiornamento gratuito di un Sistema Operativo o di un certo applicativo.

pag 5

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

Compilazione e lancio di un programma

Mentre ai tempi di Von Neumann i programmi venivano scritti direttamente in binario e memorizzati su schede

perforate, oggi, grazie ai linguaggi di programmazione evoluti, i programmi vengono scritti in forma testuale e salvati

su Hard Disk all‟interno di appositi file di testo leggibili con semplici editor di testo come Blocco Note.

Compilatore

Il compilatore è un particolare programma che traduce il file testuale in linguaggio macchina, producendo un file

binario con estensione .OBJ che contiene il codice binario corrispondente al programma originale

Assembler e Assemblatore

L‟assembler è un particolare linguaggio di programmazione le cui istruzioni testuali sono in corrispondenza 1 : 1 con

le istruzioni binarie riconosciute dalla CPU. Ad ogni istruzione Assembler corrisponde una unica istruzione binaria.

E‟ una semplice facilitazione per non scrivere direttamente in binario. L’assemblatore è il programma che converte

un file assembly in file binario. E‟ molto più semplice del compilatore, perché deve semplicemente eseguire una

traduzione univoca. Oltre al file OBJ l‟assemblatore produce in genere anche un interessante file LST contenente

l‟informazione binaria espressa in formato esadecimale con a fianco l‟istruzione testuale assembly.

Linker

Molto spesso una applicazione è costituita da più file sorgenti, ognuno dei quali contiene specifiche procedure, scritte

spesso da persone diverse all‟interno di un team di lavoro. Uno di questi file può far riferimento a funzioni o simboli

definiti all‟interno di un altro file. Il compilatore, che traduce ogni singolo file in binario, deve prevedere un

meccanismo che consenta di gestire queste situazioni senza generare errori.

A tal fine i linguaggi di programmazione prevedono l‟utilizzo di pseudoistruzioni che avvisano il compilatore su

simboli e procedure che si trovano in altri file. In corrispondenza di queste pseudoistruzioni, il compilatore crea delle

„note‟ all‟interno del file binario, che dunque non è più un file eseguibile vero e proprio, ma un file detto file oggetto,

sempre binario, ma contenente delle note che verranno interpretato da un programma detto linker, che provvede ad

integrare i vari file oggetto in un unico eseguibile risolvendo tutte le situazioni lasciate in sospeso dal compilatore.

Loader o Launcher

In realtà il codice macchina generato dal linker è un codice rilocabile, cioè che potrà essere caricato in memoria

centrale a partire da un qualunque indirizzo. Ciò è possibile mediante l‟utilizzo dei Segment Register il cui contenuto

viene assegnato dal loader durante il caricamento in memoria dell‟applicazione. Il loader è un componente del

sistema operativo che viene automaticamente richiamato nel momento in cui l‟utente digita sulla riga di comando il

nome di un file eseguibile (o fa doppio click sulla sua icona). Il loader provvede a trasferire il codice dell‟eseguibile

all‟interno della memoria centrale, provvedendo ad assegnare un valore ai vari segmenti definiti dal linker.

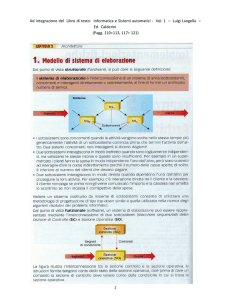

Architettura e ciclo di funzionamento della macchina di Von Neumann

La macchina di Von Neumann, come del resto le macchine attuali, è strutturata mediante una Architettura a Bus,

cioè un insieme di piste che collegano tra di loro tutti i principali dispositivi della macchina, vale a dire:

La Memoria Centrale MC, costituita da una sequenza di bytes, cioè un insieme di otto celle in grado di

memorizzare un bit ciascuna. All‟interno della memoria centrale viene caricato il programma da eseguire più

i dati che il programma stesso deve utilizzare.

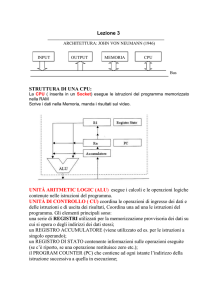

La Unità di Elaborazione detta CPU = Central Processing Unit, che si occupa di scandire una alla volta le

istruzioni presenti all‟interno della memoria centrale, caricarle nei propri registri ed eseguirle.

Dispositivi di input (schede perforate, oggi tastiera)

Dispositivi di output (schede perforate, oggi video)

Dispositivi di memoria di massa (schede perforate, poi Floppy Disk, oggi Hard Disk)

Le periferiche sono controllate mediante apposito Controller che funge da interfaccia tra i bus e la singola periferica.

pag 6

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

CPU Central Processing Unit (Unità Centrale di Processo).

Cuore del sistema di elaborazione. Compito della CPU è quello di “leggere” sequenzialmente dalla memoria

centrale (mediante i bus) le istruzioni che compongono il programma, e “provvedere” alla loro esecuzione.

Caricamento ed esecuzione di un programma

Nelle macchine attuali i programmi sono memorizzati in forma binaria all‟interno dell‟HD, mentre nella macchina di

Von Neumann erano memorizzati direttamente in forma binaria all‟interno di schede perforate. In entrambi i caso

però, per poter essere eseguito, il programma deve prima essere caricato in Memoria Centrale.

Nella macchine attuali per caricare un programma in Memoria Centrale è sufficiente fare doppio click sull‟icona

dell‟applicazione desiderata. Nella macchina di Von Neumann un apposito pulsante forzava la lettura della scheda

perforata ed il suo caricamento in memoria.

Una volta caricato il programma in Memoria Centrale, la CPU, attraverso i Bus, provvede a leggere una alla

volta le istruzioni che costituiscono il programma e ad eseguirle con la seguente sequenza:

1) Legge l’istruzione dalla Memoria Centrale portandola all’interno della CPU stessa

2) Decodifica l’istruzione caricata

3) Esegue l’istruzione

e quindi passa a caricare l’istruzione successiva e così via fino all’ultima istruzione del programma.

Clock

L‟attività della CPU è regolata mediante un clock esterno generato mediante un oscillatore ad elevata precisione. In

corrispondenza di ogni colpo di clock la CPU esegue una certa operazione. I sistemi 8086 utilizzavano un clock pari

a 4,77 MHz, il che significa che erano già in grado di eseguire 4,77 milioni di operazioni al secondo.

Nota: L‟esecuzione di una istruzione è una operazione “complessa” che richiede solitamente più colpi di clock.

La Memoria Centrale

La Mem Centrale è costituita da una Sequenza di Bytes. Enorme cassettiera numerata in cui ogni cassetto rappresenta

un byte (o comunemente cella di memoria). Il primo byte ha indirizzo 0. L‟ultimo byte ha indirizzo pari a tutti 1.

Ogni cassetto contiene un dato, mentre i numeri sui cassetti rappresentano gli indirizzi che permettono alla CPU di

individuarli senza ambiguità. La Memoria Centrale è costituita da tre “zone” differenti: RAM, ROM, CACHE

pag 7

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

RAM Random Access Memory

Random Access Memory significa che la CPU può accedere in modo diretto a qualsiasi cella della memoria,

cioè il tempo di accesso non dipende dalla posizione del dato ed è sempre lo stesso per qualsiasi cella.

Questo per distinguerla dalla memorie come l‟Hard Disk o il Floppy Disk in cui, per poter leggere un dato,

occorre prima eseguire un posizionamento della testina di lettura sulla traccia in cui si trova il dato da leggere.

Volatile (spegnendo il computer tutto il suo contenuto viene perso),

Veloce

Costosa

Riscrivibile (RW). L‟operazione di scrittura sovrascrive il contenuto precedente

ROM

Una piccola porzione della memoria centrale è realizzata con tecnologia ROM (Read Only Memory), che è:

A sola lettura

permanente, nel senso che i dati rimangono memorizzati anche in assenza di alimentazione.

ad accesso casuale ma a blocchi (non posso leggere / scrivere il singolo byte).

All‟interno della ROM è memorizzato il cosiddetto firmware contenente:

Le istruzioni di boot necessarie all‟avvio della macchina con i test sui principali dispositivi hardware

Alcune istruzioni del BIOS che servono ad interfacciare il SO con l‟hardware di base della macchina,

rendendo il SO indipendente dall‟hardware sottostante (un tempo CMOS con batteria oggi FLASH

persistente senza necessità di alimentazione persistente

Per accedere al BIOS occorre premere il tasto F2 o CANC in fase di avvio.

Cache

La RAM cache è una RAM molto più veloce realizzata con tecnologia SRAM (Static RAM). La RAM cache sfrutta

il principio di località dei programmi, nel senso che se un programma utilizza un certo dato, è molto probabile che

negli istanti successi riutilizzi quel dato o i dati vicini. Per cui quando il programma accede ad un dato della memoria,

questo dato ed i suoi dati vicini vengono duplicati all‟interno della cache, in modo che, in caso di accesso successivo,

la CPU possa prelevare i dati direttamente dalla cache (in modo molto più rapido), senza più accedere alla memoria.

Nota: Con il termine cache si indica genericamente una memoria veloce di piccole dimensioni utilizzata come

polmone per trasferire dati fra dispositivi operanti a velocità di lavoro diverse fra loro (uno più veloce e l’altro più

lento). Ad esempio fra HD e RAM (fra cui può esserci anche un fattore 1000. La RAM cache, utilizzata come

polmone fra RAM (più lenta) e CPU (più veloce) è un caso particolare di cache

Dimensioni della Memoria Centrale

La dimensione dell’Address Bus è quella che determina il massimo numero di celle della memoria che possono

essere indirizzate, cioè la dimensione massima della memoria centrale.

Se l’Address Bus ha n bit, può indirizzare 2n celle di memoria centrale (2n possibili combinazioni)

In un sistema 8086 l‟Address Bus ha dimensione 20 bit per cui può indirizzare 220 celle di memoria, cioè 1 MBytes.

Si ricorda che:

1 KByte = 1000 bytes

1 Mbyte = 1 milione di bytes

1 GByte = 1 miliardo di bytes

1 TByte = 1000 miliardi di bytes

103

106

109

1012

(2^10 = 1024 Bytes = 1 kByte)

(2^20 = 1024 kBytes = 1 MByte)

(2^30)

(2^40)

I BUS

Componenti che consentono la comunicazione fra CPU, Memoria Centrale e Periferiche.

Fisicamente consistono in un insieme di piste tracciate su un circuito stampato costituente la motherboard (o main

board), più eventuali componenti elettronici necessari al mantenimento delle forme d‟onda trasmesse.

Il BUS di un sistema di elaborazione, da punto di vista logico, può essere suddiviso in tre parti :

pag 8

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

Address Bus utilizzato dalla CPU per indirizzare la memoria centrale. E‟ unidirezionale, pilotato quasi

sempre dalla CPU. Nei sistemi 8086 è grande 20 bit

Data Bus dove transitano i dati che la CPU scambia con la memoria centrale e con le altre periferiche. Il Bus

Dati è condiviso fra tutti i moduli dell‟elaboratore. Nei sistemi 8086 è grande 16 bit

Control Bus serve sostanzialmente a controllare l’hardware esterno alla CPU, indicando il tipo di

operazione che il sistema deve eseguire. E‟ utilizzato dalla CPU ad esempio per stabilire chi in ogni

momento può leggere / scrivere sul Data Bus. Il dispositivo selezionato viene abilitato mediante apposito

segnale di Chip Select, derivato dagli indirizzi generati sull’Address Bus.

Poiché più dispositivi diversi possono assumere il controllo dei Bus, occorre un dispositivo che funga da arbitro del

bus. Nei sistemi più semplici questo compito è svolto dalla CPU (8086), mentre nei sistemi più complessi il compito è

riservato a dispositivi specifici (Bus Controller)

Le Periferiche nei Sistemi Moderni

CPU, Memoria Centrale e Bus costituiscono il nucleo centrale di un Sistema di Elaborazione.

Le periferiche rappresentano tutte le parti accessorie che non servono direttamente all‟elaborazione dei dati, ma la

cui presenza è tuttavia necessaria all‟utilizzo dell‟ elaboratore, consentendo ad esempio un‟uscita visiva dei risultati

senza doverli ripescare dalla memoria (situazione comune nella 1° generazione di elaboratori, negli anni cinquanta).

Periferiche di input In ordine cronologico si possono ricordare interruttori, schede perforate, tastiere, mouse,

scanner, fotocamere e telecamere,

Periferiche di output. In ordine cronologico si possono ricordare schede perforate, stampanti, video, dispositivi

generatori di suoni (dai buzzer alle più moderne schede sonore).

Periferiche di memoria di massa servono per memorizzare grossi quantitativi di dati (HD) o come supporto mobile

per il trasporto di dati da un elaboratore all‟altro (floppy). Le memorie di massa sono memorie permanenti, più

economiche e più capienti rispetto alla memoria centrale. Cronologicamente come memorie di massa sono state

utilizzate schede perforate, nastri magnetici, dischi magnetici (da 8” poi da 5” ¼ in grado di memorizzare 360

kBytes, poi da 3” ½ in grado di memorizzare 1,44 mBytes), ed infine dischi ottici (CD e DVD).

Scede di Comunicazione porte seriali, parallele e USB, schede di rete, modem.

In genere, mentre CPU e RAM si interfacciano direttamente ai Bus, le periferiche non sono connesse direttamente ai

bus di sistema, ma si appoggia ad una scheda di controllo detta Controller o adapter il cui compito è quello di far

comunicare due mondi differenti: la CPU e la periferica che utilizza un proprio standard diverso da quello della CPU.

Le Schede di Controllo vengono montate in appositi slot ortogonali al senso di percorrenza dei BUS. Questa

struttura consente una facile espansione modulare del sistema con l‟aggiunta di nuove schede all‟interno degli slot.

BUS SCSI

CPU

CONTROLLER

SCSI

MEMORIA

RAM

ROM

BOOT/BIO

S

BUS DATI

BUS INDIRIZZI

Stampante SCSI

Hard disk SCSI

VIDEO

ADAPTER

OUTPUT

INTERFACCIA

TASTIERA

INPUT

BUS CONTROLLI

pag 9

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

Avvio del Personal Computer

All‟avvio tutte le applicazioni, compreso il SO, sono memorizzate su HD e la RAM è completamente vuota”.

In realtà una piccola porzione della Memoria Centrale è di tipo persistente (ROM), programmata dal costruttore della

motherboard e contenente il cosiddetto firmware della macchina, cioè:

Un piccolo segmento di codice che serve, all‟avvio, per caricare nella memoria principale il SO e quanto

necessario al funzionamento della macchina (procedura di Bootstrap)

Alcune istruzioni che servono ad interfacciare il SO con l‟hardware della macchina, rendendo di fatto il SO

indipendente dall‟hardware sottostante. Queste istruzioni nel loro insieme rappresentano il BIOS (Basic

Input Output System ) della macchina.

Bootstrap

In corrispondenza della pressione del pulsante di avvio, viene eseguita la cosiddetta procedura di bootstrap, che

consiste nell‟esecuzione del programma scritto all‟interno della ROM di sistema (indirizzo FFFF0 dove c‟è una

istruzione di salto ad un altro indirizzo in cui sono effettivamente scritte le istruzioni di avvio) che provvede a:

1. Riconoscere e testare i principali componenti hardware della macchina (Power On Self Test) ovvero il

funzionamento del processore, presenza della memoria, presenza di un HD o di un lettore CD da cui caricare

il SO, presenza della tastiera e di una scheda video.

2. Caricare il sistema operativo (BOOTSTRAP), ovvero leggere il primo settore dell‟hard disk e caricarne il

contenuto in una apposita zona della memoria centrale (indirizzo 0000). Nel primo settore di una HD si

trovano solitamente le istruzioni per caricare in memoria l‟intero SO memorizzato sull‟HD stesso.

IL BIOS (Basic Input Output System )

Una volta avviato, il SO operativo continuerà a lavorare in stretta collaborazione con il BIOS, che gestisce tutto

l‟interfacciamento con l‟hardware. Quando il SO deve inviare dei dati verso una porta del PC (ad es la porta USB),

mediante una apposita chiamata al BIOS (realizzata di solito tramite un interrupt), “passa” i dati al BIOS che li

trasferisce all‟interfaccia hardware della porta indicata. Allo stesso modo quando una porta deve trasmettere dei dati

al SO, è il BIOS che li riceve e poi li “passa” al SO. In questo modo il SO è completamente svincolato dall‟hardware

sottostante e può operare su piattaforme diverse senza dover essere modificato. Le procedure del BIOS consentono

allo stesso SO di utilizzare hardware profondamente diversi (ad es. un 386 ed un Pentium).

Tutti i Personal Computer, qualunque sia il produttore, dovranno avere nel BIOS lo stesso insieme di funzioni

base (con gli stessi parametri di ingresso e gli stessi di uscita) che verranno poi sfruttate dal sistema operativo.

I Driver

In un PC esistono altre parti di software non direttamente supportate dal BIOS ma strettamente necessarie per il

funzionamento di alcune parti hardware. Si tratta dei device driver relativi a dispositivi non supportati dal BIOS (es

schede video avanzate) che devono essere installati dopo il Sistema Operativo e che vengono salvati in apposite

cartelle di sistema (C:WINDOWS\DRIVER) e caricati in memoria dal SO al momento della necessità.

Spesso occorre installare nuovi driver anche per le periferiche già supportate dal BIOS, in modo da sfruttarne

al meglio le caratteristiche di funzionamento, in particolare per quanto concerne dischi rigidi e schede video.

Flash ROM

Nelle macchine attuali le ROM non sono più strettamente Read Only, ma si parla di Flash ROM, cioè ROM che

possono anche essere modificate dall‟utente mediante una apposita finestra di interfaccia del BIOS. In fase di avvio

della macchina, ad un certo punto compare la scritta Press <F2> <DEL> to enter setup. Premendo il tasto indicato

è possibile interrompere la fase di avvio ed aprire una finestra di configurazione del BIOS, in cui è possibile ad es :

modificare la sequenza di boot (normalmente prima CD, poi HD infine la rete)

gestire Hard Disk aggiuntivi,

inserire una password a livello di BIOS che verrà richiesta all‟accensione prima ancora dell‟avvio di Windows.

E‟ possibile impostare una password BIOS anche soltanto come protezione del BIOS stesso, richiesta ogni

volta che l‟utente tenta di entrare nel BIOS per effettuare delle modifiche.

Un apposito comando consente di ripristinare i valori originali del BIOS, memorizzati in copia sempre nella ROM. Il

ripristino del BIOS più essere eseguito anche via hw spostando per alcuni secondi un apposito JUMPER di Reset.

pag 10

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

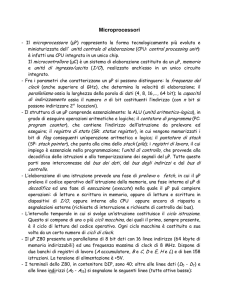

Il microprocessore 8086

Processore a 16 bit, nel senso che i registri interni sono tutti a 16 bit.

E‟ costituito essenzialmente da tre parti:

EU Execution Unit E‟ l‟unità che si occupa di eseguire le istruzioni. L‟elemento principale della EU è la ALU

Arithmetic Logic Unit . una macchina basata su logica combinatoria che si occupa di svolgere le operazioni

logiche e aritmetiche in modo simile a ciò che avviene nelle calcolatrici tascabili.

BIU Bus Interface Unit E‟ l‟unità che si occupa dell‟interfacciamento ai bus

CU Control Unit. Macchina a stati che rappresenta il vero e proprio cuore della CPU. Ordina alla BIU di caricare la

prossima istruzione, la decodifica e quindi chiede alla EU di eseguirla. Al termine ordina il caricamento

dell‟istruzione successiva. Genera i segnali per coordinare e sincronizzare le attività di tutti i dispositivi esterni.

Registri (14 Registri tutti a 16 bit più un registro di stato)

Registri di Segmento CS, SS, DS, ES Utilizzati per gestire la segmentazione dei programmi. Contengono l‟indirizzo

assoluto di partenza dei vari segmenti che compongono un programma per Personal Comnputer.

IP (Instruction Pointer) detto anche PC (Program Counter). Contiene l‟indirizzo relativo (offset) della prossima

istruzione da eseguire rispetto all‟inizio del Segmento di Codice

IR Instruction Register. Registro in cui viene memorizzato il codice binario dell‟istruzione in esecuzione.

SP Stack Pointer. Puntatore allo Stack. Contiene ‟indirizzo relativo (offset) della cella corrente dello stack rispetto

all‟inizio del Segmento di Stack

Registri Dati Interni alla ALU. Utilizzati per memorizzare operandi e risultati delle operazioni aritmetiche.

AX, BX, CX e DX Utilizzati per i calcoli. AX è il registro più utilizzato ed è chiamato accumulatore.

Ognuno di questi registri è suddiviso in due registri da 8 bit: parte alta (es AH) e parte bassa (es AL).

Registri di Indirizzamento dei Dati Utilizzati per gestire gli offset all‟interno del Segmento Dati

DI (Destination Index), SI (Source Index),

BP Base Pointer registro particolare che gestisce gli indirizzamenti all‟interno del segmento di stack

MDR Memory Data Register Registro non direttamente accessibile a livello di programma utente. E‟ il registro in cui

vengono memorizzati i dati letti dal bus Dati o che devono essere inviati al bus Dati.

MAR Memory Address Register Analogo del precedente riferito però al bus Indirizzi. Contiene l‟ultimo indirizzo di

memoria a cui la CPU ha fatto riferimento (unico registro a 20 bit).

Registro di Stato (PSW Processor Status Word) Contenente alcuni flag di stato settati dalla ALU al termine di una

operazione aritmetiche. Contengono informazioni sul tipo di risultato ottenuto. I bit utilizzati sono in tutto 9:

SF (Sign Flag) Bit di segno, indica il segno del risultato. (0 risultato positivo, 1 negativo). Coincide con MSB

ZF (Zero Flag) Bit di zero. Indica che l‟operazione algebrica corrente ha dato come risultato Zero

PF (Parity Flag) Bit di parità (1 se il risultato contiene un numero pari di 1)

CF (Carry Flag) Bit di Carry . Utilizzato nell’algebra dei numeri Unsigned. Diventa 1 nel momento in cui una

somma tra interi positivi produce un riporto (250 + 10). Nel caso della differenza (somma tra un numero

positivo ed un numero negativo), CF diventa 1 se per eseguire la sottrazione occorre un prestito, cioè se il

risultato della somma è negativo, cioè ancora se la somma tra i due numeri non fornisce riporto.

OF Bit di overflow. L‟operazione ha sforato la massima dimensione consentita. Utilizzato nell‟algebra dei

numeri Signed. La somma di numeri produce overflow quando i due operandi hanno lo stesso segno ed il

risultato presenta un segno discorde rispetto agli operandi (120 + 10). La somma fra due numeri d segno differente

non produce MAI overflow.

- facendo 250 + 10 viene attivato Carry ma non Overflow

- facendo 120 + 10 viene attivato Overflow ma non Carry

AF (Auxiliary Flag) Indica il riporto sul quarto bit (utilizzato nelle operazioni BCD).

I 3 seguenti Flag sono invece Read / Write :

DF (Direction Flag) Imposta la modalità di incr / decr (1) automatico dei reg SI DI nelle istruzioni sulle stringhe

IF (Interrupt Flag)Abilita la gestione degli Interrupt mascherabili

TF (Trap Flag) Abilita la generazione di una interruzione alla fine di ogni istruzione (debugger).

pag 11

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

Formato delle istruzioni Assembly

Qualunque sia il linguaggio utilizzato per la scrittura del programma, il programma finale .exe sarà un file binario

costituito da una sequenza di istruzioni Assembler che hanno normalmente una lunghezza compresa tra 1 e 6 byte.

1 byte contenente il codice dell’istruzione (max di 255 istruzioni possibili, con un set di 92 istruzioni base )

1 byte (eventuale) relativo alle modalità di indirizzamento che indica quali registri sono coinvolti nell‟operazione in

modo diretto o indiretto (base relative) e se l‟operazione riguarda anche la memoria o contiene dati immediati

2 byte (eventuali) contenenti l’indirizzo di memoria della cella eventualmente coinvolta nell‟operazione

2 byte (eventuali) contenenti il dato immediato da utilizzare nell‟operazione (che può occupare 1 o 2 bytes).

Assembly 8086 ammette anche dati su 4 bytes, ma poiché i registri sono tutti a 2 bytes, è impossibile spostare 4 bytes

insieme. In tal caso occorre dunque necessariamente scrivere 2 istruzioni ognuna delle quali sposti 2 bytes.

Ciclo delle caricamento ed esecuzione delle istruzioni

Il sistema inizia l‟attività (reset) impostando un valore predefinito all‟interno del Program Counter. Quindi carica

all‟interno del registro IR la prima istruzione del programma, la esegue e, al temine, incrementa il PC per un numero

di Bytes pari alle dimensioni dell‟istruzione appena eseguita e carica la prossima istruzione.

Al temine di ogni istruzione CU incrementa il Program Counter e legge dalla memoria la prossima istruzione da

eseguire la carica nel registro IR, la interpreta, e la esegue, nel senso che genera i segnali elettrici opportuni verso i

dispositivi coinvolti nell‟esecuzione dell‟istruzione. Tre fasi principali (che possono anche diventare 5) indicate come

Fetch (caricamento)

Decode

Execute

Fase di Fetch

- La CU trasferisce nel registro MAR l‟indirizzo della prossima istruzione da caricare (letto dal registro PC)

- Il contenuto di MAR viene caricato sull‟Address Bus e contemporaneamente viene abilitato il segnale Read

- La memoria decodifica l‟indirizzo dell‟istruzione da caricare, e la trasferisce sul Data Bus

- L‟istruzione viene portata dal Data Bus su MDR

- L‟istruzione viene copiata da MDR a IR

- Il registro IP viene incrementato di una quantità pari alle dimensioni dell‟istruzione caricata

Fase di Decode

- La CU decodifica l‟istruzione verificando quali registri sono coinvolti

- La CU legge un eventuale dato aggiuntivo dalla memoria centrale, eseguendo eventualmente un secondo

ciclo di fetch e provvedendo ad incrementare ulteriormente il registro IP.

Fase di Execute

- Carica i dati necessari sui registri di ingresso della ALU.

- CU genera i segnali di controllo verso la ALU per eseguire l‟istruzione

- Preleva il risultato dal registro di output della ALU e lo carica nel registro di destinazione o eventualmente in

MDR se il risultato deve essere salvato in memoria.

- Se il risultato deve essere salvato in memoria, esegue un ultimo ciclo (5°) di scrittura in memoria del risultato

Terminata l‟istruzione in corso, la CU riprende il ciclo caricando la prossima istruzione.

Pipeline

Il termine pipeline significa catena di montaggio, intesa come parallelizzazione delle fasi di Fetch ed Execute.

L‟esecuzione sequenziale delle fasi di Fetch – Decode – Execute spreca tantissimo tempo. Durante la fase di FETCH,

mentre la BIU provvede a caricare l‟istruzione utilizzando i bus di sistema di collegamento fra CPU e memoria, la

EU rimane praticamente inutilizzata. Viceversa, durante la fase di EXECUTE dell‟istruzione da parte della EU

rimangono inutilizzati i BUS.

pag 12

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

Proprio per evitare questi tempi di inutilizzo e velocizzare le operazioni, la CPU è stata suddivisa in due parti:

EU Execution Unit che si occupa della decodifica ed esecuzione delle istruzioni (mediante la ALU)

BIU Bus Interface Unit che si occupa del fetch delle istruzioni utilizzando una piccola coda (memoria FIFO) detta

INSTRUCTION QUEUE (o coda di prefetch) in cui provvede a caricare le istruzioni successive. Questa coda

ha dimensioni 6 bytes, tanto quanto la dimensione massima di una istruzione Assembly.

Pipeline significa elaborazione parallela: mentre EU esegue l’istruzione corrente, BIU provvede a scaricare

l’istruzione successiva, con la CU che coordina tutte le operazioni. In questo modo, al termine dell‟esecuzione

dell‟istruzione corrente, la CU trova l‟istruzione successiva già pronta all‟interno della coda di prefetch.. Provvede

quindi a trasferirla alla EU, ad incrementare PC e a segnalare alla BIU di caricare la prossima istruzione. In base al

nuovo valore di PC, la BIU elimina dalla coda i byte relativi all‟istruzione “consumata”, fa avanzare gli altri byte in

testa alla coda di prefetch e provvede ad un nuovo caricamento.

Segmentazione della memoria

Un programma Assembler è suddiviso in segmenti che possono essere di tre tipi:

codice

stack

data

code segment contenente le istruzioni del programma

stack segment contenente informazioni ausiliarie (parametri e variabili locali)

data segment contenente i dati (variabili globali)

Un programma può contenere più segmenti di codice, più segmenti di dati, ma sempre solo un unico segmento

di stack.

Ogni segmento non ha una dimensione fissa (le dimensioni del segmento di codice dipendono dal numero di

istruzioni contenute nel programma, le dimensioni del segmento di dati dipende dal numero di variabili

dichiarate all‟interno del programma), ma ha una dimensione massima pari a 64 kBytes,

In fase di lancio del programma, ogni segmento del programma memorizzato su file viene caricato in Memoria

Centrale da un componente del sistema operativo, il loader, (normalmente nel primo posto libero).

La Memoria Centrale risulta pertanto segmentata, cioè suddivisa in segmenti.

Il numero massimo di segmenti non è fisso, ma dipende dalle dimensioni dei segmenti stessi.

Il processore 8086 ha una architettura a 16 bit, cioè tutti i suoi registri sono a 16 bit. Per poter eseguire un

programma in memoria, la CPU deve necessariamente conoscere l’indirizzo assoluto dell‟istruzione all‟interno della

memoria, il quale però è un indirizzo a 20 (in quanto tutti gli indirizzi di memoria, nell‟8086, sono a 20 bit).

La soluzione a questo problema è stata l‟utilizzo di un apposito registro di segmento a 16 bit, detto CS (Code

Segment Register) all‟interno del quale vengono caricati i 16 bit più significativi dell’indirizzo assoluto di

partenza del segmento all’interno della memoria. In tal caso si da per scontato che i 4 bit inferiori valgano tutti 0,

cioè che l‟indirizzo assoluto di partenza del segmento sia un indirizzo multiplo di 16.

Dopo di che un secondo registro, il program counter PC, gestisce l‟offset (cioè lo spiazzamento rispetto alla testa del

segmento) della prossima istruzione da eseguire. Il registro PC viene inizializzato con tutti zeri (offset della prima

istruzione rispetto alla testa del segmento), dopo di che viene incrementato in corrispondenza dell‟esecuzione di ogni

singola istruzione.

In ogni istante, per calcolare il reale indirizzo assoluto (all‟interno della Memoria Centrale) relativo alla prossima

istruzione da eseguire, occorre

Calcolare l’indirizzo di partenza del segmento, aggiungendo 4 zeri in coda al Code Segment Register

Eseguire la somma fra l’indirizzo assoluto di partenza del code segment e PC

CS

16 bit

xxxx xxxx xxxx xxxx 0000

+

PC

16 bit

0000 0000 0000 yyyy

=

Effective Address

20 bit

xxxx xxxx xxxx xxxx yyyy

pag 13

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

Questo calcolo viene di solito indicato con la notazione: Indirizzo Assoluto = CS : PC

Nota: Da un punto di vista strettamente matematico l’indirizzo assoluto può essere calcolato mediante la seguente

formula :

Indirizzo Assoluto = CS * 16 + PC

Moltiplicare un numero binario per 16 significa infatti traslarlo verso sinistra di 4 posizioni

Data e Extra Data Segment

Allo stesso modo del segmento di codice, nella prossima area libera della memoria viene caricato il segmento dati

contenente le variabili globali dell‟applicazione. Il Segmento di Dati viene gestito allo stesso identico modo del

Segmento di Codice. Il registro DS (Data Segment Register) contiene i primi 16 bit dell‟indirizzo assoluto di

partenza del Segmento Dati all‟interno della Memoria Centrale (assumendo a 0 i rimanenti 4 bit).

I registri SI e DI sono utilizzati per gestire gli offset dei vari dati rispetto all‟inizio del segmento.

Per calcolare gli indirizzi effettivi dei dati, si opera come per il Code Segment, cioè si aggiungono 4 zeri in coda al

valore di DS sommando poi gli offset contenuti nei registri di indirizzamento (SI, DI). Cioè :

Indirizzo Assoluto di un dato = DS : SI oppure

Indirizzo Assoluto di un dato = DS : DI

Nota: Poiché si prevedeva che 64 kBytes potessero non bastare per i dati di una applicazione, l’8086 può gestire

contemporaneamente 2 segmenti di dati, detti Data Segment e Extra Data Segment, i cui indirizzi di partenza sono

memorizzati rispettivamente nei registri di segmento DS (Data Segment Register) e ES (Extra Segment Register)

Stack Segment

Il terzo segmento di un programma Assembly è lo Stack Segment in cui vengono salvate le variabili locali ed i

parametri. A differenza dei segmenti precedenti, nello stack il programma non può andare a scrivere direttamente,

ma può scrivere soltanto in modalità LIFO, cioè impilando i dati uno sopra l‟atro. L‟istruzione PUSH consente di

salvare una informazione nello stack, mentre l‟istruzione POP consente di prelevare dallo stack l‟ultima

informazione memorizzata,

L’indirizzo di partenza del Segmento di Stack all’interno della Memoria Centrale (primi 16 bit) è

memorizzato all’interno di apposito registro di segmento detto SS (Stack Segment Register).

Il registro SP (Stack Pointer) gestisce gli offset all’interno dello stack rispetto all’inizio del segmento.

Il segmento di stack viene gestito in modo differente rispetto agli altri segmenti, nel senso che viene creato di una

dimensione fissa (tipicamente 1024 bytes, comunque impostabile via codice dal programma utente), e lo Stack

Pointer, anziché puntare alla cella iniziale (con offset 0000), punta all‟ultima cella in fondo (con indice 1024),

contenente il valore speciale EOS (End Of Stack).

Ogni volta che si aggiunge una informazione all‟interno della stack mediante PUSH, SP viene decrementato di

una quantità pari alle dimensioni dell‟ informazione salvata.

Ad esempio salvando un dato grande 2 bytes, SP verrà decrementato di 2 diventando 1022

Quando si preleva una informazione dallo stack mediante POP, SP viene incrementato di una quantità pari alle

dimensioni dell‟informazione. Se si continuano ad inserire dati ed SP viene decrementato fino ad arrivare a 0 si

ottiene un errore di stack overflow che significa che lo stack è arrivato oltre il massimo della capienza

SP punta sempre all’ultima informazione salvata dentro lo stack.

Cenno sulla Interrupt Vector Table

All‟indirizzo 00000 della RAM è contenuto la cosiddetta Interrupt Vector Table grande 1024 Bytes e contenente

256 Interrupt da 4 Bytes ciascuno. Quando alla CPU arriva una richiesta di Interrupt, la CPU esegue un salto

all‟interno della Interrupt Vector Table andando a leggere i 4 bytes relativi all‟interrupt ricevuto. In questi 4 bytes c‟è

l‟indirizzo assoluto (CS e Offset) della procedura da eseguire in risposta all‟interrupt.

pag 14

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

PIEDINATURA 8086

Ciclo Macchina (o Ciclo di Bus)

Si definisce Ciclo Macchina o Ciclo di Bus il ciclo completo utilizzato dalla CPU per accedere alla memoria

centrale in lettura o in scrittura. Esso è costituito tipicamente da 4 fasi distinte ciascuna di durata pari ad un ciclo di

clock. Queste fasi sono indicate normalmente come T1, T2, T3, T4, con il possibile inserimento di un numero

indefinito di stati Tw tra T3 e T4 se il dispositivo a cui si intende accedere è più lento rispetto al tempo di clock.

Piedinatura della CPU 8086

1)

2)

3)

4)

5)

6)

7)

8)

9)

10)

11)

12)

13)

14)

15)

16)

17)

18)

19)

20)

GND

BUS_14

BUS_13

BUS_12

BUS_11

BUS_10

BUS_9

BUS_8

BUS_7

BUS_6

BUS_5

BUS_4

BUS_3

BUS_2

BUS_1

BUS_0

NMI

INTR

CLK

GND

40)

39)

38)

37)

36)

35)

34)

33)

32)

31)

30)

29)

28)

27)

26)

25)

24)

23)

22)

21)

VCC

BUS_15

AddBUS_16

AddBUS_17

AddBUS_18

AddBUS_19

BHE

MIN/MAX

RD

HOLD

HOLDA

WR

M/IO

DT/R

DEN

ALE

INTA

TEST

READY

RESET

VCC e GND

VCC = 5 Volt. All‟interno di una architettura 8086 i cavi di tensione sono normalmente disponibili all‟interno di

connettori a 4 pin così strutturati::

Rosso

=>

5V

Nero

=>

riferimento di massa per i 5 V

Nero

=>

riferimento di massa per i 12 V (ponticellato con il precedente)

Grigio

=>

12V

Questi fili, all‟interno della motherboard, diventano parte integrante del Control Bus. Il 12 Volt può servire per

l‟alimentazione di dispositivi quali floppy disk, hard disk, video adapter.

CLK

Clock. Il clock è ottenuto mediante un apposito oscillatore esterno che, a seconda del cristallo di quarzo utilizzato,

può generare frequenza differenti. Nell‟architettura 8086 come oscillatore è utilizzato il Generatore di clock Intel

8284 che produce una onda quadra di frequenza pari a 14,318 MHz, che, divisa per 3, invia al processore, sul pin

19, un clock di 4.77 MHz, con Duty Cycle del 33 %. Ogni colpo di clock ha dunque una durata temporale pari a 1

/ 4.77 = 0,210 usec, cioè 210 nsec. I fronti di discesa e di salita hanno una durata inferiore ai 10 nsec. Il ciclo di

bus ha una durata complessiva pari a 840 nsec. I cicli di I/O impiegano in genere 5 colpi di clock, per una durata

complessiva di 1,05 usec.

ALE [output]

Address Latch Enable. Impulso attivo soltanto durante la Fase T1. Consente di demultiplexare i Bus pilotando

appositi Latch bistabili (tipicamente 8282) da quali hanno origine Address Bus e Data Bus separati.

pag 15

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

AD

Address Bus o Data Bus a seconda del valore del pin ALE. Nei sistemi 8086 Address Bus e Data Bus sono

multiplexati nel senso che, per risparmiare sul numero di piedini, il processore presenta soltanto 20 pin di bus,

che possono fungere sia da Address Bus sia da Data Bus a seconda dello stato del segnale ALE

Durante la fase detta T1 la CPU immette su queste linee i segnali di indirizzamento della cella di memoria a cui

intende accedere. Durante le fasi T2, T3, T4 tutte queste linee fungono da Data Bus.

MIN/MAX [input]

Sono due diverse modalità per collegare elettricamente l‟8086 alla circuiteria circostante. In MINIMUM MODE

(ottenuto collegando il piedino a +5V) il processore 8086 opera da solo, mentre il MAXIMUM MODE è

utilizzato quando l‟8086 lavora in tandem con il coprocessore matematico 8087 o con altri processori. Nel modo

massimo, oltre al 8087, necessita anche di altri chip esterni quale il controllore di bus 8288. I pin indicati di

seguito sono riferiti al modo MINIMO. Nel modo MASSIMO diversi pin cambiano di significato.

RD [output]

Read. Indica che la CPU sta eseguendo un ciclo di lettura (in memoria o in IO). Attivo in T2, T3, Tw

WR [output]

Write. Indica che la CPU sta eseguendo un ciclo di scrittura (in memoria o in IO). Attivo in T2, T3, Tw

M/IO [output]

Indica se il ciclo di bus è riferito alla Memoria (1) oppure ad un dispositivo di IO (0). Deve rimanere impostato

per l‟intero ciclo di bus. La combinazione tra M/IO e RD produce i segnali MEMR e IOR utilizzati per pilotare

rispettivamente la lettura dalla memoria e la lettura da IO. La combinazione tra M/IO e WR produce i segnali

MEMW e IOW utilizzati per pilotare rispettivamente la scrittura verso la memoria e la scrittura verso IO.

BHE [output]

Bus High Enable. Attivo soltanto nella fase T1, quando la CPU sta cercando di accedere ad una cella di memoria.

- Se BHE è attivo (basso) significa che la CPU intende accedere ad una intera word della memoria, cioè al byte

contenuto nell‟indirizzo corrente e al byte successivo.

- Se invece BHE non è attivo (alto) significa che la CPU intende accedere soltanto ad un singolo byte della

memoria. Poiché le variabili sono sempre allineate alla word (A0 = 0), il valore di A0, abbinato a BHE,

consente di accedere al byte alto (A0 = 1) oppure al byte basso (A0 = 0).

INTR [input]

Interrupt Request Segnale di ingresso che viene testato al termine di ogni istruzione prima di passare al caricamento

dell‟istruzione successiva per verificare se vi è una richiesta pendente di interrupt da soddisfare. E‟ attivo alto e può

essere mascherato internamente resettando via software il bit di disabilitazione dell‟interrupt (IF Interrupt Flag).

NMI [input]

Not Maskable Interrupt. Segnale di ingresso che indica la richiesta di un interrupt non mascherabile che dovrà

essere eseguito al termine dell‟istruzione corrente.

INTA [output]

Interrupt Ackowledge. In Risposta all‟interrupt request (mascherabile o non mascherabile), la CPU avvisa il

dispositivo richiedente che è pronta per avviare la procedura di gestione dell‟interrupt. Il segnale rimane attivo per

l‟intero ciclo di esecuzione dell‟interrupt

HOLD [input]

Segnala alla CPU che un altro dispositivo (tipicamente il DMA Controller) ha richiesto il controllo del bus.

Mentre nel caso di Interrupt Request la CPU termina comunque l‟istruzione in corso, nel caso di DMA request la

CPU si limita a terminare il ciclo di bus in corso ponendo le proprie linee di dati, indirizzi e controllo in stato di

alta impedenza (tristate), in pratica disconnettendole dai bus. La CPU, per quanto possibile, continua la propria

esecuzione se questa non richiede l‟accesso ai bus.

pag 16

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

HOLDA [output]

La CPU avvisa il dispositivo richiedente (DMA Controller) di avergli ceduto il controllo dei bus. Quando il

dispositivo ha terminato di usare il bus riporta basso il segnale di HOLD e la CPU ne riprende possesso.

READY [input]

La memoria avvisa la CPU di avere terminato la lettura / scrittura del dato

RESET [input]

Viene utilizzato per reinizializzare il processore. Il segnale di Reset vene generato all‟accensione subito dopo

l‟accensione da un circuito accessorio dell‟alimentatore, quando i livelli di tensione si sono stabilizzati (si sono

caricati tutti i condensatori), oppure mediante un apposito pulsante esterno.

In corrispondenza del segnale di Reset la CPU provvede a caricare FFFF dentro CS e 0000 dentro IP

Per essere intercettato dalla CPU, il Reset deve rimanere attivo per almeno 4 colpi di clock consecutivi. Prima di

arrivare alla CPU viene fatto passare attraverso il generatore di clock 8284 per sincronizzarlo con il clock stesso

TEST [input]

Segnale d‟ingresso esaminato dall‟istruzione WAIT. Se TEST è basso il microprocessore continua normalmente

nell‟esecuzione del programma, altrimenti si arresta in stato di attesa e vi resta fino quando TEST non ritorna

basso. Utilizzato nella comunicazione con il coprocessore matematico 8087 o altri coprocessori.

DT/R e DEN [output]

Data Transmit / Receive. 1 = Transmit 0 = Receive. DEN = Data Enable. Devono rimanere impostati per l‟intero

ciclo di bus (tutte e quattro le fasi). Servono per pilotare eventuali tranceiver.

Indirizzamento della memoria

La memoria ROM è realizzata mediante più banchi di tipo INTEL 2732 (a 24 pin) aventi un indirizzamento a 12 bit

dunque in grado di gestire 4096 bytes di memoria (4 kBytes). Poiché la ROM può soltanto essere letta, viene inviato

alla ROM soltanto il segnale di MEMR, inviato al pin OE (output enable) della memoria. Il pin CS (chip select) è

ottenuto mediante una decodifica esterna dei bit di indirizzo non direttamente collegati al dispositivo.

A13

A19

A0

CS

Data 0 - 7

Address 1-12

MEMR

OE

Gli altri 8 bit della word (byte alto) sono ottenuti mediante un secondo banco di memoria pilotato

parallelamente. Sulla porta AND degli indirizzi, al posto del semplice A0, ci sarà la condizione (A0 = 1 OR BHE)

L‟intera memoria viene vista dalla CPU come suddivisa in due banchi, il banco relativo ai bytes pari (parte bassa di

un numero) ed il banco relativo ai byte dispari (parte alta di un numero). I due banchi possono essere indirizzati

congiuntamente (BHE = 0), oppure separatamente mediante A0 (A0 = 0 byte pari, A0 = 1 byte dispari).

L‟acceso alla RAM avviene in modo analogo, ma sono di solito disponibili sia il pin WE (write enable), sia il pin RE

(Read Enable). Ad esempio l‟integrato 2142 rappresenta un banco di RAM da 1024 Bytes (1 kByte) a 24 pin (10 pin

di Address, 8 pin di Data, due chip select, WE, RE, Vcc, GND). Anche in questo caso la word è ottenuta mediante un

secondo banco di memoria pilotato parallelamente. CS2 è collegato a massa (sempre abilitato) per il banco

contenente la parte bassa del dato, mentre è collegato a BHE per il banco contenente la parte alta.

Nota: Se il dato è ad un solo byte, non ci sono particolari problemi (il dato verrà letto dal banco di memoria indicato

da A0.). Se però il dato occupa due byte può essere allineato ad un indirizzo dispari oppure ad un indirizzo pari Se è

allineato ad un indirizzo pari,significa che byte basso e byte alto hanno lo stesso indirizzo tranne che per A0 (0 per il

byte basso e 1 per il byte alto). Ciò significa che i due byte potranno essere letti parallelamente dalla CPU

all’interno dei due banchi in un unico ciclo macchina.

pag 17

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

Se invece il dato è allineato ad un indirizzo dispari, significa che byte basso e byte alto, oltre a A0, hanno anche la

parte rimanente di indirizzo differente. Ciò significa che la CPU non può indirizzarli parallelamente e dovrà per

forza eseguire due cicli macchina differenti (dato non allineato). Per questo motivo, quando si dichiarano grandi

strutture dati, anche nei linguaggi di alto livello come il C, è bene verificare che i dati abbiano sempre un

allineamento pari.

Il Ciclo Macchina o Ciclo di Bus

Ciclo di lettura / scrittura della memoria composto da 4 cicli di clock.

B

U

S

I

N

D

I

R

I

Z

Z

I

R

E

G

.

I

N

D

I

R

I

Z

Z

I

READY

0

D

E

C

O

D

E

R

1

2

3

R

E

G

I

S

T

R

O

B

U

S

D

A

T

I

4

5

6

D

A

T

I

7

ALE

MEMR

MEMW

CONTROL BUS

Ciclo di Lettura (es. MOV AX, VAR)

FASE T1 : La CPU mediante ALE abilita l‟Address Bus e ci scrive sopra l’indirizzo della cella a cui deve accedere.

Contemporaneamente abilita i segnali BHE e M/IO. Al termine della fase T1 la memoria provvede a salvare

l‟indirizzo all‟interno del proprio “Registro Indirizzi”.

FASE T2 : La CPU attiva il segnale RD e si pone in stato di alta impedenza rispetto ai bus (in pratica si “sgancia”

dai bus). La memoria ricerca il dato richiesto.

FASE T3 : Terminata la ricerca del dato e il suo trasferimento sul “Registro Dati”, la memoria prende possesso del

Data Bus e ci scrive sopra il dato. Al termine attiva il segnale READY. Se la memoria non riesce a “scaricare” il

dato nel tempo di clock, la fase T3 può durare più colpi di clock detti Tw al termine dei quali verrà attivato il Ready

FASE T4 : La CPU legge il segnale di Ready e quindi legge il dato dal Data Bus, disattiva i segnali RD, BHE e

M/IO. In corrispondenza della disattivazione del segnale RD la memoria si “sgancia” dal Data Bus.

Ciclo di Scrittura (es. MOV VAR, AX)

FASE T1 : Esattamente come prima.

FASE T2 : La CPU attiva il segnale WR e trasferisce sul Data Bus il dato da scrivere in memoria. Al termine della

fase T2 la memoria provvede a salvare il dato all‟interno del proprio “Registro Dati”.

FASE T3 : La memoria scrive il contenuto del Registro Dati all’interno della cella puntata dal Registro

Indirizzi, attivando al termine il segnale READY. Se la memoria non riesce a “scaricare” il dato nel tempo di

clock, la fase T3 può durare più colpi di clock detti Tw al termine dei quali verrà attivato il segnale di Ready

FASE T4 : La CPU legge il segnale di Ready, disattiva i segnali WR, BHE e M/IO e si “sgancia” dal Data Bus.

pag 18

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

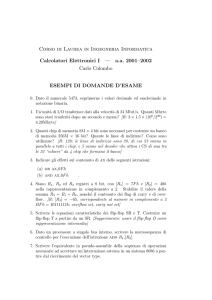

Evoluzione dei Processori Intel: Schema Riassuntivo

Anno

Processore

utilizzato

Socket e

PIN

1981

8086

1983

80286

1986

80386

1990

80486DX

1992

1994

1994

80486DX2

80486DX4

Pentium

1997

Pentium 2

1999

Pentium 3

2001

Pentium 4

2003

Pentium M

DIP

40

PLCC

68

PLCC

132

Socket1

168

Socket2

238

Socket4

273

Slot1

242

Socket

370

423

478

775 LGA

479

(Centrino)

gennaio

Core Duo

2006

(Centrino Duo)

fine

Core 2 Duo

Merom/Conroe

2006

479

775 LGA

Clock

CPU

MHz

4.77

6 – 20

typ 12,5

20 - 25 33

25 - 33 50

66

100

75 - 100

266

333

450

1 GHz

1,4 GHz

3,2 GHz

3,8 GHz

1.5 GHz

2.2 GHz

2 GHz

2,4 GHz

2,66 GHz

Clock

Base

FSB

MHz

Cache

Liv 1

Data

Bus

Address

Bus

RAM

max

RAM

typ

no

Cache

Liv 2

in-pack

no

Sistema

Operativo

256 kByte

Hard

Disk

Typ

20 MB

16 bit

20 bit

1 MByte

no

no

16 bit

24 bit

16 MBytes

2 MBytes

60 MB

no

no

32 bit

32 bit

4 GBytes

4 MBytes

100 MB

8 kB

no

32 bit

32 bit

4 GBytes

8 MBytes

200 MB

MS DOS

33

33

8 kB

no

32 bit

32 bit

4 GBytes

16 MBytes

600 MB

50

50

no

64 bit

32 bit

4 GBytes

32 MBytes

2 GB

66

100

100

133

100

133

200

100

133

166

66 100

100 133

400

533

800

400

533

667

8+8

kB

16 + 16

kB

16 + 16

kB

16 + 16

kB

MS DOS 3.2

(Windows 1.0)

MS DOS 4.0

(Windows 2.0)

MS_DOS 6.0

(Windows 3.0)

MS_DOS 6.22

(Windows 3.11)

Windows 95

256 kB

64 bit

36 bit

64 GBytes

4 GB

Windows 95 SE

256 kB

64 bit

36 bit

64 GBytes

512 kB

64 bit

36 bit

64 GBytes

32 + 32

kB

32 + 32

1 MB

2 MB

2 MB

64 bit

36 bit

64 GBytes

64 bit

36 bit

64 GBytes

per ogni core

condivisi

32 + 32

4 MB

64 bit

36 bit

64 GBytes

per ogni core

condivisi

64 MBytes

SDRAM

128 MBytes

SDRAM

256 Mbytes

SDRAM

DDR

512 MBytes

DDR

1 GBytes

DDR2

2 GBytes

DDR2

200

266

800

1066

10 GB

Windows 98

40 GB

Windows 2000

80 GB

Windows XP

160 GB

250 GB

250 GB

Windows XP

Windows Vista

L‟anno si riferisce all‟anno di commercializzazione del PC basato sul processore indicato.

L‟uscita sul mercato del processore può essere antecedente rispetto alla data di commercializzazione del PC.

pag 19

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

Evoluzione dei microprocessori INTEL

Caratteristica importantissima di tutti i processori Intel dal 8086 fino ad oggi è che tutti i processori nati dopo l‟8086

mantengono la compatibilità software, cioè consentono l‟esecuzione di programmi scritti per l‟8086 mediante

l‟utilizzo di una modalità detta 8086 virtual mode supportata da tutti i processori fino a quelli attuali.

Nota: Una caratteristica da tenere presente è che tutti i processori Intel discendenti dell‟8086 sono macchine di tipo

CISC (Complex Instruction Set Computer), cioè con un set di istruzioni complesse e a lunghezza variabile.

Questa caratteristica era utile negli anni '70 e '80, perché permetteva di risparmiare costosa memoria. In tempi più

recenti, la lunghezza variabile è diventata un tallone d'achille che complica notevolmente il progetto dei nuovi

processori, i quali dedicano una parte consistente delle loro risorse a "tradurre" il set di istruzioni x86 in uno più

razionale. L‟alternativa alla tecnologia CISC è la tecnologia denominata RISC (Reduced Instruction Set Computer),

che prevede un set ridotto di istruzioni tutte della stessa dimensione. L‟obiezione alla tecnologia RISC è che, con

un set ridotto, le operazioni più complesse devono essere eseguite via software. Poi si perderebbe la compatibilità

Architettura

In informatica, architettura a 64 bit indica che il formato standard di una variabile semplice (intero, puntatore, handle

ecc.) è di 64 bit di larghezza. Generalmente questo riflette la dimensione dei registri interni della CPU usata per

quella architettura. Indica essenzialmente la possibilità di eseguire i calcoli a 64 bit.

Benché una CPU possa essere a 64 bit internamente, il suo bus dati esterno o il bus indirizzi possono avere

dimensioni differenti, maggiori o (raramente) minori, . In un sistema a 64 bit i puntatori sono anch'essi a 64 bit,

indipendentemente dalle dimensioni dell‟Address Bus (che potrà essere anche solo 36 bit con utilizzo di memoria virtuale).

8086

80386

Pentium 2

Pentium 4

Core 2 Duo

i3, i5, i7

Itanium

Architettura 16 bit

Architettura IA 32 a 32 bit (Intel Architecture-32 bit)

Architettura Intel P6

Architettura NetBurst sempre a 32 bit

Architettura EM64T Emulazione 64 bit x86 compatibile (2007)

Architettura Nehalem sempre basata su una Emulazione 64 bit x86 compatibile

Archtettura IA64 non compatibile con x86.

L‟ architettura EM64T (Extended Memory 64 Tecnology) detta anche IA32E, mediante registri aggiuntivi, è in

grado di eseguire SO a 64 bi, cioè a loro volta in grado di eseguire calcoli a 64 bit.

La nuova architettura IA64 (Architettura Intel - 64 bit), basata su registri interni a 64 bit, è al momento implementata

soltanto nei processori Itanium e Itanium 2 per i server e le workstation ad alte prestazioni, e non è compatibile con

la IA-32.

Package

Con l‟aumentare del numero dei piedini anche il package del microprocessore è cambiato negli anni.

dual in line package (DIP) con i piedini disposti soltanto sui due lati lunghi (integrati classici). Package

utilizzato nell‟8086 (40 piedini complessivi) e in alcune versione del 80286

PLCC (Plastic Leaded Chip Carrier) di forma pressoché quadrata con i piedini disposti sull‟intero perimetro,

con 2 / 3 file di piedini per ogni lato (a partire dal 80286 fino al Pentium)

La tecnologia PGA (Pin Grid Array), introdotta a partire dal Pentium II, utilizza pin molto più piccoli e

ravvicinati (come piccole “gocce”), disposti sull’intera area del processore con notevole aumento del numero.

La tecnologia LGA (Land Grid Array) introdotta nelle ultime versioni del Pentium 4 con Socket 775 col fine

dichiarato di migliorare la gestione dei segnali in alta frequenza, prevede che i pin di contatto non siano più sul

processore, ma direttamente sul socket. Molte critiche. Secondo i produttori di motherboard Intel avrebbe

introdotto questo nuovo metodo di connessione per far ricadere i problemi di rottura dei pin sui produttori di

schede madri piuttosto che sulle proprie spalle. Il dissipatore è collegato alla motherboard mediante quattro

punti di ancoraggio. Package tutt‟ora in uso negli ultimi processori Core 2 Duo.

pag 20

Sistemi - Classe Terza

robertomana.it

Il Personal Computer

Clock

Una caratteristica costante nell‟evoluzione dei processori è il costante aumento della frequenza di clock. Con

l‟aumento del clock, la memoria centrale ed i vari adapter devono essere in grado di operare alla stessa frequenza di

clock del processore, altrimenti l‟aumento risulta del tutto inutile. In 20 anni di vita del Personal Computer (1981 –

2001) si è passati da 4.77 MHz dell‟8086 a 3.8 GHz del Pentium 4, poi vi è stata una brusca frenata dovuta

all‟eccessiva produzione di calore prodotto dai segnali a frequenza elevata. La frequenza di 4 GHz corrisponde una

lunghezza d‟onda di 7,5 cm, dunque campo delle microonde.

Memoria Cache

Come cache di livello 1 si intende una eventuale memoria cache presente direttamente all‟interno della CPU che

serve per il prefetch di istruzioni e dati che potenzialmente potrebbero essere utilizzati a breve (utilizzata per la