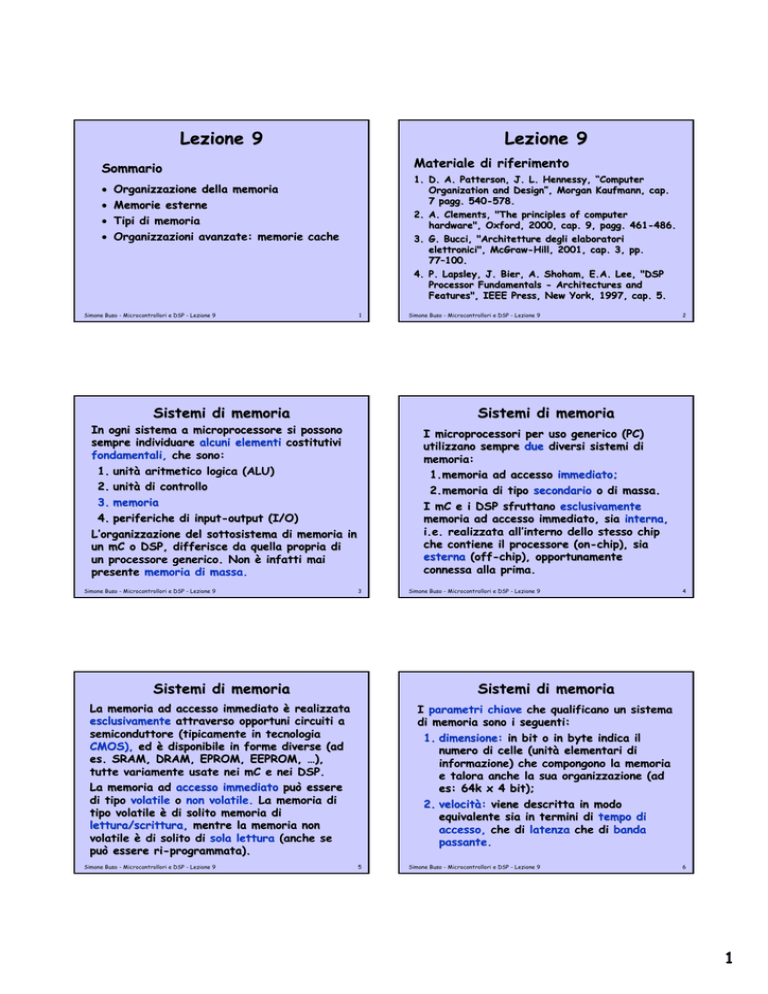

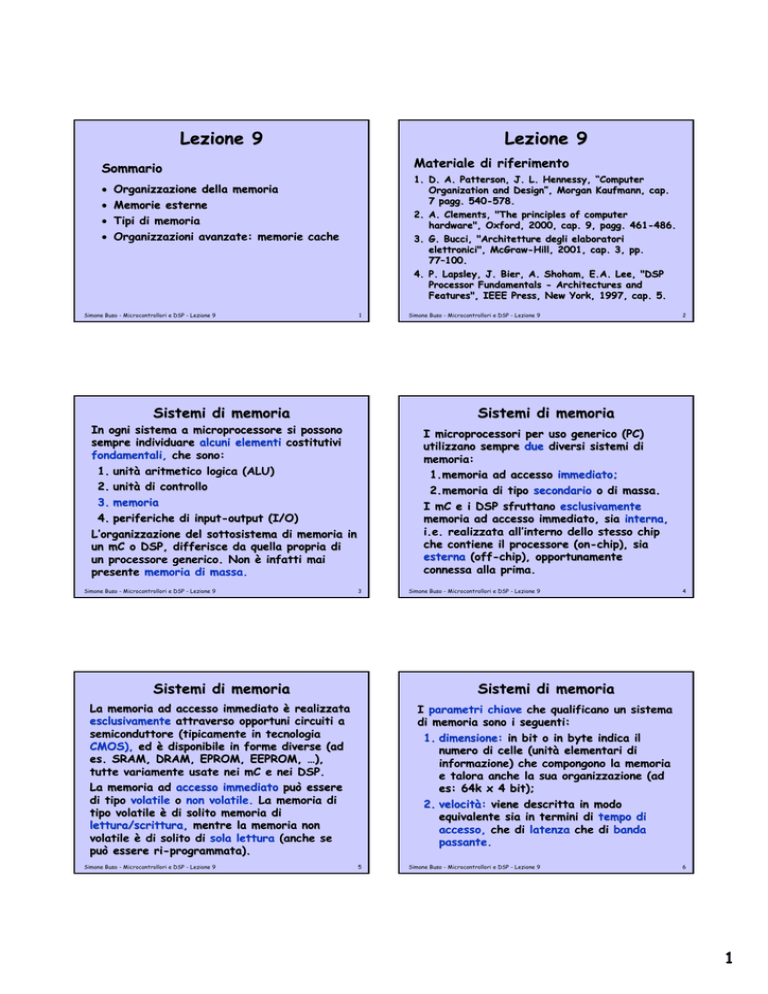

Lezione 9

Lezione 9

Materiale di riferimento

Sommario

•

•

•

•

1. D. A. Patterson, J. L. Hennessy, “Computer

Organization and Design”, Morgan Kaufmann, cap.

7 pagg. 540-578.

2. A. Clements, "The principles of computer

hardware", Oxford, 2000, cap. 9, pagg. 461-486.

3. G. Bucci, "Architetture degli elaboratori

elettronici", McGraw-Hill, 2001, cap. 3, pp.

77–100.

4. P. Lapsley, J. Bier, A. Shoham, E.A. Lee, "DSP

Processor Fundamentals - Architectures and

Features", IEEE Press, New York, 1997, cap. 5.

Organizzazione della memoria

Memorie esterne

Tipi di memoria

Organizzazioni avanzate: memorie cache

Simone Buso - Microcontrollori e DSP - Lezione 9

1

Sistemi di memoria

I microprocessori per uso generico (PC)

utilizzano sempre due diversi sistemi di

memoria:

1.memoria ad accesso immediato;

2.memoria di tipo secondario o di massa.

I mC e i DSP sfruttano esclusivamente

memoria ad accesso immediato, sia interna,

i.e. realizzata all’interno dello stesso chip

che contiene il processore (on-chip), sia

esterna (off-chip), opportunamente

connessa alla prima.

3

Simone Buso - Microcontrollori e DSP - Lezione 9

Sistemi di memoria

Sistemi di memoria

La memoria ad accesso immediato è realizzata

esclusivamente attraverso opportuni circuiti a

semiconduttore (tipicamente in tecnologia

CMOS), ed è disponibile in forme diverse (ad

es. SRAM, DRAM, EPROM, EEPROM, …),

tutte variamente usate nei mC e nei DSP.

La memoria ad accesso immediato può essere

di tipo volatile o non volatile. La memoria di

tipo volatile è di solito memoria di

lettura/scrittura, mentre la memoria non

volatile è di solito di sola lettura (anche se

può essere ri-programmata).

I parametri chiave che qualificano un sistema

di memoria sono i seguenti:

1. dimensione: in bit o in byte indica il

numero di celle (unità elementari di

informazione) che compongono la memoria

e talora anche la sua organizzazione (ad

es: 64k x 4 bit);

2. velocità: viene descritta in modo

equivalente sia in termini di tempo di

accesso, che di latenza che di banda

passante.

Simone Buso - Microcontrollori e DSP - Lezione 9

2

Sistemi di memoria

In ogni sistema a microprocessore si possono

sempre individuare alcuni elementi costitutivi

fondamentali, che sono:

1. unità aritmetico logica (ALU)

2. unità di controllo

3. memoria

4. periferiche di input-output (I/O)

L’organizzazione del sottosistema di memoria in

un mC o DSP, differisce da quella propria di

un processore generico. Non è infatti mai

presente memoria di massa.

Simone Buso - Microcontrollori e DSP - Lezione 9

Simone Buso - Microcontrollori e DSP - Lezione 9

5

Simone Buso - Microcontrollori e DSP - Lezione 9

4

6

1

Sistemi di memoria

Sistemi di memoria

2.a tempo di accesso: è il tempo (in ns di

solito) che intercorre tra la richiesta

del dato e il momento in cui esso è reso

disponibile (ciclo di read). Si compone di

due parti: tempo di decodifica o

localizzazione del dato e tempo di

trasferimento del dato.

2.b latenza: è il tempo che intercorre tra

l’inizio del ciclo di write e l’arrivo del

dato in memoria. I tempi di read e

write sono normalmente uguali.

2.c banda passante: è un’indicazione della

velocità alla quale i dati possono essere

trasferiti dal processore alla memoria e

viceversa. Si misura in bytes al secondo.

3. consumo di potenza: indica la potenza

elettrica media richiesta da un sistema

di memoria. In alcuni casi i costruttori

forniscono anche potenza assorbita in

stand-by (a riposo). Questi dati sono

fondamentali per il dimensionamento dell’

alimentazione di un sistema di memoria

esterno al chip.

Simone Buso - Microcontrollori e DSP - Lezione 9

7

Sistemi di memoria

Le caratteristiche di un sistema di memoria

ideale sono le seguenti:

1. alta velocità;

2. piccola occupazione di area di silicio;

3. basso consumo;

4. robustezza (rispetto a disturbi,

variazioni di temperatura, …);

5. basso costo.

Queste caratteristiche sono in larga misura

incompatibili tra loro, il che costringe a

scelte di compromesso.

9

Simone Buso - Microcontrollori e DSP - Lezione 9

Sistemi di memoria

Sistemi di memoria

Tutti i sistemi di memoria sono organizzati in

modo gerarchico. Il concetto di gerarchia di

memoria funziona bene in quanto le

informazioni che un processore scambia con la

memoria hanno sempre caratteristiche di:

1. località spaziale: i dati che sono

spazialmente prossimi all’interno della

memoria tendono ad essere usati a breve

distanza gli uni dagli altri;

2. località temporale: quando un dato viene

usato dal processore di solito viene anche

ri-usato a breve distanza.

Un sistema di memoria può quindi avere

eccellenti prestazioni combinando piccole

quantità di memoria molto veloce (quindi molto

costosa, a elevato consumo,…) e quantità via

via più grandi di memoria più lenta (e quindi

meno costosa, a minore consumo, …).

La memoria più pregiata in un processore è

rappresentata dai registri.

La memoria interna, che è di solito di tipo

SRAM (RAM statica), è molto più estesa (può

arrivare a molti kbyte) ma considerevolmente

più lenta (in termini relativi).

Simone Buso - Microcontrollori e DSP - Lezione 9

8

Sistemi di memoria

4. integrazione: dipende dalla tecnologia

usata nella realizzazione della memoria,

con particolare riferimento alla

definizione del processo fotolitografico

usato per la creazione delle maschere di

processo. La densità di memoria (numero

di bit per unità di volume) è direttamente

legata al livello di integrazione. Le prime

unità di memoria prodotte (anni ‘60)

avevano una capacità di appena 16 bit.

Attualmente esistono memorie su singolo

chip con capacità di dell’ordine di 1 Gbit.

Simone Buso - Microcontrollori e DSP - Lezione 9

Simone Buso - Microcontrollori e DSP - Lezione 9

11

Simone Buso - Microcontrollori e DSP - Lezione 9

10

12

2

Organizzazione della memoria

Organizzazione della memoria

La memoria on chip può essere organizzata

in modi diversi, al fine di massimizzare le

prestazioni del processore.

Nelle organizzazioni di tipo Harvard, la

memoria è suddivisa in banchi separati che

fanno uso di bus indipendenti per il

trasferimento dei dati o delle istruzioni.

Talvolta questa suddivisione in banchi viene

iterata in modo da permettere l’accesso

simultaneo ad una istruzione e a più di un

dato. Si parla di organizzazioni Harvard

modificate.

Simone Buso - Microcontrollori e DSP - Lezione 9

In alcuni casi i banchi di memoria sono 3,

uno per le istruzioni (P) e due per i dati (X,

Y). In questo modo, in un singolo ciclo del

processore è possibile leggere una istruzione

e fino a due operandi.

Queste organizzazioni avanzate non sono

normalmente estendibili alla memoria offchip in quanto non tutti i bus vengono resi

disponibili all’esterno. Al massimo, ne sono

resi disponibili due (dati e istruzioni). I

vantaggi di una organizzazioni a banchi

multipli vanno quindi parzialmente persi.

13

Organizzazione della memoria

16 bit

Bus indirizzi X

Bus indirizzi Y

Bus indirizzi P

MUX

Bus indirizzi

esterno

16 bit

Bus dati X

Bus dati Y

Bus dati P

Bus dati

esterno

Logica di

controllo bus

esterno

In alcuni casi, invece di ricorrere a banchi di

memoria multipli, si ricorre a memorie di tipo

dual port. Queste permettono due accessi

simultanei (duplicano tutta l’elettronica di

decodifica e di accesso alle celle) pur

mantenendo una organizzazione a singolo

banco (tipo Von Neumann).

Esistono anche memorie di tipo multiple port

dove il numero di accessi simultanei può

arrivare fino a 4.

Il limite principale di queste memorie è

rappresentato dal costo molto alto.

write/read

X/Y

memoria programmi

memoria dati

input

15

Organizzazione della memoria

CPU

Bus dati 1

Bus indirizzi 1

Bus dati 2

Bus indirizzi 2

Bus dati 3

Bus indirizzi 3

Memoria A

(dual port)

Memoria B

Simone Buso - Microcontrollori e DSP - Lezione 9

14

Organizzazione della memoria

Schema di

espansione della

memoria interna

su due bus

esterni a 16

bit.

Simone Buso - Microcontrollori e DSP - Lezione 9

Simone Buso - Microcontrollori e DSP - Lezione 9

Simone Buso - Microcontrollori e DSP - Lezione 9

16

Organizzazione della memoria

Organizzazione di tipo

composto: una memoria

dual port (banco A) e

una memoria standard

(banco B), permettono

l’accesso simultaneo a

una istruzione e due

dati.

Tipica nei DSP Motorola

della serie 561xx.

17

In altri casi, la possibilità di accessi multipli

è garantita dalla integrazione on-chip di

banchi di memoria molto veloci, capaci di

permettere più accessi in sequenza nello

stesso ciclo di clock.

Memoria di questa qualità può essere

ottenuta solo ricavandola all’interno del

processore stesso. Si tratta di una soluzione

efficace, ma estremamente costosa.

Come le soluzioni multi-port anche queste

soluzioni, dette multi-access, non sono

praticabili a livello di memoria esterna.

Simone Buso - Microcontrollori e DSP - Lezione 9

18

3

Organizzazione della memoria

Organizzazione della memoria

Nei mC e DSP il controllo della memoria

esterna è reso possibile da un opportuno

circuito, di solito interno al chip (non sono

richiesti controller aggiuntivi).

Le caratteristiche dei controllori integrati

nel chip sono però molto variabili. Alcuni

consentono solo di generare i segnali

essenziali (selezione, strobe, … ) per i bus

esterni, altri sono molto più flessibili

consentendo la gestione di wait-states e

memorie esterne del tipo “da PC” (es: DRAM

a pagine).

I cicli di attesa o wait-states sono necessari

ogni volta che la memoria esterna risulta più

lenta del processore.

Se il processore richiede N cicli di clock per

accedere alla memoria (spesso N = 1), la

memoria deve presentare un tempo di accesso

TA tale che:

Simone Buso - Microcontrollori e DSP - Lezione 9

TA<N⋅Tclk

Se questo non si verifica, è comunque

possibile rallentare il processore con un certo

numero Nw di cicli di attesa.

19

Simone Buso - Microcontrollori e DSP - Lezione 9

Organizzazione della memoria

Organizzazione della memoria

Questo comporta però una penalizzazione

nello sfruttamento del processore, quindi è da

considerarsi molto attentamente. La

condizione

Ad esempio, supponendo di dover espandere

la memoria interna di un mC con una memoria

il cui tempo di accesso sia di 30 ns, a fronte

di un periodo di clock di 25 ns (si assuma

N=1) si ha che la condizione:

TA<(N+Nw)⋅Tclk

TA<(N+Nw)⋅Tclk

può infatti essere soddisfatta anche con

Nw=0, per esempio ricorrendo ad un aumento

di Tclk.

Anche un solo wait-state può essere infatti

una penalizzazione relativa troppo pesante

(e.g. del 100% nel caso N=1).

Simone Buso - Microcontrollori e DSP - Lezione 9

può essere soddisfatta con Nw = 1. Questo

però rende il processore più lento del 100%

negli accessi alla memoria. Invece, riducendo

la frequenza di clock in modo che sia Tclk =

33 ns, la penalizzazione è solo del 32%.

21

Simone Buso - Microcontrollori e DSP - Lezione 9

Tipi di memoria

Tipi di memoria

Nei mC e nei DSP la memoria volatile di

lettura/scrittura viene sempre realizzata

come SRAM (Static Random Access Memory).

Il termine RAM designa però ogni tipo di

memoria in cui il tempo di accesso risulti

indipendente dalla posizione spaziale della

locazione (o cella) cui si accede.

Quindi anche le memorie di sola lettura

(ROM) sono delle RAM, contrariamente a

quanto generalmente si pensi. L’uso del

termine RAM come sinonimo di memoria di

lettura/scrittura è quindi errato.

L’uso di memoria SRAM come memoria interna

per i mC e i DSP è giustificato dalle seguenti

proprietà:

1) elevata velocità (tempo di accesso tipico

dell’ordine di 1 ns);

2) semplicità di gestione (non richiedono

refresh, diversamente dalle DRAM);

L’uso è invece limitato da due fattori:

1) consumo non trascurabile (alcuni mW per

kbyte);

2) complessità realizzativa (6 o 4 transistori

per cella) ⇒ minore densità, costo più alto.

Simone Buso - Microcontrollori e DSP - Lezione 9

20

23

Simone Buso - Microcontrollori e DSP - Lezione 9

22

24

4

Tipi di memoria

Tipi di memoria

VDD

La memoria SRAM veniva in passato usata

anche nel caso di espansioni di memoria

esterne. Attualmente si nota la tendenza a

utilizzare invece DRAM (Dynamic RAM),

essenzialmente per contenere i costi.

La necessità di refresh dei dati tipico delle

DRAM, costringe però, di norma, all’uso di

controllori esterni.

Anche le prestazioni ne risentono, in quanto il

semplice uso di wait-states non è sufficiente

a garantire l’interfacciamento al processore.

E’ necessario gestire wait-states dinamici.

Simone Buso - Microcontrollori e DSP - Lezione 9

D

D

W

25

Simone Buso - Microcontrollori e DSP - Lezione 9

Tipi di memoria

Tipi di memoria

B

Address bus

C

Chip Select

1 bus flottante

0

E

F

D

dati validi

tempo di accesso

Data bus

tempo di hold

Diagramma temporale di lettura per una SRAM

Simone Buso - Microcontrollori e DSP - Lezione 9

27

Simone Buso - Microcontrollori e DSP - Lezione 9

Tipi di memoria

Tipi di memoria

Le RAM dinamiche hanno un costo molto

inferiore a quelle statiche e una densità

almeno 4 volte superiore.

Richiedono però una significativa circuiteria di

controllo per gestire i cicli di refresh, che

viene realizzata di norma insieme alla memoria

stessa.

Hanno tempi di accesso maggiori di quelli delle

RAM statiche (dell’ordine delle decine di ns).

Infine, presentano un consumo di potenza ben

minore di quello delle SRAM, dell’ordine di

0.1 mW/kbyte.

Simone Buso - Microcontrollori e DSP - Lezione 9

28

Struttura generale di

una memoria DRAM.

bit lines

latch

address

RAS

word line

sense ampli

latch

CAS

bit line

word lines

indirizzo valido

row dec

1

0

tempo di ciclo

26

Le RAM statiche altro non sono che schiere di

registri a latch (ciascun latch fatto con 4 o 6

transitori). Le memorie RAM dinamiche

sfruttano invece l’immagazzinamento di carica

elettrica per la registrazione dei bit di

informazione.

La carica viene immagazzinata sotto l’ossido di

gate di una struttura MOS, modificando la

conducibilità elettrica del canale sottostante.

Purtroppo la carica intrappolata tende a

ricombinarsi (leakage), da cui la necessità di

refresh, con periodicità intorno al ms.

col dec

A

1

0

Cella di memoria

SRAM: la

scrittura avviene

portando la write

line W a livello

alto e attivando

la linea dati

desiderata.

L’ingombro della

cella è elevato

(10µm x 10µm).

output

buffer

Din

Dout

R/W

CE

29

Simone Buso - Microcontrollori e DSP - Lezione 9

30

5

Tipi di memoria

1

0

1

0

Address bus

indirizzo valido

riga

1

0

1

0

1 bus flottante

0

Address DRAM

colonna

A

1

0

RAS

C

CAS

E

B

D

Tipi di memoria

dati validi

Read/Write

Data bus

Diagramma temporale di lettura per una DRAM

Simone Buso - Microcontrollori e DSP - Lezione 9

31

Tipi di memoria

Simone Buso - Microcontrollori e DSP - Lezione 9

Memorie PROM

33

Simone Buso - Microcontrollori e DSP - Lezione 9

Memorie PROM

bit line

word line

fusibile

34

Memorie EPROM

Le memorie EPROM sono memorie di sola

lettura elettricamente ri-programmabili. La

cella tipica di una memoria EPROM ha

questa struttura:

Cella di memoria

PROM

La programmazione

avviene, in modo

irreversibile,

interrompendo il

fusibile.

VGG

VSS

Al momento della lettura il transistore rimarrà

spento: il circuito di lettura interpreta questo

stato come un valore logico 0.

Simone Buso - Microcontrollori e DSP - Lezione 9

32

Nelle memorie PROM l’informazione è

associata allo stato di un transistore (ON o

OFF, normalmente corrispondenti a 1 e 0).

Questo a sua volta dipende da un microfusibile, che collega un terminale del

transistore (ad es. il Drain) ad un potenziale

fisso.

La memoria è inizialmente piena di 1. La sua

programmazione consiste nell’interrompere per

fusione alcuni dei micro-fusibili (1 → 0).

Le memorie PROM sono estremamente veloci

(tempi di accesso dell’ordine di 1 ns).

Esistono diversi tipi di memoria ROM:

1) PROM (OTP): memoria di sola lettura che

può essere scritta una sola volta;

2) EPROM: memoria di sola lettura che può

essere cancellata con un dispositivo

apposito a luce UV.

3) EEPROM: memoria di sola lettura che può

essere scritta e cancellata elettricamente.

4) Flash EPROM: memoria di sola lettura che

può essere scritta e cancellata

elettricamente. Strutturalmente diversa

dalla precedente.

Simone Buso - Microcontrollori e DSP - Lezione 9

Nei mC e DSP è spesso integrata una piccola

quantità di memoria di sola lettura (ROM).

Questa può anche diventare la sola memoria

presente on-chip, quando si abbia a che fare

con prodotti di grandissima serie dove, ad

esempio, il programma, ritenuto definitivo,

viene memorizzato in modo non modificabile

durante la realizzazione del chip.

Comunque, anche in fase di sviluppo di una

applicazione, si ha spesso a che fare con

memoria di tipo ROM, anche se, di norma, di

tipo ri-programmabile e talvolta esterna.

gate

n+

gate flottante

ossido

p

n+

VDD

Substrato p35

Simone Buso - Microcontrollori e DSP - Lezione 9

36

6

Memorie EPROM

Memorie EPROM

La memoria EPROM può essere vista come una

memoria di tipo dinamico nella quale il periodo

di refresh è estremamente lungo (alcuni anni).

Questo effetto si ottiene immagazzinando

carica elettrica in un conduttore molto ben

isolato, quindi esposto a correnti di leakage

molto basse: il gate flottante.

La carica giunge sul gate flottante attraverso

l’ossido sottile che lo separa dal canale

quando gate e drain sono polarizzati a

tensione elevata (20 V). Il meccanismo fisico

viene detto hot electron injection.

L’iniezione di elettroni caldi è dovuta a

ionizzazione da impatto in prossimità del

drain. La componente verticale del campo

elettrico trascina all’interno del floating gate

parte della carica negativa generata.

La cancellazione di una EPROM avviene

esponendo il chip ad una sorgente di

radiazione UV, che provoca la ricombinazione

attraverso l’ossido della carica intrappolata.

Il chip è incapsulato in un involucro dotato di

finestra trasparente, appunto a questo scopo.

Simone Buso - Microcontrollori e DSP - Lezione 9

37

Simone Buso - Microcontrollori e DSP - Lezione 9

Memorie EPROM

Memorie EPROM

La presenza della carica negativa intrappolata

nel gate flottante provoca un innalzamento

della tensione di soglia del dispositivo. Al

momento della lettura, questo rimarrà spento.

Il circuito di lettura associa a questo stato il

valore logico 0.

ID

1

bit line

transistore di

selezione

word line

0

Ith

Vread

VG

Simone Buso - Microcontrollori e DSP - Lezione 9

39

Cella di memoria EPROM

La programmazione

avviene innalzando la

soglia del MOS con gate

flottante in modo che, al

momento della lettura

questo resti spento.

La carica intrappolata nel

gate flottante viene

rimossa esponendo il chip

a radiazione UV.

Simone Buso - Microcontrollori e DSP - Lezione 9

Memorie EEPROM

Memorie EEPROM

Si tratta di una memoria molto simile alla

EPROM, che può però essere cancellata solo

elettricamente. La sua cella tipica risulta così

strutturata:

L’estensione del gate flottante sopra al drain,

con riduzione al minimo dello spessore

dell’ossido (< 10 nm), permette agli elettroni

di raggiungerlo, in fase di programmazione,

per effetto tunnel (Fowler-Nordheim).

Dando una tensione negativa al gate gli

elettroni intrappolati possono ritornare al

drain, sempre per effetto tunnel. La

cancellazione della memoria è quindi

puramente elettrica.

Le EEPROM possono essere ri-scritte per un

numero grande, ma finito di volte (> 100000).

VGG

VSS

gate

n+

gate flottante

ossido

p

n

n+

VDD

Substrato pSimone Buso - Microcontrollori e DSP - Lezione 9

38

41

Simone Buso - Microcontrollori e DSP - Lezione 9

40

42

7

Memorie EEPROM

word line

Cella di memoria EEPROM

Il circuito equivalente per

una cella di memoria

EEPROM è identico a

quello della memoria

EPROM.

La carica viene però

estratta dal gate

flottante per tunneling

con tensione di gate < 0.

Simone Buso - Microcontrollori e DSP - Lezione 9

43

Anche le memorie FLASH sono cancellabili in

modo puramente elettrico, per effetto tunnel

(ossido sottile come le EEPROM) verso il

source.

Diversamente dalle EEPROM, il meccanismo

fisico di scrittura delle FLASH è l’iniezione di

elettroni caldi (come le EPROM, di cui

riprendono la struttura di cella, con un minore

spessore dell’ossido sotto il floating gate).

Possono essere riscritte anch’esse per un

numero finito di volte, che però è molto

grande (> 100000).

Simone Buso - Microcontrollori e DSP - Lezione 9

Memorie FLASH

Memorie FLASH

La cella tipica di una memoria FLASH è

molto simile a quella di una EEPROM. La

cancellazione avviene polarizzando

negativamente il gate e positivamente il

source.

gate flottante

gate

ossido

VGG

VSS

n+ n

p

n+

E’ molto comune incontrare mC e DSP con

memoria FLASH incorporata. La gestione della

memoria, che è piuttosto complessa, è in

questo caso a cura di un apposito controller

incorporato nel mC (o DSP) stesso.

Il problema principale delle FLASH è legato al

fatto che i tempi di lettura e scrittura sono

variabili in funzione di parametri come

temperatura, età, tolleranze di processo.

Quindi la gestione dei tempi di attesa deve

essere dinamica (di solito tramite polling di un

apposito registro di stato).

VDD

Substrato pSimone Buso - Microcontrollori e DSP - Lezione 9

45

Simone Buso - Microcontrollori e DSP - Lezione 9

Memorie FLASH

46

Memorie FLASH

Decoder di riga

Inoltre, la cancellazione può avvenire solo per

blocchi (richiede la polarizzazione ad una

tensione positiva del source) di alcuni kbyte.

Conviene quindi che i dati siano registrati

nella memoria evitando di utilizzare sempre lo

stesso blocco, per aumentare la vita utile

(ogni cancellazione implica uno stress per la

memoria).

I tempi di cancellazione e scrittura possono

essere abbastanza lunghi, dell’ordine di alcune

decine di secondi per un chip da 256 kbyte.

Simone Buso - Microcontrollori e DSP - Lezione 9

44

Source switch

bit line

transistore di

selezione

Memorie FLASH

Blocco di memoria

FLASH

Il circuito

equivalente di una

cella non prevede il

transistore di

selezione.

Decoder di colonna

Ogni blocco ha i terminali di source connessi

ad un deviatore che permette l’applicazione

della tensione di cancellazione.

47

Simone Buso - Microcontrollori e DSP - Lezione 9

48

8

Organizzazioni avanzate: cache

Memorie EPROM, EEPROM, FLASH

EPROM

Dimensioni (cella)

Programmazione

Cancellazione

Tempo di cancellazione

Cancellazione minima

Tempo di scrittura

Tempo di accesso

EEPROM

1

3.0

1.2

CHEI

FNT

CHEI

Luce UV

FNT

FNT

20 min.

5 ms

1 s

byte

blocco

5 ms

< 100 µs

10 ns

100 ns

chip

< 100 µs

100 ns

Le prestazioni di un sistema di memoria

possono essere aumentate in modo molto

significativo e a costi relativamente contenuti

sfruttando il concetto di memoria virtuale.

L’idea è far apparire la memoria molto più

veloce di quanto essa sia, facendo in modo

che il maggior numero possibile di accessi

(>95%) avvenga in una sua piccola frazione,

realizzata con una tecnologia ad alta velocità.

Ciò ha senso solo per sistemi di memoria di

dimensioni considerevoli e relativamente lenti,

tipici di dispositivi di alta gamma (DSP).

FLASH

Tabella comparativa per i diversi tipi di

memoria ri-programmabile

Simone Buso - Microcontrollori e DSP - Lezione 9

49

Simone Buso - Microcontrollori e DSP - Lezione 9

50

Organizzazioni avanzate: cache

Organizzazioni avanzate: cache

I sistemi cache consentono un miglioramento

di prestazioni in tutti e soli i casi in cui la

memoria non può essere letta in un solo ciclo

di clock del processore.

Questo non è comune nei mC, che hanno

frequenze di clock piuttosto basse. Lo sta

invece diventando nei DSP più potenti, che

cominciano ad operare a frequenze di clock di

centinaia di MHz.

Questi fanno spesso uso anche di memoria

DRAM, il che li rende molto simili ai

processori per uso generico (che usano cache).

Il livello di complessità delle cache usate nei

DSP è comunque inferiore (per ragioni di costo)

a quello dei processori per uso generico (PC).

Comunque l’uso della cache riguarda solo la

memoria istruzioni, mai la memoria dati. Ciò

risolve il problema della gestione delle

scritture in memoria, che complica

notevolmente i sistemi cache per uso generico.

Nei casi più semplici, la cache di un DSP è un

semplice buffer che immagazzina brevi

sequenze di istruzioni (repeat buffer).

Simone Buso - Microcontrollori e DSP - Lezione 9

51

Simone Buso - Microcontrollori e DSP - Lezione 9

Memoria cache

Memoria cache

Per memoria cache si intende un segmento del

sistema di memoria, caratterizzato da elevata

velocità, nel quale, attraverso strategie

opportune, si fa in modo di registrare le

informazioni più frequentemente richieste dal

processore, prelevandole dalla memoria più

lenta.

Il parametro principale in un sistema a cache

è il suo hit-ratio (h), che rappresenta la

frazione di accessi alla memoria, sul totale

che il processore esegue, che riescono a

trovare i dati richiesti nella cache stessa.

Simone Buso - Microcontrollori e DSP - Lezione 9

52

La tipica organizzazione di un sistema cache

prevede lo sdoppiamento dei bus dati e

indirizzi e un opportuno circuito di controllo.

bus dati

CPU

bus indirizzi

controller

cache

53

hit

Simone Buso - Microcontrollori e DSP - Lezione 9

memoria

principale

memoria

cache

54

9

Memoria cache

Memoria cache

E’ possibile stimare il vantaggio offerto dalla

cache nella riduzione del tempo di accesso

apparente alla memoria considerando alcuni

parametri:

tacc: tempo di accesso alla memoria principale;

tc: tempo di accesso alla memoria cache;

h: hit ratio.

La quantità che definisce l’efficienza del

sistema cache è lo speed-up ratio S:

S =

E’ interessante valutare l’andamento di S in

funzione di h:

S

5

4

3

2

1

0

0.5

1

h

tacc

h·tc + (1-h)·tacc

Simone Buso - Microcontrollori e DSP - Lezione 9

55

Il valore massimo

di S si ottiene per

h=1, ed è pari al

rapporto tra tacc e

tc (qui assunto

uguale a 5).

Valori tipici di h

sono dell’ordine di

0.95.

Simone Buso - Microcontrollori e DSP - Lezione 9

Memoria cache

Memoria cache

In realtà, il miglioramento nelle prestazioni di

un mC o DSP con cache dipende anche dalla

quota di tempo q spesa dal processore in

attività che non coinvolgono la memoria e dal

numero di cicli di clock richiesti per l’accesso

alla memoria. Una valutazione più accurata

dell’incremento di velocità consentito dalla

cache può quindi essere la seguente:

Sono possibili almeno 3 diverse organizzazioni

delle memorie cache:

1. a mappatura diretta;

2. associativa;

3. parzialmente associativa.

Il costo di queste soluzioni è crescente, e

dipende dalla complessità dell’algoritmo che

gestisce il caricamento dei dati nella cache e

gli eventi di “miss”, ossia il mancato

ritrovamento dei dati cercati nella cache. La

complessità è minima per le cache a

mappatura diretta.

Tciclo_avg = q·Tclk + (1-q)·(h·tc + (1-h)·tacc)

dove si valuta la durata media di un ciclo

macchina, Tciclo_avg, in relazione a Tclk.

Simone Buso - Microcontrollori e DSP - Lezione 9

57

Cache a mappatura diretta

TAG

B

Linea

Word

L

W

cache

linea k

Si assume di disporre di una memoria

principale divisibile in 2B blocchi, ciascuno

costituito da 2L linee di 2W parole.

La cache è suddivisa in due sezioni: la sezione

DATA e la sezione TAG. Nella prima vengono

copiate 2L linee di memoria, nella seconda

l’indirizzo del blocco di appartenenza di

ciascuna linea (detto appunto TAG).

La linea indirizzata dalla CPU viene cercata

nella cache. Simultaneamente viene anche

cercato il suo TAG. Viene quindi operato il

confronto tra i due TAG.

indirizzo

linea k

linea k

memoria

principale

linea k

blocco 2B

Simone Buso - Microcontrollori e DSP - Lezione 9

58

Cache a mappatura diretta

blocco j-1

blocco j

Simone Buso - Microcontrollori e DSP - Lezione 9

56

59

Simone Buso - Microcontrollori e DSP - Lezione 9

60

10

Cache a mappatura diretta

Cache a mappatura diretta

Se il blocco indirizzato dalla CPU ha lo stesso

TAG della linea trovata nella cache si ha un

hit, altrimenti un miss.

In caso di miss la linea cercata dalla CPU

viene copiata nella cache al posto di quella

inutile, che viene ricopiata nella memoria

principale o semplicemente cancellata.

Questa è l’organizzazione più semplice (meno

costosa) per una memoria cache. E’

inerentemente parallela e composta da due

banchi di memoria veloce e da un comparatore

digitale per il confronto dei TAG.

Simone Buso - Microcontrollori e DSP - Lezione 9

Linea

TAG

Word

TAG

COMP

indirizzo

DATA

hit

oe

sel

bus dati

61

Simone Buso - Microcontrollori e DSP - Lezione 9

Cache associative

Cache associative

Nelle cache associative, qualunque linea di

memoria può occupare qualunque posizione

nella cache.

Il TAG in questo caso è l’intero indirizzo della

linea cercata (composto da B+L bit).

La ricerca di una linea avviene confrontando

simultaneamente (in parallelo) tutti i TAG con

quello cercato (array di porte XOR).

Solo se il confronto è positivo e quindi solo

una volta concluso, la linea cercata può essere

inviata al bus dati (organizzazione seriale).

La gestione dei miss richiede una strategia

non ovvia di sostituzione delle linee. Si

possono usare soluzioni diverse, ossia:

1. si rimpiazza una linea a caso (RANDOM)

2. si rimpiazza la prima linea entrata (FIFO)

3. si rimpiazza la linea meno recentemente

usata (LRU);

La complessità (ed il costo) di questi algoritmi

è in ordine crescente.

In generale, le cache totalmente associative

sono molto costose da realizzare.

Simone Buso - Microcontrollori e DSP - Lezione 9

63

Cache parzialmente associative

64

Memoria cache

Le cache parzialmente associative sono

costituite da più cache a mappatura diretta

operate in parallelo.

Nel caso più semplice si usano due cache in

parallelo e si parla di cache associativa a 2

vie.

E’ quindi possibile avere due linee k

simultaneamente presenti nella cache.

Il confronto dei TAG avviene quindi ancora in

parallelo, ma coinvolge solo due istanze di

TAG (risultando più semplice rispetto alle

cache associative).

Simone Buso - Microcontrollori e DSP - Lezione 9

Simone Buso - Microcontrollori e DSP - Lezione 9

62

Il dimensionamento di un sistema cache è

molto complesso.

E’ necessario stabilire numerosi parametri,

tra i quali: la dimensione della cache, la

dimensione della linea e, nel caso di cache

associative (anche parzialmente), la

strategia di gestione dei miss.

L’impatto sulle prestazioni finali del

processore è comunque difficile da

prevedere sulla carta: spesso il

dimensionamento si basa su simulazioni del

sistema.

65

Simone Buso - Microcontrollori e DSP - Lezione 9

66

11