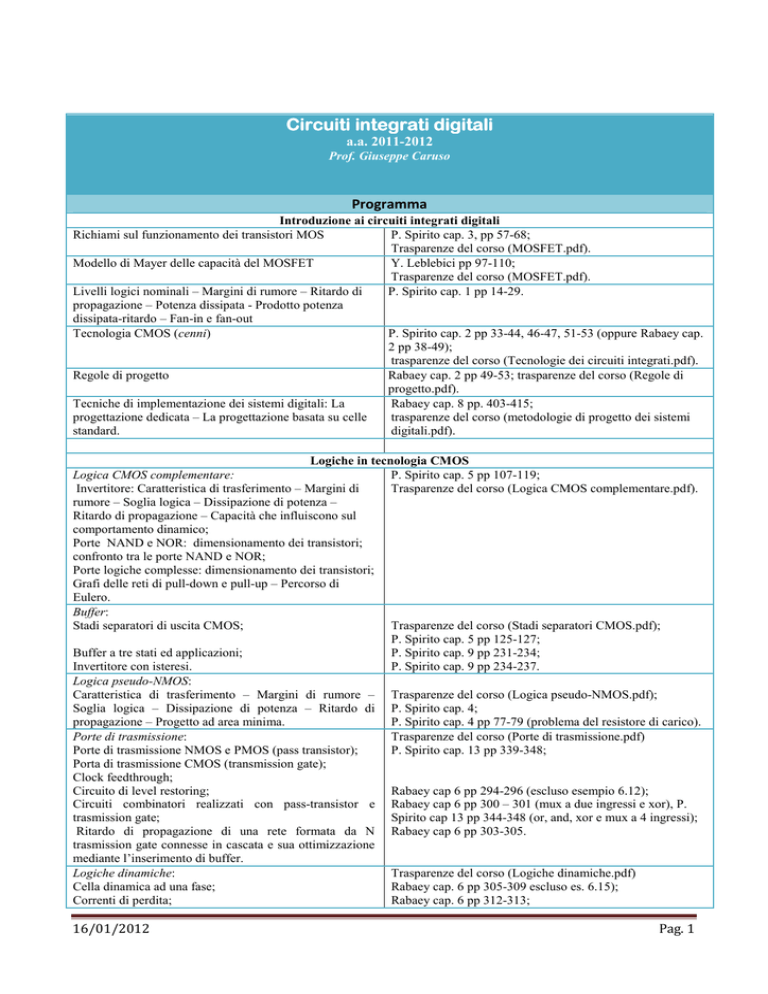

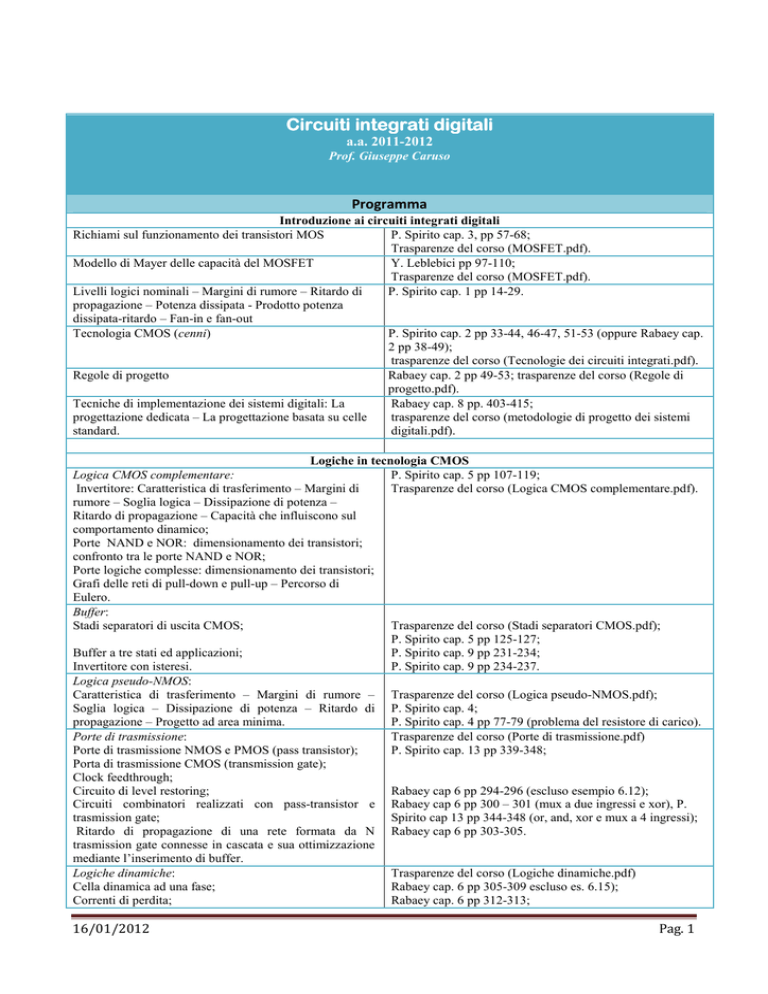

Circuiti integrati digitali

a.a. 2011-2012

Prof. Giuseppe Caruso

Programma

Introduzione ai circuiti integrati digitali

Richiami sul funzionamento dei transistori MOS

P. Spirito cap. 3, pp 57-68;

Trasparenze del corso (MOSFET.pdf).

Modello di Mayer delle capacità del MOSFET

Y. Leblebici pp 97-110;

Trasparenze del corso (MOSFET.pdf).

Livelli logici nominali – Margini di rumore – Ritardo di

P. Spirito cap. 1 pp 14-29.

propagazione – Potenza dissipata - Prodotto potenza

dissipata-ritardo – Fan-in e fan-out

Tecnologia CMOS (cenni)

P. Spirito cap. 2 pp 33-44, 46-47, 51-53 (oppure Rabaey cap.

2 pp 38-49);

trasparenze del corso (Tecnologie dei circuiti integrati.pdf).

Regole di progetto

Rabaey cap. 2 pp 49-53; trasparenze del corso (Regole di

progetto.pdf).

Tecniche di implementazione dei sistemi digitali: La

Rabaey cap. 8 pp. 403-415;

progettazione dedicata – La progettazione basata su celle

trasparenze del corso (metodologie di progetto dei sistemi

standard.

digitali.pdf).

Logiche in tecnologia CMOS

P. Spirito cap. 5 pp 107-119;

Logica CMOS complementare:

Invertitore: Caratteristica di trasferimento – Margini di

Trasparenze del corso (Logica CMOS complementare.pdf).

rumore – Soglia logica – Dissipazione di potenza –

Ritardo di propagazione – Capacità che influiscono sul

comportamento dinamico;

Porte NAND e NOR: dimensionamento dei transistori;

confronto tra le porte NAND e NOR;

Porte logiche complesse: dimensionamento dei transistori;

Grafi delle reti di pull-down e pull-up – Percorso di

Eulero.

Buffer:

Stadi separatori di uscita CMOS;

Trasparenze del corso (Stadi separatori CMOS.pdf);

P. Spirito cap. 5 pp 125-127;

Buffer a tre stati ed applicazioni;

P. Spirito cap. 9 pp 231-234;

Invertitore con isteresi.

P. Spirito cap. 9 pp 234-237.

Logica pseudo-NMOS:

Caratteristica di trasferimento – Margini di rumore – Trasparenze del corso (Logica pseudo-NMOS.pdf);

Soglia logica – Dissipazione di potenza – Ritardo di P. Spirito cap. 4;

propagazione – Progetto ad area minima.

P. Spirito cap. 4 pp 77-79 (problema del resistore di carico).

Porte di trasmissione:

Trasparenze del corso (Porte di trasmissione.pdf)

Porte di trasmissione NMOS e PMOS (pass transistor);

P. Spirito cap. 13 pp 339-348;

Porta di trasmissione CMOS (transmission gate);

Clock feedthrough;

Circuito di level restoring;

Rabaey cap 6 pp 294-296 (escluso esempio 6.12);

Circuiti combinatori realizzati con pass-transistor e Rabaey cap 6 pp 300 – 301 (mux a due ingressi e xor), P.

trasmission gate;

Spirito cap 13 pp 344-348 (or, and, xor e mux a 4 ingressi);

Ritardo di propagazione di una rete formata da N Rabaey cap 6 pp 303-305.

trasmission gate connesse in cascata e sua ottimizzazione

mediante l’inserimento di buffer.

Logiche dinamiche:

Trasparenze del corso (Logiche dinamiche.pdf)

Cella dinamica ad una fase;

Rabaey cap. 6 pp 305-309 escluso es. 6.15);

Correnti di perdita;

Rabaey cap. 6 pp 312-313;

16/01/2012

Pag. 1

Ripartizione della carica elettrica (charge sharing);

Porte dinamiche in cascata;

Logica domino;

Logica NORA (np-CMOS).

Rabaey cap. 6 pp 315-316;

Rabaey cap. 6 pp 319-320;

Rabaey cap. 6 pp 320-322;

Rabaey cap. 6 p 326.

Multivibratori

Trasparenze del corso (multivibratori.pdf)

Classificazione dei flip-flop – Flip-flop SR sincrono Rabaey 1a ediz. cap. 6 pp 333-353 (fotocopie),

realizzato con otto transistori – Latch pseudostatico – (*) Rabaey 2a ediz. pp 372-374;

Flip-flop master-slave di tipo D pseudostatico – Flip-flop

master-slave di tipo D dinamico – Flip-flop C2MOS (*);

Millman Grabel cap. 15 pp 728-734 (fotocopie).

Astabili e monostabili realizzati in logica FCMOS.

Circuiti aritmetici

Full-adder – Sommatore ripple-carry – Sommatore

Trasparenze del corso (circuiti aritmetici.pdf)

Manchester carry-chain – Sommatore carry-bypass –

Rabaey cap. 11 pp 599-617.

Sommatore linear carry-select – Sommatore square-root

carry-select.

Moltiplicatore array

Rabaey cap. 11 pp. 627-634 (escluso codifica di Booth)

Memorie

Trasparenze del corso (memorie.pdf)

Classificazione delle memorie;

Rabaey cap. 12 pp 671-674;

Architettura delle memorie;

Rabaey cap. 12 pp 674-678, P. Spirito cap. 14 p 378;

ROM a porte NOR e NAND statiche;

Rabaey cap. 12 pp 681-688;

ROM a porte NOR e NAND dinamiche;

Rabaey cap. 12 pp 694-696;

Rabaey cap. 12 pp 696-697;

Metodi di personalizzazione delle ROM;

EPROM, E2PROM e memorie Flash;

Rabaey cap. 12 pp 697-705 (P. Spirito cap. 9 pp 381-391);

SRAM: celle 4 T e 6T

Rabaey cap. 12 pp 708-716 (escluso dimensionamento delle

porte di trasmissione)

DRAM: cella dinamica 3T;

Rabaey cap. 12 pp 716-719;

Cella dinamica 1T e circuito di lettura

P. Spirito cap. 15 pp 411-417;

Rabaey cap. 12 pp 733-737;

Sense amplifier differenziale (cenni);

Decodificatori di riga;

Rabaey cap. 12 pp725-730 (escluso es. 12.12);

Decodificatori di colonna.

Rabaey cap. 12 pp 730-732.

Esercitazioni sperimentali

Uso del simulatore circuitale LTSpice IV - Generazione delle caratteristiche statiche di un MOSFET canale n utilizzando

il modello “EDU1um”.

Invertitore CMOS: rilievo della tensione di soglia e dei tempi di propagazione mediante simulazioni SPICE.

Progetto e simulazione di una porta complessa in logica CMOS complementare.

Layout di un invertitore CMOS

Simulazione post-layout di un invertitore CMOS

Layout di una porta NOR con fan-in 3 in logica CMOS complementare

Layout di una porta NAND con fan-in 3 in logica CMOS complementare

Layout di un multiplexer con quattro ingressi

Esercitazioni teoriche

Calcolo delle capacità parassite di un transistore MOS – Calcolo della tensione di soglia in presenza di effetto body –

Calcolo delle resistenze di un NMOS ed un PMOS.

Esercizi sulla logica CMOS complementare

Esercizi sulle porte di trasmissione

16/01/2012

Pag. 2