Elettronica dei Sistemi Digitali –

Algoritmi di channel routing per

standard cells; verifica progettuale

Valentino Liberali

Dipartimento di Tecnologie dell’Informazione

Università di Milano, 26013 Crema

e-mail: [email protected]

http://www.dti.unimi.it/˜liberali

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 1

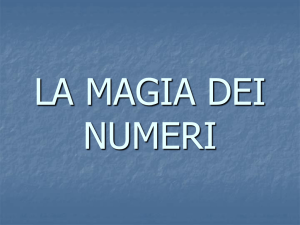

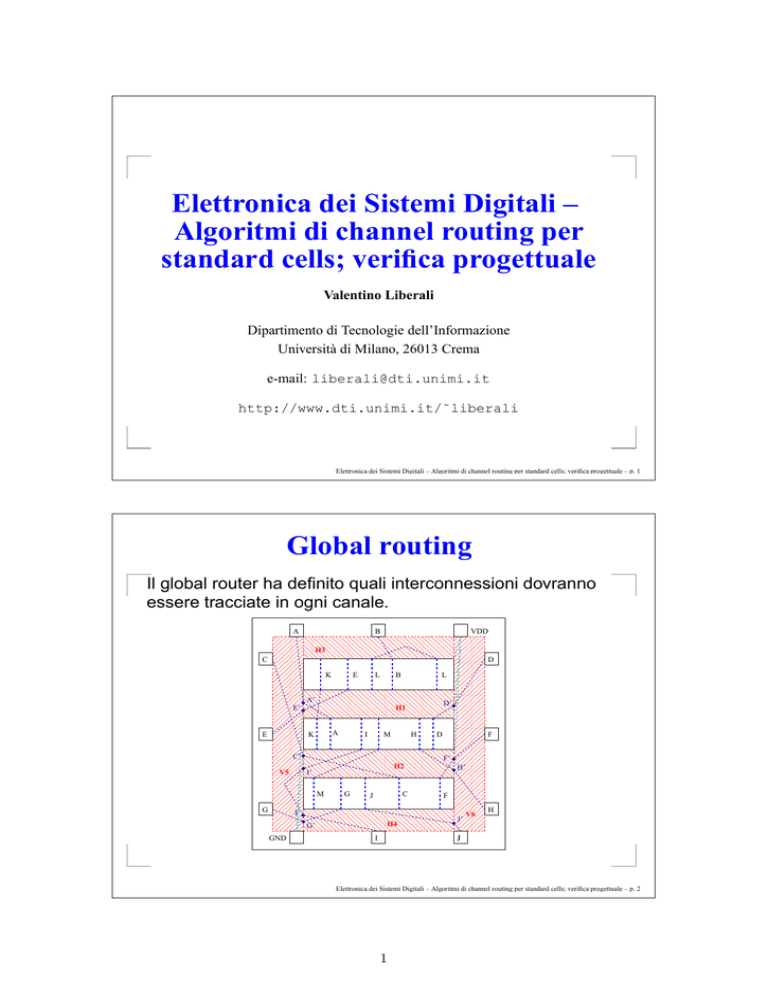

Global routing

Il global router ha definito quali interconnessioni dovranno

essere tracciate in ogni canale.

A

B

VDD

111111111111111111111

0000

0000

1111

00000000000000000

H3

0000

1111

0000D

1111

00000000000000000

11111111111111111

C 1111

000011111111111111111

0000

1111

000000000000000000000

1111

0000

1111

L 1111

0000 K E L B

1111

0000

0000

1111

0000

1111

000011111111111111111

1111

0000

1111

00000000000000000

A’

0000

1111

0000

D’ 1111

00000000000000000

H1

E’ 11111111111111111

0000

1111

0000

000000000000000001111

000011111111111111111

1111

0000

1111

00000000000000000

11111111111111111

0000

1111

0000F

1111

A

I

H

M

D 1111

E 1111

0000K

0000

0000

1111

0000

1111

0000

1111

0000

1111

00000000000000000

11111111111111111

C’

F’ 1111

000011111111111111111

1111

0000

00000000000000000

H2

H’

0000

1111

0000

1111

I’

V5

00000000000000000

11111111111111111

0000

1111

0000

000000000000000001111

000011111111111111111

1111

0000

1111

0000 M G J

1111

0000

C

F 1111

0000

1111

0000H

1111

00000000000000000

11111111111111111

G 1111

0000

0000

1111

I’ 11111111111111111

V6

00000000000000000

0000

1111

0000

1111

J’

00000000000000000

H4

G’

000011111111111111111

1111

0000

1111

00000000000000000

11111111111111111

0000

1111

0000

1111

I

GND

J

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 2

1

Channel routing (1)

Modello “classico” per un algoritmo di channel routing:

le interconnessioni sono lungo due direzioni ortogonali;

il passo di griglia è uniforme;

ci sono due livelli di interconnessione;

un livello di interconnessione è usato per i segmenti

orizzontali, l’altro per quelli verticali;

ogni interconnessione è realizzata con un solo

segmento orizzontale, più tanti segmenti verticali

quanti sono i terminali da connettere in direzione

verticale.

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 3

Channel routing (2)

0

x1

x2

x3

x4

C

B

A

D

A

B

A

C

x5

x6

x7

A

B

A

x8

x9 L

B

D

A

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 4

2

Vertical constraint graph (1/2)

Il posizionamento dei segmenti orizzontali viene

determinato con un algoritmo basato sul vertical constraint

graph:

è un grafo orientato (dall’alto verso il basso)

ogni nodo è un vertice del grafo

esiste un arco A → B se il nodo A si trova allineato

sopra al nodo B (cioè se una interconnessione

verticale lungo il canale provoca un cortocircuito tra A

e B)

se esiste l’arco A → B, allora il tratto orizzontale

dell’interconnessione A deve essere posizionato più in

alto del tratto orizzontale dell’interconnessione B

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 5

Vertical constraint graph (1/2)

se nel VCG esiste l’arco A → B, allora il tratto

orizzontale dell’interconnessione A deve essere

posizionato più in alto del tratto orizzontale

dell’interconnessione B

se è possibile un ordinamento dei nodi che rispetti tutti

i vincoli del grafo, questo è l’ordine (dall’alto verso il

basso) delle interconnessioni orizzontali)

altrimenti bisogna “spezzare” qualche

interconnessione

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 6

3

Channel routing (3)

0 x1

C

x2

x3

x4

B

A

D

x5

A

A

B

A

C

B

x6

x7

A

x8

x9 L

B

D

A

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 7

Bibliografia sul routing

Per un approfondimento sugli algoritmi di routing:

S.H. Gerez, Algorithms for VLSI Design Automation.

Wiley, Chichester, UK, 1998 – Capitolo 9.

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 8

4

Progettazione di circuiti elettronici

I circuiti “semplici” erano progettati risolvendo manualmente

le equazioni e realizzando prototipi su scheda con

componenti discreti (“bread-board” )

Questo approccio è diventato inadeguato, perché

il numero di componenti elettronici è elevato

le prestazioni dipendono dalle dimensioni di ciascun

componente

i componenti hanno un comportamento non ideale di

cui bisogna tenere conto

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 9

Verifica progettuale (1/2)

Gli elevati costi dei sistemi elettronici richiedono un buon

livello di confidenza sulla bontà del progetto. Nelle varie fasi

del progetto, prima della prototipazione, sono necessari

diversi passi di verifica.

PRIMA del disegno del layout (domini comportamentale e

strutturale):

verifica (simulazione) comportamentale, prima della

sintesi

verifica (simulazione) logica o circuitale, dopo la sintesi

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 10

5

Verifica progettuale (2/2)

DOPO il disegno del layout (domini fisico e strutturale):

verifica di correttezza delle geometrie (DRC = Design

Rule Chech), dopo il disegno del layout

verifica di correttezza dei collegamenti elettrici (ERC =

Electrical Rule Chech), dopo il disegno del layout

verifica di congruenza tra schema e layout (LVS =

Layout Vs. Schematic)

estrazione dei parassiti (“backannotation”) e

simulazione circuitale tenendo conto degli effetti

parassiti

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 11

Simulazione (1/6)

Si effettua una simulazione al calcolatore

per verificare il progetto prima di realizzarlo

per ottimizzare i parametri di progetto

per stimare gli effetti dovuti alle variazioni dei parametri

I primi programmi per la simulazione dei circuiti elettronici

risalgono agli anni 1960-1970:

SPICE (University of California at Berkeley)

ASTAP (IBM)

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 12

6

Simulazione (2/6)

L’aumento della complessità dei sistemi integrati ha

richiesto una modellizzazione a differenti livelli di

astrazione.

Simulazione del dispositivo: descrizione fisica del

singolo dispositivo, dimensioni geometriche e

parametri fisici dei materiali, grandezze fisiche in 3D

Simulazione circuitale: descrizione strutturale a livello

transistor, comportamento elettrico dei dispositivi,

tensione e corrente

Simulazione a macromodelli: “circuito equivalente”

semplificato, comportamento elettrico “ideale”,

tensione e corrente

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 13

Simulazione (3/6)

Simulazione “switch-level”: è un esempio di

simulazione a macromodelli, in cui i transistori

vengono modellizzati come interruttori ideali con

resistenza serie

Simulazione logica: rete di porte logiche (blocchi

unidirezionali), segnali logici (con o senza ritardo)

Simulazione RTL (register-transfer-level): rete digitale

sincrona, in cui si analizzano le transizioni di stato (la

logica combinatoria determina lo stato successivo in

base allo stato attuale e agli ingressi)

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 14

7

Simulazione (4/6)

Simulazione comportamentale: schema a blocchi,

descrizione (più o meno dettagliata) del

comportamento di ciascun blocco, “segnali” di vario

tipo (digitali o analogici)

Simulazione funzionale: schema a blocchi, descrizione

ad alto livello della funzione di ciascun blocco (le

primitive che descrivono i blocchi non hanno

necessariamente legami con il corrispondente

hardware)

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 15

Simulazione (5/6)

I sistemi digitali sono non lineari e tempo-varianti → la

simulazione deve essere effettuata nel dominio del tempo.

Le grandezze analogiche (tensione e corrente): richiedono

il calcolo di derivate e integrali.

Derivate: sono approssimate con il rapporto

incrementale

Integrali: sono calcolati con un’approssimazione a

gradino o a trapezio

I segnali digitali richiedono calcoli più semplici.

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 16

8

Simulazione (6/6)

Modellizzazione del tempo: per l’analisi numerica dei

sistemi, il tempo (grandezza continua) deve essere

suddiviso in intervalli discreti (“time step” ).

Simulazione analogica a time step costante

Simulazione analogica a time step variabile (con

calcolo dinamico del time step)

Simulazione digitale sincrona con clock (solo per

sistemi digitali temporizzati in cui si possono trascurare

i ritardi)

Simulazione digitale ad eventi (per circuiti asincroni o

pseudo-sincroni)

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 17

Simulazione analogica in transitorio (1)

Rapporto incrementale:

Forward Euler:

v(tk+1 ) − v(tk )

d

≈ v(tk )

tk+1 − tk

dt

Backward Euler:

v(tk+1 ) − v(tk )

d

≈ v(tk+1 )

tk+1 − tk

dt

Trapezoidale:

v(tk+1 ) − v(tk ) 1

≈

tk+1 − tk

2

d

d

v(tk+1 ) + v(tk )

dt

dt

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 18

9

Simulazione analogica in transitorio (2)

Esempio: circuito RC descritto da:

1

d

v(t) = − v(t)

dt

τ

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 19

Simulazione analogica in transitorio (2)

Approssimazione Forward Euler, con time step costante

∆t = tk+1 − tk :

1

1

(v(tk+1 ) − v(tk )) = − v(tk )

∆t

τ

e risolvendo rispetto a v(tk+1 ):

∆t

v(tk+1 ) = v(tk ) 1 −

τ

La soluzione oscilla per ∆t > τ

e diventa instabile per ∆t > 2τ !!!

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 20

10

Simulazione analogica in transitorio (3)

Approssimazione Backward Euler, con time step costante

∆t = tk+1 − tk :

1

1

(v(tk+1 ) − v(tk )) = − v(tk+1 )

∆t

τ

e risolvendo rispetto a v(tk+1 ):

v(tk+1 ) =

v(tk )

1 + ∆tτ

La soluzione è sempre stabile.

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 21

Simulazione analogica in transitorio (4)

Approssimazione trapezoidale:

d

2

d

v(tk+1 ) = (v(tk+1 ) − v(tk )) − v(tk )

dt

∆t

dt

da cui:

1

2

1

− v(tk+1 = (v(tk+1 ) − v(tk )) + v(tk )

τ

∆t

τ

e risolvendo rispetto a v(tk+1 ):

v(tk+1 ) = v(tk )

La soluzione oscilla per ∆t > 2τ

e tende a diventare instabile per

1 − 2∆tτ

1 + 2∆tτ

∆t

τ

→ ∞ !!!

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 22

11

Sistemi “stiff” (1/2)

Un sistema dinamico si definisce “stiff” (= rigido) quando è

descritto da equazioni differenziali in cui:

le costanti di tempo sono molto diverse tra loro

(parecchi ordini di grandezza);

le costanti di tempo sono dovute a parametri tra loro

non correlati.

In un sistema digitale, si alternano transitori brevi (le

commutazioni delle porte logiche) e intervalli relativamente

lunghi in cui le grandezze elettriche rimangono pressoché

costanti

→ tutti i sistemi digitali sono “stiff”.

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 23

Sistemi “stiff” (1/2)

Non è possibile risolvere numericamente un sistema stiff in

maniera accurata:

se il time step ∆t è grande, i transitori dovuti alle

costanti di tempo brevi vengono persi con

l’approssimazione Backward Euler (e la soluzione

oscilla con gli altri due metodi);

se il time step ∆t è piccolo, i transitori dovuti alle

costanti di tempo brevi vengono risolti correttamente,

ma i transitori dovuti alle costanti di tempo lente

richiedono tempi di simulazione proibitivi.

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 24

12

Modello “switch-level” del MOS

MOS

=

r

Dalla conduttanza

del MOS in triodo

= β (vGS −Vth ) si calcola la resistenza

g = ∂∂viD DS

vDS =0

equivalente:

r=

1

1

=

g β (vGS −Vth )

con

β=

µεox W

·

tox L

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 25

Simulazione “switch-level”

Nelle porte logiche si sostituisce ogni transistore MOS con

il suo modello “switch-level” e si considerano le capacità di

carico CL .

Il circuito digitale si riduce ad un circuito RC; la rete di

resistenze dipende dai segnali logici in ingresso

→ si può calcolare l’andamento (esponenziale) delle

tensioni nel tempo e i tempi di ritardo (attraversamento a

VDD /2), che dipendono dai segnali logici di ingresso.

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 26

13

Modello comportamentale (1)

Un sistema digitale:

opera su valori discreti

è un insieme di operazioni su valori

può essere descritto come un cammino di segnali

(= processo)

Un processo è definito tramite un insieme di istruzioni

(come un programma in C o in Pascal).

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 27

Modello comportamentale (2)

Descrizione di tipo “black-box”

Descrizione limitata alle relazioni tra ingresso e uscita

Nessun riferimento alla tecnologia utilizzata per la

realizzazione

Modello puramente matematico delle non idealità

(come i ritardi)

Esempio: y = a + b AFTER 2 ns;

Il ritardo è specificato dall’istruzione “AFTER”

La simulazione comportamentale considera il

ritardo, ma non c’è nessuna informazione relativa

alla causa che lo ha generato.

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 28

14

Modello comportamentale (3)

Un sistema suddiviso in sottosistemi è descritto mediante

un insieme di processi.

Poiché tutti i sottosistemi sono contemporaneamente attivi,

il modello deve prevedere l’esecuzione contemporanea dei

programmi (“processi concorrenti”).

La comunicazione tra processi è assicurata dai segnali

(percorsi unidirezionali dei dati).

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 29

Processo

È attivato da un evento (tempo oppure cambiamento di

valore di un segnale d’ingresso a cui il processo è

sensibile).

I segnali che attivano un processo sono contenuti nella

“sensitivity list” del processo.

È descritto con un insieme di istruzioni.

Le istruzioni vengono eseguite sequenzialmente.

Al termine il processo viene sospeso, cioè messo in

stato di attesa (“wait”) dell’evento successivo.

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 30

15

Bibliografia sulla simulazione circuitale

Per un approfondimento sulla simulazione circuitale nel

dominio del tempo:

K.S. Kundert, The Designer’s Guide to SPICE &

SPECTRE. Kluwer Academic Publishers, Boston, MA,

US, 1995 – Capitolo 4.

Per un approfondimento sulla simulazione digitale:

S.H. Gerez, Algorithms for VLSI Design Automation.

Wiley, Chichester, UK, 1998 – Capitolo 10.

Elettronica dei Sistemi Digitali – Algoritmi di channel routing per standard cells; verifica progettuale – p. 31

16