Livello logico digitale

bus e memorie

Principali tipi di memoria

• Memoria RAM

• Memorie ROM

RAM (Random Access Memory)

• SRAM (Static RAM)

– Basata su FF (4 o 6 transistor MOS)

– Veloce, costosa, bassa densità (bit/area): tempo accesso

0.5-5 ns, costo 4000-10000 per GB (nel 2004)

– usate nelle memori cache (direttamente su CPU)

• DRAM (Dynamic RAM)

– Immagazzinamento di cariche elettriche (~50pC)

– Meno veloce, meno costosa, alta densità (indirizzamento

via mux): tempo accesso 50 ns, costo 100 € per GB (nel

2004)

– Syncronous DRAM (SDRAM): Lettura sincrona ad un

segnale di clock (un solo fronte attivo)

RAM caratteristiche principali

Tanti aspetti specifici

• Formato di un modulo (altezza x ampiezza)

– 64K x 8 (64K indirizzi, 8 bit per indirizzo)

– 512 x 1

– 126K x 4

– 2K x 8

• Moduli preassemblati

– SIMM (72 pin), DIMM (168 pin), …

• Ex: PC-133 8M x 64 (8 chip, 32M x 8 bit)

• Tempo di ciclo

– Tempo che intercorre fra due operazioni (read o write)

su locazioni differenti

Esempi di organizzazione di RAM

Principali tipi di memorie ROM

• ROM (programmate in fabbrica)

• PROM (Programmabili una volta dall’utente)

• EPROM (Cancellabili mediante esposizione a raggi

ultravioletti e riprogrammabile)

• EEPROM (Cancellabili elettricamente e riscrivibili)

– Tecnologia FLASH (cancellazione per blocchi)

Riepilogo principali tecnologie

memorie

Esempio di SRAM

Ingresso

Indirizzi

Uscita

Controllo

SDRAM

SIMM

DDR

Bus nei calcolatori

Collegano vari sottosistemi. Caratteristiche:

• Dimensioni e caratteristiche fisiche

– Connettori, distanza fra connettori, lunghezza massima

• Ampiezza dati: 16,32, 64 bit

• Numero massimo di dispositivi collegabili

• Protocollo del bus

– Sincrono vs Asincrono

– Master/Slave

– Arbitraggio

• Banda di trasmissione (MB/sec)

– Valore teorico, effettivo,…

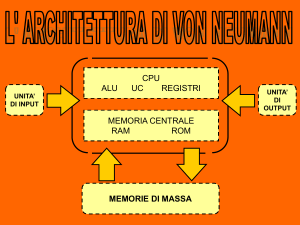

Architetture con un solo bus

•

DEC PDP-8 (1965)

•

Interconnessione a bus, molto flessibile

•

Architettura incentrata sull’I/O

•

Possibilità di connettere qualsiasi periferica

•

Prodotto in oltre 50.000 esemplari

Un singolo BUS?

I sistemi con un singolo BUS (bus di backplane) sono

economici, ma non sono in grado di offrire elevate

prestazioni

– Molte unità sullo stesso BUS: Contesa per l’accesso

– Velocità di traferimento diverse

– Numero di unità che possono essere connesse

• Si utilizzano quindi diversi tipi di BUS

– Bus per il collegamento Processore-Memoria

– Bus per collegamento dispositivi periferici (non è molto

veloce perché non serve)

• Le connessioni fra tipi diversi di bus sono

effettuate da appositi circuiti adattatori

Esempi di bus

Esempio di bus in un PC

BUS ADAPTER

MEMORIA

SCHEDA GRAFICA

DISCHI

BUS ADAPTER

Pentium 4

Utilizzo del BUS

Bisogna stabilire un insieme di regole (protocollo) per

regolamentare la transazioni

• Uno dei due partner di una transazione è il master

del bus, mentre l’altro slave (padrone, schiavo)

• Il master inizia una transazione mentre lo slave

esegue gli ordini forniti dal master

– Ex: la CPU (master) ordina la lettura di un dato dalla

memoria (slave)

– Lo stesso dispositivo può svolgere il ruolo sia di master

che di slave (in cicli differenti)

– Se più di un dispositivo collegato al bus può svolgere

funzione di master, allora è richiesto un ulteriore

protocollo (arbitraggio del bus) per assegnare in modo

esclusivo la funzione di master

Utilizzo del BUS: terminologia

• Un segnale S di controllo può determinare l’azione

che controlla quando esso vale 1 oppure 0

• Si dice che il segnale è asserito quando assume il

valore che provoca l’azione, altrimenti il segnale è

negato

• Se il segnale provoca l’azione quando il valore è 1

(asserito alto), il segnale si denota con S,

altrimenti con S (notazione Intel #S)

• Ciclo di bus è l’insieme di attività che coinvolgono il

bus atte a svolgere un’operazione (ex. Ciclo di

lettura, ciclo di scrittura,..)

Bus Sincrono

Esempio di ciclo di lettura

Bus Asincrono

Esempio di ciclo di lettura

Arbitraggio del BUS

daisy chain

• Server per decidere il master della nuova transazione

• Deve risolvere i conflitti nel caso di richieste

contemporanee da parte di più dispositivi per diventare

master

• Una tecnica comune è daisy chain

• Non è fair: il dispositivo i è avvantaggiato rispetto ad i+1