Richiami sulla struttura dei sistemi di calcolo

n Gestione delle Interruzioni

n Gestione della comunicazione fra processore e

dispositivi periferici

n Gerarchia di memoria

n Protezione.

2.1

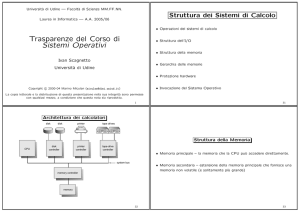

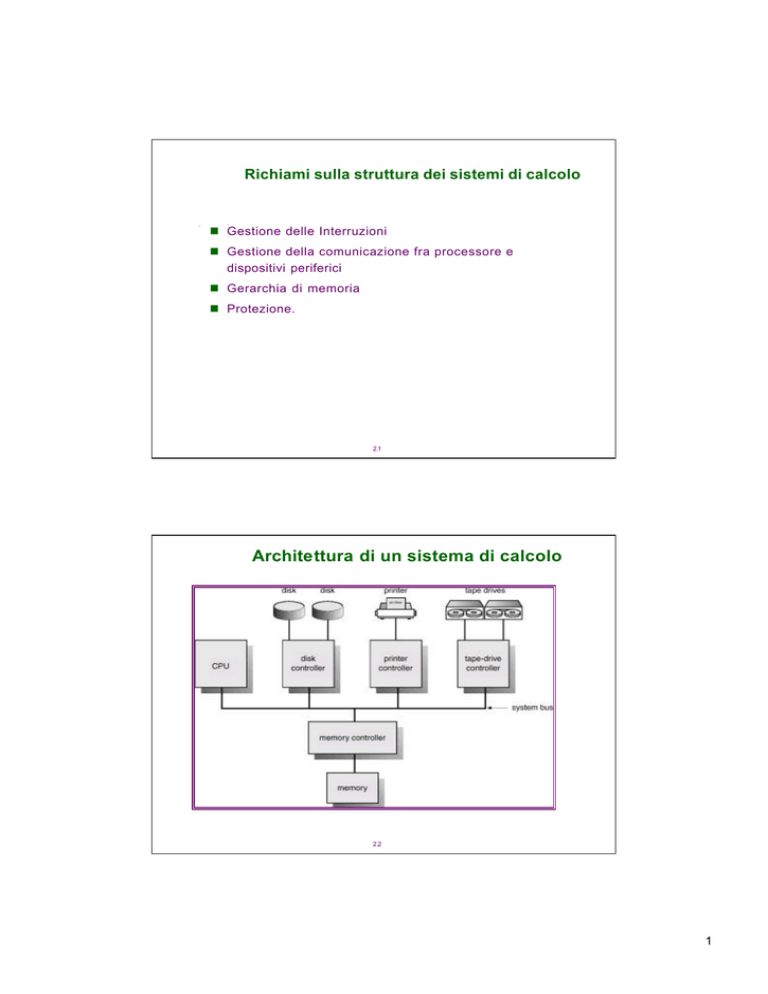

Architettura di un sistema di calcolo

2.2

1

Funzionamento di un Sistema di calcolo

n

I dispositivi di I/O e la CPU possono operare c o n c o r r e n t e m e n t e.

n

Ad ogni dispositivo di I/O corrisponde il proprio controllore.

n

Ogni controllore ha il suo b u f f e r locale .

n

CPU sposta i dati dalla/ verso la memoria centrale verso/ da i

buffer locali

n

L’operazione di I/O ha luogo tra il dispositivo ed il buffer locale

del controller.

n

Il controller informa la CPU del termine di una opera zione

g e n e r a n d o u n interrupt (di fine I/O).

2.3

Interrupt

n Una definizione:

F Un meccanismo che consente l’interruzione del normale

ciclo di esecuzione della CPU

n Introdotti per aumentare l’efficienza di un sistema di

calcolo

n Permettono al S.O. di intervenire durante

l’esecuzione di un processo utente, per gestire le

risorse di un calcolatore (CPU, Memoria, I/O)

n Possono essere sia hardware che software

n Possono essere ritardati (mascherati) se la CPU sta

svolgendo compiti non interrompibili

2.4

2

Classi di Interrupt

n Interrupt Hardware

F Eventi hardware asincroni, non causati dal programma in

esecuzione

4 Dispositivi di I/O (es. fine I/O)

4 Clock (scadenza quanto di tempo)

n Interrupt Software (Trap)

F Causato dal programma

4 Eventi eccezionali, quali divisione per zero, errori di

indirizzamento

4 Richiesta di servizi al S.O. (system call)

2.5

Gestione degli Interrupt

(panoramica)

n Un segnale di interrupt request viene inviato alla CPU

n La CPU:

hardware

F Interrompe l’elaborazione corrente

F Salta all’indirizzo di una locazione di memoria contenente la

routine di gestione dell’interrupt (ISR o interrupt h a n d l e r)

n L’ISR:

F gestisce l’interrupt in modo opportuno

software

F Restituisce il controllo al processo interrotto (o ad altro

processo)

n La CPU riprende l’esecuzione del processo interrotto

2.6

3

Gestione degli Interrupt

(dettagli)

1. Un segnale di interrupt request viene inviato alla CPU

2. La CPU termina l’esecuzione dell’istruzione corrente

3. La CPU verifica la presenza di un segnale di Interrupt e in

caso affermativo invia una conferma (ACK) al device che ha

generato l’interrupt

2.7

Gestione degli Interrupt

(dettagli)

4. La CPU salva sullo stack le informazioni necessarie

a riprendere l’elaborazione interrotta (Registri critici:

PC e Registro di Stato)

5. Selezione dell’interrupt handler appropriato tramite il

vettore di interrupt

6. Caricamento del PC con l’indirizzo iniziale

dell’handler

-

(in pratica si salta all’ISR e il ciclo f e t c h -e x e c u t e viene

ripreso)

TUTTE LE OPERAZIONI FIN QUI SONO SVOLTE IN

HARDWARE

2.8

4

Gestione degli Interrupt

(dettagli)

7. Salvataggio dello stato del processore sullo stack

(informazioni critiche non salvate via hardware)

8. Gestione dell’interrupt

n

Lettura delle informazioni di controllo provenienti dal

dispositivo ed eventuale nuova comunicazione col

dispositivo

9. Ripristino dello stato del processore

n

È l’operazione inversa alla 7

10. Ritorno del controllo al processo in esecuzione

n

Ripristino del PC e del registro di stato salvati sullo stack.

2.9

2.10

5

Sistemi Operativi Interrupt-Driven

n I sistemi operativi sono guidati dalle interruzioni

n Gran parte del nucleo viene eseguito come interrupt

handler

n Gli interrupt (sia hardware che software) guidano

l’avvicendamento dei processi

2.11

Interruzioni multiple

n Un interrupt può avvenire

durante la gestione di un

altro interrupt

n Due possibili approcci:

F Disabilitazione degli interrupt

(riabilitazione prima di

riprendere il processo

interrotto)

F Interrupt annidati (interrupt a

priorità maggiore possono

interrompere la ISR)

2.12

6

Tecniche di comunicazione di I/O

n Tre modalità di comunicazione tra CPU e

dispositivi di I/O:

F I/O programmato

F I/O interrupt driven

F DMA (Direct Memory Access)

2.13

I/O programmato (tecnica obsoleta)

n

La CPU esegue un’istruzione di I/O eseguendo un apposito

programma di I/O.

n

Il programma di I/O (es. input dati):

F Prepara l’operazione di I/O scrivendo sui registri del controller del

dispositivo

n

Il dispositivo esegue l’azione richiesta e al termine scrive sui

registri del controller i risultati (buffer e stato)

n

La CPU attende (busy waiting ) il completamento dell’operazione

testando periodicamente il contenuto di appositi registri di stat o

n

Infine la CPU sposta i dati di input dal buffer del controller alla

memoria centrale

LA CPU DEVE ATTENDERE IL COMPLETAMENTO

DELL’OPERAZIONE

2.14

7

I/O interrupt- driven

n

La CPU esegue un’istruzione di I/O lanciando un apposito

programma di I/O.

n

Il programma di I/O (es. input dati):

F Prepara l’operazione di I/O scrivendo sui registri del controller del

dispositivo

n

Il sistema operativo sospende l’esecuzione del processo che ha

eseguito l’operazione di input ed esegue un altro processo

n

Il dispositivo esegue l’azione richiesta, al termine scrive sul

buffer del controller il risultato e segnala il termine

dell’operazione attraverso interrupt.

n

Al ricevimento dell’interrupt, la CPU copia i dati dal buffer del

controller alla memoria centrale.

2.15

DMA- Direct Memory Access

n

Nei precedenti approcci, il processore spreca parte del suo

tempo a trasferire dati dal controller alla memoria e la velocit à

del trasferimento dipende dalla velocità con cui il processore

può gestire il servizio.

n

Con un modulo di DMA, il controller del dispositivo trasferisce

blocchi di dati dal buffer direttamente in memoria centrale,

senza l’intervento della CPU

n

il S.O. invia al DMA:

F Richiesta di lettura o scrittura

F Indirizzo del dispositivo di I/O

F Locazione di partenza della memoria da cui leggere o scrivere

F Numero di parole da leggere o scrivere

n

Completato il trasferimento, il DMA invia un interrupt alla CPU

2.16

8

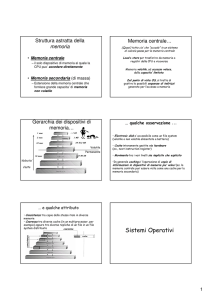

Struttura della Memoria

n Memoria Centrale – insieme ai registri è il solo

spazio di memorizzazione che può essere acceduto

direttamente dalla CPU.

n Memoria Secondaria – estensione della memoria

centrale con una vasta e non volatile capacità di

memorizzazione.

n Dischi Magnetici – dischi ricoperti di materiale

magnetico

F Superficie del disco divisa in tracce e settori

F Il disk controller costituisce l’interfaccia fra disco e

computer.

2.17

Disco a testine mobili

2.18

9

Gerarchia di memoria

n

Le memorie possono essere organizzate in una gerarchia.

F Velocità

F Costo

F Volatilità

n

C a c h i n g – copiare informazioni in memorie pù veloci ; la

memoria centrale può essere vista come una cache della

memoria secondaria.

2.19

Gerarchia della memoria

2.20

10

Caching

n

Uso di memorie veloci per conservare dati acceduti di recente

n

Un concetto che si applica a vari livelli:

F Cache della memoria centrale

F Cache del disco in memoria

F Cache di file system distribuiti in file system locali

n

Richiede una politica di gestione della cache.

F Dimensione della cache e dei blocchi

F Una funzione di mapping del blocco nella cash

F Algoritmi di sostituzione.

n

Problema della coerenza.

2.21

Migrazione di A dal Disco ai Registri

2.22

11

2.23

Architetture di Protezione

n

In un ambiente con risorse condivise sono necessari

meccanismi di protezione per evitare

F Interferenze fra processi utente

F Interferenze fra processi utente e processi del S.O.

n

D u a l-Mode Operation

n

I/O Protection

n

Memory Protection

n

CPU Protection

2.24

12

Dual-Mode Operation

n

Impedisce ad un programma scorretto di causare danni ad un

altro programma.

n

È necessario un supporto h a r d w a r e per distinguere fra due

modalità di funzinamento .

1. User mode – esecuzione per conto di un processo utente.

2. Monitor mode ( a n c h e kernel mode o system mode) – esecuzione

per conto del S.O.

2.25

Dual-Mode Operation (Cont.)

n

Un bit di modo deve essere aggiunto nello status register per

indicare il modo corrente : monitor (0) o user (1).

n

Se si verifica un interrupt o una eccezione, l’hardware passa in

m o d o monitor.

Interrupt/fault

monitor

user

set user mode

Istruzioni privilegiate sono quelle eseguibili solo in modo m o n i t o r.

2.26

13

I/O Protection

n

Tutte le istruzioni di I/O devono essere considerate privilegiate.

n

Il S.O. dovrà offrire primitive e servizi per eseguire operazioni di

I/O.

n

L’obiettivo è evitare che un programma utente possa ad

esempio corrompere il file system, accedendo ad un dispositivo

di memoria secondaria

n

È necessario garantire che nessun processo utente possa

avere il controllo del sistema nella modalità monitor (occorre ad

esempio evitare che un programma utente riesca a modificare il

vettore delle interruzioni, inserendovi un indirizzo che fa

riferimento a proprio codice)

2.27

Uso di una System Call per eseguire I/O

2.28

14

Protezione di memoria

n

È necessaria la protezione di memoria per

F

il vettore delle interruzioni e per le ISR.

F Lo spazio dei processi utente e del sistema operativo.

n

Per proteggere la memoria è possibile aggiungere all’hardware

due registri che determinano l’intervallo degli indirizzi validi

accessibili da un processo

F Base register – per il più piccolo indirizzo di memoria fisica

accessibile.

F Limit register – contiene l’ampiezza dell’intervallo

n

La memoria esterna a questo intervallo è inaccessibile.

2.29

Uso dei registri Base e Limite

2.30

15

Hardware per la protezione degli indirizzi

(MMU)

2.31

Hardware Protection

n

Durante l’esecuzione in modo monitor, il S.O. ha libero accesso

sia alla memoria monitor che a quella degli utenti

n

Le istruzioni di caricamento dei registri base e limite devono

essere istruzioni privilegiate.

2.32

16

Protezione della CPU

n

T i m e r – per interrompere il processore dopo uno specifico

intervallo di tempo per garantire che il S.O. mantenga il contro llo

del sistema.

F Timer è decrementato ad ogni tick di clock.

F Quando il timer arriva al valore 0, si verifica un interrupt.

n

Timer è usato per realizzare il time sharing , calcolare l’ora

corrente

n

Anche l’struzione Load -timer è privileg i a t a.

2.33

Network Structure

n

Local Area Networks (LAN)

n

Wide Area Networks (WAN)

2.34

17

Local Area Network Structure

2.35

Wide Area Network Structure

2.36

18