SECONDA UNIVERSITA’ DEGLI STUDI DI NAPOLI

Facoltà di Ingegneria

Corso di Laurea Magistrale in Ingegneria Informatica

Corso di Elettronica dei Sistemi Digitali

Progetto

Progettazione di un IC per la risoluzione di disequazioni di primo grado in

Pipeline

Docente

Prof. Aldo Minardo

Studenti

Andrea Cirillo Matr. A18000046

Pasquale Cirillo Matr. A18000045

Anno Accademico 2011-2012

1

Introduzione

Nel corso del progetto ci si è rivolti alla progettazione e alla simulazione di un IC per la

risoluzione di disequazioni di primo grado sfruttando la tecnica della Pipeline. L’obiettivo

è quello di ottenere, dati tre ingressi A, B, C su quattro bit, il risultato delle disequazioni:

A+B ≤C

A+B ≥C

(1)

Il layout del sistema è stato realizzato seguendo un approccio modulare per cui, di

seguito, si procederà illustrando singolarmente il funzionamento dei diversi dispositivi

per passare, infine, alla composizione degli stessi. In particolare, i dispositivi sono stati

progettati in tecnologia CMOS da 0.25µm con 6 livelli di metal con l’ausilio del software

Microwind 3.1 : esso consente al progettista di simulare e progettare un circuito integrato

a livello fisico.

La struttura in Pipeline è stata progettata con la tecnologia a Pass-Transistor seguendo lo schema generale riportato in Figura 1, dove la logica combinatoria contrassegnata

con F corrisponde ad un Adder Ripple Carry a 4 bit realizzato sfruttando la tecnologia

a Gate di Trasmissione, mentre quella contrassegnata con G corrisponde ad un Comparatore a 4 bit. In realtà, alla struttura basilare illustrata sono state apportate alcune

modifiche che verrano descritte nei paragrafi successivi.

2

Invertitore

La Figura 2(a) mostra lo schema circuitale di un invertitore CMOS statico. Il suo funzionamento è facilmente intuibile a partire dal modello a interruttore del transistor MOS

mostrato in Figura 2(b). In prima approssimazione, il transistor può essere rappresentato da un interruttore con una resistenza infinita quando è aperto (|VGS | < |VT |) e una

resistenza finita quando è chiuso (|VGS | > |VT |). Ciò si traduce nella seguente interpretazione dell’invertitore: se Vin ha un valore logico alto uguale a VDD , il transistore NMOS è

attivo e il transistor PMOS è interdetto. In queste condizioni esiste un cammino diretto

tra l’uscita e la massa del circuito; a regime l’uscita assume una tensione Vout = 0 V .

Figura 1: Pipeline

1

(a)

(b)

Figura 2: Invertitore statico CMOS: (a) Schema circuitale, (b) rappresentazione

dell’invertitore mediante interruttori.

Figura 3: Analisi della risposta dinamica dell’invertitore CMOS

Invece, quando la tensione di ingresso ha un valore logico basso (0 V ) i transistor NMOS

e PMOS sono rispettivamente spento e acceso; l’uscita è connessa attraverso il PMOS

all’alimentazione e assume un valore di tensione Vout = VDD . Questa porta realizza la

funzione logica NOT.

Utilizzando lo stesso modello ad interruttore del transistore MOS, è possibile fare

un’analisi qualitativa del comportamento dinamico della porta logica (Figura 3). La risposta dinamica è dominata principalmente dalla capacità di uscita CL , che è composta

dalle capacità parassite dei drain dei due transistor, dalla capacità delle piste di interconnessione e dalle capacità di ingresso delle porte logiche che l’invertitore sta pilotando.

Supponendo che la tensione di ingresso commuti istantaneamente e considerando una

transizione basso-alto, avremo che la risposta dinamica è determinata dal tempo che la

porta impiega a caricare la capacità CL attraverso la resistenza Rp . La dipendenza della

resistenza e della capacità dalla tensione Vout può essere eliminata rimpiazzando entrambi gli elementi con i loro corrispondenti lineari. In questo modo, il calcolo del tempo di

propagazione del circuito si semplifica in un’analisi di una rete RC. Per cui:

2

Figura 4: Invertitore statico CMOS: Layout realizzato in Microwind 3.1

tpHL = 0, 69Reqn CL

tpLH = 0, 69Reqp CL

tpHL + tpLH

Reqn + Reqp

= 0, 69CL

tp =

2

2

(2)

Per avere che i tempi di propagazione di una porta logica siano gli stessi per entrambe

le commutazioni del segnale di ingresso è necessario realizzare i due transistor in modo

che abbiano approssimativamente lo stesso valore di resistenza equivalente. A tale scopo,

la realizzazione riportata nella Figura 4 mostra un invertitore composto da un transistor

1.5

PMOS con un rapporto di aspetto W

L = 0.25 e da un transistor NMOS con un rapporto

0.5

di aspetto W

L = 0.25 . Considerando un carico sul nodo di uscita di 0.01 pF , la porta

logica mostra un tempo di ritardo per le due transizioni molto simili tra loro (Figura 5):

per la transizione basso-alto la porta mostra un ritardo di circa 22 ps, mentre per la

transizione alto-basso il ritardo è di circa 34 ps.

3

Figura 5: Invertitore statico CMOS: test del dispositivo

3

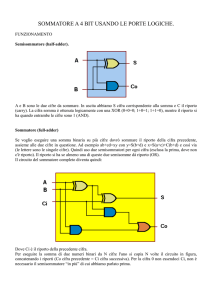

Il sommatore

L’addizione è l’operazione aritmetica usata più frequentemente e costituisce spesso il fattore limitante per la velocità computazionale di un sistema. Dunque, l’ottimizzazione

accurata dei blocchi sommatori riveste il ruolo di massima importanza nel progetto di

un’unità di elaborazione. L’ottimizzazione procede sia a livello logico sia a livello circuitale. A livello logico è possibile riorganizzare la struttura delle varie relazioni booleane

in modo da ottenere un circuito più piccolo e veloce. D’altra parte, a livello di circuito

è possibile manipolare le dimensioni dei transistor e la topologia delle porte logiche in

modo tale da ottimizzare ciascun elemento che compone il sommatore. La Tabella 1

mostra la tabella di verità di un sommatore binario (full adder ): A e B sono i due bit

da sommare, Ci è il riporto in ingresso, S rappresenta il risultato della somma e Co è

il riporto di uscita risultante dalla somma A + B. Le relazioni booleane che legano gli

ingressi A, B e Ci alle uscite S e Co si possono esprimere come segue:

S = A ⊕ B ⊕ Ci

= AB̄ C̄i + ĀB C̄i + ĀB̄Ci + ABCi

(3)

Co = AB + BCi + ACi

Molto spesso è utile dal punto di vista dell’implementazione definire i segnali di

somma e riporto di uscita S e Co in funzione di tre segnali intermedi: G (Generate),

D (Delete) e P (Propagate). G = 1 significa che il riporto in uscita (Co ) è generato,

cioè posto a 1 indipendentemente dal valore di Ci ; D = 1 rappresenta il caso opposto in

4

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

Ci

0

1

0

1

0

1

0

1

S

0

1

1

0

1

0

0

1

Co

0

0

0

1

0

1

1

1

Tabella 1: Tabella di verità di un sommatore binario

cui Co è posto a 0 indipendentemente da Ci ; P = 1 significa che il valore del riporto di

uscita sarà uguale a quello di ingresso, cioè che il valore del riporto all’ingresso Ci viene

propagato verso l’uscita Co . Dando uno sguardo alla tabella di verità, possiamo ricavare

le espressioni booleane che legano i segnali G, D e P ai valori logici dei bit in ingresso A

e B:

G = AB

D = ĀB̄

(4)

P =A⊕B

Da queste relazioni si possono ricavare S e Co in funzione di P e G:

Co (G, P ) = G + P Ci

S (G, P ) = P ⊕ Ci

(5)

Notiamo che i segnali G e P sono funzione dei solo ingressi A e B, ma non del

segnale di riporto Ci . Un sommatore a N bit può essere realizzato nel modo più semplice

mettendo in cascata N blocchi full-adder, connettendo l’uscita del riporto del blocco

k − 1 (Co,k−1 ) al riporto di ingresso del blocco k (Ci,k ), con k = 1, 2, . . . N − 1, mentre il

riporto di ingresso del primo blocco (Ci,0 ) è costante a 0. Questo tipo di architettura è

detta sommatore ripple-carry (sommatore a propagazione del riporto), poichè il riporto

si propaga da uno stadio all’altro. Il tempo di ritardo del circuito dipende dal numero di

stadi logici che devono essere attraversati che a sua volta è funzione della configurazione

dei bit in ingresso: per alcune coppie di ingressi non vi è alcuna propagazione, mentre per

altre coppie il riporto deve propagarsi attraverso l’intera catena dal bit meno significativo

al bit più significativo. Il tempo di propagazione di questa struttura è definito come il

ritardo calcolato in condizioni di caso peggiore tra tutte le combinazioni possibili degli

ingressi. Nel sommatore ripple-carry, il caso peggiore si verifica quando il riporto è

generato nel bit meno significativo e propagato lungo tutta la catena fino al bit più

5

Figura 6: Circuito a gate di trasmissione che realizza un full-adder con tempi di

propagazione simili per il segnale di somma e riporto

significativo. Il valore del riporto è usato, infine, nell’ultimo stadio per calcolare il bit

più significativo della somma. Il tempo di ritardo è, quindi, proporzionale al numero N

di bit delle parole di ingresso ed è approssimativamente dato da:

tadd = (N − 1) tC + tS

(6)

dove tC è il tempo per il calcolo del riporto (carry) da Ci a Co e tS quello della somma

da Ci a S.

Un full-adder può essere costruito usando multiplexer e porte logiche XOR. Sebbene

questo approccio non sia facilmente praticabile in logica complementare, diventa abbastanza semplice usando la logica a gate di trasmissione. Una possibile implementazione di

un full-adder basato su questa tecnica è mostrato nella Figura 6 e impiega 24 transistor.

Questa realizzazione fa uso dei segnali intermedi di propagazione (P ) e generazione (G)

del riporto presentati nelle (4). Il segnale P , che deriva dall’operazione XOR tra A e B, è

usato per selezionare il valore diretto o negato del riporto in ingresso come nuovo valore

della somma. Inoltre, in funzione del valore del segnale P , il riporto in uscita assume

il valore del riporto in ingresso oppure quello dell’ingresso A (in alternativa è possibile

usare anche B). Una delle caratteristiche più interessanti di questo tipo di realizzazione

è la simmetria tra i tempi di propagazione della somma e del riporto in uscita.

Seguendo un approccio modulare verranno di seguito illustrate le singole parti che

compongono il sommatore partendo dall’elemento principale, il gate di trasmissione, e

procedendo gradualmente alla composizione delle funzioni più complesse utilizzate per il

calcolo della somma e del riporto.

6

Figura 7: Gate di trasmissione CMOS

3.1

Il gate di trasmissione

Il gate di trasmissione fonda il suo funzionamento sulle proprietà complementari dei

transistor NMOS e PMOS: i dispositivi NMOS trasmettono bene gli 0 logici e male gli

1; invece, i dispositivi PMOS trasmettono correttamente gli 1 logici, ma male gli 0. Il

gate di trasmissione sintetizza in un unico componente le proprietà migliori di entrambi

i transistor, combinando un NMOS e un PMOS in parallelo come mostrato in Figura 7.

I segnali di controllo, C e C̄, sono complementari: quando C = 1, entrambi i MOSFET

sono attivi, permettendo al segnale di passare attraverso il gate di trasmissione, per cui:

A = B se C = 1

Al contrario, con C = 0, entrambi i transistor sono interdetti e il gate di trasmissione

diventa un circuito aperto tra A e B.

Consideriamo il processo di carica del nodo B da 0 a VDD attraverso il gate di

trasmissione in figura Figura 8a. Il nodo A è mantenuto a VDD e il gate di trasmissione è

abilitato (C = 1 e C̄ = 0). Se fosse presente il solo dispositivo NMOS, il nodo B sarebbe

caricato solamente fino a VDD − VT n , cioè fino al punto in cui il transistor NMOS si

spegne. Tuttavia, essendo presente e acceso anche il transistor PMOS (VGSp ≈ −VDD ),

l’uscita viene caricata fino a VDD . La Figura 8b mostra il caso opposto, cioè, la scarica

del nodo B da VDD a 0. Il transistor PMOS da solo può scaricare il nodo B fino a

|VT p | e poi si spegne. Il transistor NMOS in parallelo rimane comunque acceso (essendo

VGSn = VDD ) e consente di scaricare completamente il nodo B a massa. Sebbene il gate

di trasmissione richieda due transistor e due segnali di controllo, esso consente di ottenere

l’escursione logica massima tra massa e alimentazione.

Nella Figura 9 è riportato il layout del gate di trasmissione

implementato utilizzando

1.5

un transistor PMOS con un rapporto di aspetto W

=

e

un transistor NMOS con

L

0.25

W

0.5

un rapporto di aspetto L = 0.25 . In queste condizioni, considerando una capacità

di carico sul nodo di uscita pari a 0.01 pF , il tempo di propagazione per la transizione

basso-alto è di circa 42 ps, mentre per la transizione alto-basso è di circa 46 ps. Dalla

Figura 10 è possibile notare come sulla commutazione basso-alto del segnale di controllo

Clock collegato al Gate del transistor NMOS (e la corrispondente transizione alto-basso

del segnale ∼Clock collegato al terminale Gate del PMOS) l’impulso sull’ingresso DataIn

si propaghi sull’uscita DataOut.

7

Figura 8: Il gate di trasmissione fornisce un’escursione logica completa tra massa e

alimentazione

Figura 9: Layout del Gate di trasmissione realizzato in Microwind 3.1

3.2

Generazione del segnale di propagazione del riporto

Come descritto precedentemente, il segnale di propagazione del riporto è calcolato applicando l’operazione XOR tra il segnale A e B. La funzione logica XOR è facilmente

implementabile con la tecnica a gate di trasmissione: la soluzione della Figura 6 fa uso

di due gate di tramissione e due invertitori in modo da ottenere, oltre al segnale di

propagazione P , anche il segnale P̄ . Analizziamo, ora, il comportamento del circuito

considerando l’ingresso A = 1 (Ā = 0) e B = 0: il gate di trasmissione in alto risulta

essere spento, per cui la tensione al nodo P è imposta dal primo invertitore pilotato

dall’ingresso B (il segnale Ā collega il transistor NMOS a massa) ed è uguale al valore

logico 1; il gate di trasmissione in basso è acceso, mentre il secondo invertitore risulta

essere spento, per cui il nodo P̄ verrà scaricato dal gate di trasmissione e portato al

valore logico 0. Quando l’ingresso B commuta da 0 a 1, l’invertitore in alto pone il nodo

P al valore logico 0 e il gate di trasmissione in basso traferisce il valore logico alto sul

nodo P̄ . Analogamente, le stesse analisi possono essere effettuate quando l’ingresso A è

8

Figura 10: Gate di trasmissione: test del dispositivo

uguale a 0.

Nella Figura 11 è riportato il layout del circuito implementato, mentre nella Figura 12

è riportato un test che illustra le analisi effettuate precedentemente.

3.3

Circuiti per la somma e per il riporto

L’implementazione di un sommatore con gate di trasmissione prevede tempi di propagazione simili per il segnale di somma e riporto perchè entrambi i segnali attraversano al

massimo un gate di trasmissiione e un invertitore. Il segnale P , che deriva dall’operazione

XOR tra A e B, è usato per selezionare il valore diretto o negato del riporto in ingresso

come nuovo valore dell’uscita della somma. Inoltre, in funzione del valore del segnale P ,

il riporto di uscita assume il valore del riporto in ingresso oppure quello dell’ingresso A.

Il circuito che realizza tutto ciò, è formato da due multiplexer che realizzano le funzioni

logiche seguenti:

S̄ = (Ci · P + C̄i · P̄ )

C̄o = (C̄i · P + Ā · P̄ )

Nelle seguenti condizioni di funzionamento:

9

(7)

Figura 11: Layout del circuito per la generazione del segnale di propagazione realizzato

in Microwind 3.1

• Ci = 1 (C̄i = 0)

• A = 1 (Ā = 0)

si ha: quando P = 1 il secondo gate di trasmissione (dall’alto nella Figura 6) è acceso

e lascia passare il valore in ingresso Ci che, dopo essere stato negato dall’invertitore in

cascata, rappresenterà il nuovo valore della somma; il nuovo valore per il riporto di uscita

sarà ottenuto negando il valore di C̄i in ingresso al quarto gate di trasmissione (in basso

nella Figura 6). Nella Figura 13 è riportato il layout del circuito che calcola la somma

e il riporto di uscita, mentre nella Figura 14 è mostrato un test che sintetizza l’analisi

appena effettuata.

3.4

Full-Adder a 1 bit

Il Full-Adder per la somma di due operandi ad un bit viene ottenuto dalla composizione

dei circuiti analizzati nelle sezioni precedenti. La Figura 15 mostra il layout del dispositivo, mentre la Figura 16 mostra un test realizzato inserendo in ingresso al sommatore

dei segnali variabili per A, B e Cin : in particolare la simulazione mette in evidenza come

i tempi di propagazione per il segnale di somma e di riporto uscente siano molto simili

tra loro. Da come è possibile notare il dispositivo risponde seguendo il comportamento

atteso: quando i tre ingressi hanno un valore logico alto, sia il segnale di somma che di

riporto uscente assumono un valore logico alto, mentre quando i tre ingressi sono bassi

sia la somma che il segnale di riporto uscente commutano da 1 a 0.

10

Figura 12: Circuito per la generazione del segnale P: test del dispositivo

3.5

Full-Adder a 4 bit

Un sommatore a 4 bit ripple carry (propagazione del riporto) è ottenibile collegando

quattro full-adder a 1 bit in cascata connettendo l’uscita del riporto del blocco k − 1

(Co,k−1 ) al riporto di ingresso del blocco k (Ci,k ). Come espresso dalla (6), il tempo di

ritardo è proporzionale al numero N di bit delle parole di ingresso. Precedentemente

è stato accennato che nel sommatore ripple carry il caso peggiore si verifica quando il

riporto è generato nel bit meno significativo e propagato lungo tutta la catena fino al bit

più significativo e, inoltre, il valore del riporto è usato nell’ultimo stadio per calcolare il

bit più significativo della somma. Un’analisi sul caso peggiore richiede, quindi, che sia

A0 che B0 siano uguali a 1, dato che il riporto in ingresso alla catena è sempre 0, mentre

tutti gli altri stadi devono essere in stato di propagazione (uno e solo uno tra Ai e Bi deve

essere 1). Infine, è necessario che l’uscita della somma del bit più significativo esegua

una transizione: se assumiamo che il valore iniziale di SN −1 sia 0, esso dovrà commutare

a 1. A tale scopo è sufficiente che AN −1 e BN −1 siano entrambi alti o bassi in modo da

ottenere un valore alto della somma quando arriva un riporto con valore 1. Ad esempio,

i seguenti valori di A e B danno luogo al caso peggiore per la somma di due numeri interi

a 4 bit (LSB a destra):

A: 0001

B: 0111

Per misurare il tempo di propagazione al caso peggiore è sufficiente mantenere costanti

tutti i bit ad eccezione di A0 che può essere fatto commutare tra 0 e 1. La Figura 17

11

Figura 13: Layout del circuito per il calcolo di somma e riporto di uscita realizzato in

Microwind 3.1

mostra il sommatore implementato, mentre nella Figura 18 è riportata la simulazione

effettuata per il calcolo del ritardo di propagazione. Considerando i valori di A e B

riportati nella (3.5) si ha:

tpLH = 944 ps

tpHL = 588 ps

tpLH + tpHL

tp =

= 766 ps

2

(8)

Il ritardo di propagazione calcolato sarà utilizzato, in seguito, per calcolare la frequenza

massima a cui il circuito completo in pipeline dovrà lavorare.

4

Il comparatore

Un comparatore digitale o comparatore magnitudo (magnitude comparator) è un dispositivo elettronico che, presi due numeri in ingresso in formato binario, determina se un

numero è maggiore, minore o uguale all’altro. Il comparatore è uno dei dispositivi più

usati nelle central processing units (CPU) e nei microcontrollori. Un comparatore è mostrato nella Figura 19 e si può notare come l’uscita sia usualmente una variabile di tre

bit.

12

Figura 14: Circuito per il calcolo di somma e riporto di uscita: test del dispositivo

Ai

0

0

1

1

Bi

0

1

0

1

Ei

1

0

0

1

Tabella 2: Tabella di verità per la funzione di uguaglianza

Per semplicità, la progettazione del dispositivo, come per il sommatore, è avvenuta

seguendo un approccio modulare, ossia è stato prima progettato un comparatore ad 1

bit implementando la sola funzione di uguaglianza e poi, usando tale modulo come componente base, è stato progettato il comparatore di nibble (4 bit) completo. Le funzioni

G (A > B), E (A = B) e L (A < B) sono state ricavate utilizzando le corrispondenti tabelle di verità e mediante la semplificazione delle funzioni logiche tramite la tecnica delle

Mappe di Karnaugh. Viene riportato di seguito un esempio per il calcolo delle funzioni

G, E e L basato su un comparatore a 2 bit (l’estensione al caso generale risulta essere

alquanto semplice). Un comparatore a 2 bit è un dispositivo con quattro ingressi (A0 , B0 ,

A1 , B1 ). Si può affermare che A = B solo se tutti i bit della stessa posizione sono uguali,

quindi Ai = Bi per ogni i. Dalla Tabella 2 si ricava, quindi, che E0 = A0 B0 + Ā0 B̄0 e che

E1 = A1 B1 + Ā1 B̄1 . Dire che A = B implica che Ai = B

i (Ei = 1), ossia

che E0 E1 = 1.

Per cui si ricava che la funzione E = A0 B0 + Ā0 B̄0 A1 B1 + Ā1 B̄1 . Notando che

13

Figura 15: Layout del Full-Adder a 1 bit realizzato in Microwind 3.1

Ai

0

0

1

1

Bi

0

1

0

1

Gi

0

0

1

0

Tabella 3: Tabella di verità per la funzione di maggioranza

(x ⊕ y) = (xy + x̄ȳ) e notando che:

Ei = Ai Bi + Āi B̄i ⇒

⇒ Ai B̄i + Āi Bi =

= Āi + Bi Ai + B̄i =

= Āi Ai + Āi B̄i + Ai Bi + Bi B̄i =

= Ai Bi + Āi B̄i

si può pensare di implementare la funzione Ei con: la cascata di due invertitori che

negano gli ingressi Ai e Bi ; due porte AND a due ingressi che effettuano la AND logica

Ai B̄i e B̄i Ai ; una NOR a due ingressi che effettua la somma Ai B̄i + Ai B̄i .

A > B se A1 > B1 o A1 = B1 AN D (A0 > B0 ). Dalla Tabella 3 si può ricavare la

funzione logica G come:

14

Figura 16: Full-Adder a 1 bit: test del dispositivo

G = A1 B̄1 + E1 A0 B̄0 = Y1 + E1 Y0

Dualmente A < B se B1 > A1 o A1 = B1 AN D (B0 > A0 ), ossia:

L = Ā1 B1 + E1 Ā0 B0

Le funzioni G, E e L, come detto, sono facilmente ricavabili anche per il comparatore

a 4 bit seguendo le stesse considerazioni fatte. La Figura 20 mostra il comparatore a 4

bit realizzato. Il dispositivo ha otto ingressi (A3 − A0 , B3 − B0 ) e restituisce il risultato

su 3 bit. A = B se A3 = B3 , A2 = B2 , A1 = B1 , A0 = B0 per cui la funzione logica E

può essere facilmente espressa come:

E = E3 E2 E1 E0

Le funzioni logiche G e L sono, invece:

G = A3 B̄3 + E3 A2 B̄2 + E3 E2 A1 B̄1 + E3 E2 E1 A0 B̄0

L = Ā3 B3 + E3 Ā2 B2 + E3 E2 Ā1 B1 + E3 E2 E1 Ā0 B0

La Tabella 4 riporta la tabella di verità del dispositivo completo, mentre nella Figura 21

è mostrato il layout realizzato. L’analisi effettuata tramite il test di Figura 22 mostra

il comportamento del comparatore a 4 bit quando esso viene sollecitato dai seguenti

ingressi: A = C000, B = 0000 (LSB a destra) dove C indica che il valore varia tra 0

e 1. Trascurando il transitorio iniziale, si può notare come i segnali E0 , E1 , E2 e E3

hanno una transizione 0-1 via via sempre più lenta: ciò è causato dalla struttura delle

interconnesioni la cui lunghezza cresce (da sinistra a destra nella Figura 21 - E0 vede un

carico minore, mentre E3 vede un carico maggiore) causando un aumento della capacità

15

A3 , B3

A3 > B3

A3 < B3

A3 = B 3

A3 = B 3

A3 = B 3

A3 = B 3

A3 = B 3

A3 = B 3

A3 = B 3

A2 , B2

X

X

A2 > B2

A2 < B2

A2 = B2

A2 = B2

A2 = B2

A2 = B2

A2 = B2

A1 , B1

X

X

X

X

A1 > B1

A1 < B1

A1 = B1

A1 = B1

A1 = B1

A0 , B0

X

X

X

X

X

X

A0 > B0

A0 < B0

A0 = B0

A>B

H

L

H

L

H

L

H

L

L

A<B

L

H

L

H

L

H

L

H

L

A=B

L

L

L

L

L

L

L

L

H

Tabella 4: Tabella di verità per il comparatore 4 bit. H = High Voltage Level, L = Low

Voltage Level, X = Don’t Care.

parassita che diventa sempre più importante. Sulla commutazione 0-1 del segnale A3 ,

il dispositivo risponde commutando le uscite in modo che la funzione A = B risulti

falsa, mentre la funzione A > B diventa vera. In particolare, il ritardo di propagazione

t HL+t LH

= 489+323

ps = 406 ps che è un tempo

dell’uscita A = B risulta essere tp = p 2 p

2

inferiore al ritardo calcolato nel caso peggiore per il sommatore a 4 bit. Questa analisi

risulterà determinante per il calcolo della massima frequenza computazionale a cui potrà

lavorare il circuito in pipeline.

Verranno di seguito riportati alcuni dettagli implementativi utilizzati per la progettazione del comparatore a 4 bit in modo da ridurre le capacità parassite delle singole porte

logiche. Un esempio molto significativo è rappresentato dalla porta AND a 4 ingressi utilizzata per il calcolo della funzione di uguaglianza. La Figura 23 mostra come per ridurre

le capacità di diffusione siano state utilizzate diffusioni in comune sia per la connessione

in serie dei transistor NMOS sia per la connessione in parallelo dei transitor PMOS. Per

il secondo caso, le interconnessioni sono state realizzate utilizzando alternativamente i

contatti collocati tra le piste di polisilicio: il primo come contatto di alimentazione, il

secondo per l’uscita della porta, il terzo per l’alimentazione e così via.

5

Pipeline

La pipeline è una tecnologia utilizzata nell’architettura hardware dai microprocessori per

incrementare il throughput, ovvero la quantità di istruzioni eseguite in una data quantità

di tempo, parallelizzando i flussi di elaborazione di più istruzioni: essa aumenta lo sfruttamento delle risorse e il flusso di dati in uscita. Se si considera un blocco combinatorio

formato da tre funzioni logiche più o meno complesse e tra di esse si interpongono dei

registri che permettono di trattare i dati come un flusso continuo, il vantaggio rispetto all’approccio convenzionale risulta evidente. Il blocco combinatorio viene, in questo

modo, suddiviso in tre sezioni ciascuna delle quali ha un tempo di propagazione minore

rispetto alla logica originaria. Questo riduce effettivamente il valore del minimo periodo

16

di clock ammissibile:

Tmin,pipe = tc−q + max {tp,logic1 , tp,logic2 , tp,logic3 } + tsu

(9)

dove tc−q è il tempo di progazione dei registri, tsu è il tempo di setup dei registri e tp,logic1 ,

tp,logic2 , tp,logic3 sono i tempi di ritardo delle singole sezioni della logica combinatoria.

Un sistema pipeline può essere realizzato usando latch positivi e negativi a passtransistor al posto di registri edge-triggered. Ad esempio, nella Figura 24, la logica è stata

introdotta tra il latch master e quello slave in un sistema master-slave. I sistemi basati

su latch offrono maggiore flessibilità per la realizzazione di un pipeline e permettono di

ottenere prestazioni migliori. Quando i CLK e CLK sono non sovrapposti si ottiene il

corretto funzionamento pipeline: il dato in ingresso viene campionato in C1 sul fronte

di discesa di CLK e l’elaborazione del blocco logico F comincia; il risultato del blocco

logico F viene immagazzinato su C2 al fronte di discesa di CLK e quindi l’elaborazione

del blocco logico G comincia.

Nella particolare applicazione presentata in questo progetto, il precedente circuito

pipeline è stato leggermente variato: i pass-transistor lasciano passare un valore logico

degradato (VDD − VT n ) causando un consumo statico di potenza per i circuiti collegati

in cascata e comportando una degradazione dei margini di rumore; inoltre, la logica implementata per il sommatore e il comparatore è stata pensata per funzionare su valori

logici diretti e non negati, per cui i segnali di ingresso non possono essere prelevati dall’uscita degli invertitore riportati in Figura 24, ma devono essere ritenuti validi all’uscita

dei pass-transistor. L’idea sviluppata ha consentito il riutilizzo degli invertitori per pilotare un transistor PMOS di level restorer in modo da ripristinare il valore logico alto

(risolvendo in questo modo anche i problemi legati al consumo statico di potenza). Per

il corretto funzionamento del circuito, il transistor di level restorer deve essere dimensionato adeguatamente affinchè il pass-transistor possa, durante la fase di scarica, portare

la tensione sul proprio nodo di uscita ad un valore inferiore alla tensione di commutazione dell’invertitore. Avendo realizzato il pass-transistor con

minime, il level

dimensioni

0.50

restorer è stato realizzato con un rapporto di aspetto W

=

.

Nella

Figura 25 e

L

0.25

nella Figura 26 sono riportati le simulazioni del pass-transistor senza e con level restorer:

nel secondo caso il segnale p in uscita dal pass-transistor recupera la massima escursione

logica a discapito di una piccola perdita di prestazioni. Inoltre, quando la tensione di

controllo clock del pass-transistor assume il valore logico basso, l’uscita p assume valori

di tensione diversi da 0 a causa di correnti di sottosoglia del transistor NMOS. Ciò comporta delle correnti di cammino diretto tra alimentazione e massa nell’invertitore posto

in cascata causando un consumo statico di potenza.

Sulla base delle considerazioni fatte nei paragrafi precedenti, il minimo periodo di

clock usato per il controllo delle funzioni logiche in pipeline viene imposto dal ritardo di

propagazione del sommatore che risulta essere più elevato del tempo di propagazione del

comparatore (tali tempi di propagazione sono stati calcolati considerando i due dispositivi

singolarmente e ponendo sul nodo di uscita una capacità parassita di 0.01 pF ). Quando,

invece, i due dispositivi vengono inseriti all’interno del circuito completo, essi vedranno

un carico maggiore dovuto ai parassiti delle piste di interconnessione aggiuntive e al

17

fanout più elevato. Il periodo minimo di clock è stato tarato sulla base dei tempi di

propagazione relativi al worst case verificati sperimentalmente inserendo come ingresso

al dispositivo i valori di A e B tali da ottenere il maggior numero di riporti propagati

all’interno della catena di ripple-carry. In queste condizioni, il ritardo di propagazione

del segnale Sum3 (il bit più significativo in uscita dal sommatore) è di circa 12 ns, come

si può osservare dalla Figura 27. Sulla base di queste considerazioni, il periodo minimo

del segnale di sincronizzazione è stato scelto di 30 ns. Nella figura Figura 29 è mostrata

una simulazione del dispositivo completo dove gli ingressi sono stati scelti come segue:

A3 = 0, A2 = 0, A1 = 0, A0 = V ariabile;

B3 = 0, B2 = 0, B1 = 0, B0 = 0;

Cin = 0;

C3 = V ariabile, C2 = 0, C1 = 0, C0 = 0.

La scelta di tali ingressi ha permesso di ottenere uno scenario semplice da poter analizzare

e nel contempo, ha permesso di mostrare il comportamento del dispositivo nel caso in cui

gli input sollecitino tutte le uscite. A0 e C3 sono stati ottenuti con forme d’onda le cui

transizioni non avvengono in corrispondenza dei fronti di salita e di discesa dei segnali di

sincronizzazione CLK e CLK, poichè essi devono essere mantenuti stabili nel momento

in cui il latch commuta ed entra in memorizzazione.

La Figura 28 mostra il layout del circuito completo: l’occupazione di area non è stata

una delle figure di merito principalmente prese in considerazione; tuttavia è possibile

notare come l’intero circuito occupi circa 94x100 µm2 .

6

La progettazione in VHDL

Il VHDL, insieme al Verilog, è il linguaggio più usato per la progettazione di sistemi

elettronici digitali. Esso rappresenta uno degli strumenti che ha consentito lo sviluppo di

tecniche automatiche usate per la progettazione dei circuiti digitali dalle quali, oramai,

non è possibile prescindere soprattutto a causa dell’aumento, anno per anno, della complessità circuitale. Il VHDL permette di descrivere il circuito ad un più alto livello di

astrazione tramite un approccio comportamentale, tramite funzioni logiche, o un approccio strutturale che fa uso di elementi più semplici ed elementari. Il successo delle tecniche

automatiche è comunque dovuto allo sviluppo di strumenti di sintesi che permettono di

tradurre questa descrizione in una rete di porte logiche, minimizzando una funzione di

costo specifica, quale area, ritardo o potenza.

L’intero circuito in pipeline, è stato progettato in un secondo momento tramite una

descrizione VHDL, per mostrare come un approccio di semi-automatico possa ridurre

il tempo di progettazione e facilitare il lavoro del progettista di sistemi digitali rispetto

ad un approccio puramente dedicato. Di seguito è riportato il codice per i vari moduli,

mentre per brevità sarà effettuata un’analisi dettagliata, tramite l’ausilio di un testbench,

solo del dispositivo completo.

Di seguito è riportata l’implementazione del Full-Adder a 1 bit con la tecnologia a

gate di trasmissione, secondo l’appoccio data-flow (ingressi ed uscite sono definiti come un

18

flusso concorrente di segnali). Il segnale di propagazione del riporto è calcolato mediante

la funzione logica XOR tra i due operandi in ingresso al sommatore, mentre il segnale di

somma e riporto uscente tramite la funzione logica che implementa un multiplexer.

ENTITY f u l l a d d e r 1 b i t IS

PORT( x i , y i , r i p _ i n : IN s t d _ l o g i c ; rip_usc , somma : OUT s t d _ l o g i c ) ;

END ENTITY;

ARCHITECTURE f u l l a d d e r 1 b i t _ a r c OF f u l l a d d e r 1 b i t IS

SIGNAL p , rip_usc_neg , rip_adder , somma_neg : s t d _ l o g i c := ’ 0 ’ ;

BEGIN

p <= x i XOR y i ;

rip_usc_neg <= ( (NOT r i p _ i n ) AND p ) OR ( (NOT x i ) AND (NOT p ) ) ;

r i p _ u s c <= NOT rip_usc_neg ;

somma_neg <= ( r i p _ i n AND p ) OR ( (NOT r i p _ i n ) AND (NOT p ) ) ;

somma <= NOT somma_neg ;

END ARCHITECTURE;

Il sommatore a 4 bit è stato progettato tramite un approccio strutturale, dove l’elemento basilare utilizzato è il full-adder a 1 bit.

ENTITY sommatore4bitRC IS

PORT( c_in : IN s t d _ l o g i c ; A, B : IN s t d _ l o g i c _ v e c t o r ( 3 downto 0 ) ;

c_out : OUT s t d _ l o g i c ; s : OUT s t d _ l o g i c _ v e c t o r ( 3 downto 0 ) ) ;

END ENTITY;

ARCHITECTURE sommatore4bitRC_arc OF sommatore4bitRC IS

COMPONENT f u l l a d d e r 1 b i t PORT( x i , y i , r i p _ i n : IN s t d _ l o g i c ;

rip_usc , somma : OUT s t d _ l o g i c ) ;

END COMPONENT;

SIGNAL co0 , co1 , co2 , co3 : s t d _ l o g i c := ’ 0 ’ ;

BEGIN

c0 : f u l l a d d e r 1 b i t PORT MAP(A( 0 ) , B( 0 ) , c_in , co0

c1 : f u l l a d d e r 1 b i t PORT MAP(A( 1 ) , B( 1 ) , co0 , co1 ,

c2 : f u l l a d d e r 1 b i t PORT MAP(A( 2 ) , B( 2 ) , co1 , co2 ,

c3 : f u l l a d d e r 1 b i t PORT MAP(A( 3 ) , B( 3 ) , co2 , co3 ,

c_out <= co3 ;

19

, s (0));

s (1));

s (2));

s (3));

END ARCHITECTURE;

Il comparatore è stato implementato con un approccio data-flow sulla base delle

funzioni logiche G, L ed E introdotte precedentemente.

ENTITY c o m p a r a t o r e 4 b i t IS

PORT( x1 , x2 : IN s t d _ l o g i c _ v e c t o r ( 3 downto 0 ) ;

g , e , l : OUT s t d _ l o g i c ) ;

END ENTITY;

ARCHITECTURE c o m p a r a t o r e 4 b i t _ a r c OF c o m p a r a t o r e 4 b i t IS

SIGNAL e0 , e1 , e2 , e3 :

BEGIN

e0 <= ( x1 ( 0 ) AND x2 ( 0 ) )

e1 <= ( x1 ( 1 ) AND x2 ( 1 ) )

e2 <= ( x1 ( 2 ) AND x2 ( 2 ) )

e3 <= ( x1 ( 3 ) AND x2 ( 3 ) )

s t d _ l o g i c := ’ 0 ’ ;

OR

OR

OR

OR

( (NOT

( (NOT

( (NOT

( (NOT

x1 ( 0 ) )

x1 ( 1 ) )

x1 ( 2 ) )

x1 ( 3 ) )

AND

AND

AND

AND

(NOT

(NOT

(NOT

(NOT

x2 ( 0 ) ) ) ;

x2 ( 1 ) ) ) ;

x2 ( 2 ) ) ) ;

x2 ( 3 ) ) ) ;

e <= e0 AND e1 AND e2 AND e3 ;

g <= ( x1 ( 3 ) AND (NOT x2 ( 3 ) ) )

OR ( e3 AND x1 ( 2 ) AND (NOT x2 ( 2 ) ) )

OR ( e3 AND e2 AND x1 ( 1 ) AND (NOT x2 ( 1 ) ) )

OR ( e3 AND e2 AND e1 AND x1 ( 0 ) AND (NOT x2 ( 0 ) ) ) ;

l <= ( (NOT x1 ( 3 ) ) AND x2 ( 3 ) )

OR ( e3 AND (NOT x1 ( 2 ) ) AND x2 ( 2 ) )

OR ( e3 AND e2 AND (NOT x1 ( 1 ) ) AND x2 ( 1 ) )

OR ( e3 AND e2 AND e1 AND (NOT x1 ( 0 ) ) AND x2 ( 0 ) ) ;

END ARCHITECTURE;

L’ultimo modulo implementa il segnale di sincronizzazione clock, con un periodo di

30 ns, tramite un approccio comportamentale. Il VHDL tramite il costrutto Process,

permette di descrivere il comportamento di un dispositivo tramite una serie di statement

che verranno eseguiti sequenzialmente e non concorrentemente come, invece, avviene per

l’approccio data-flow.

ENTITY c l o c k IS

PORT( c l k : OUT s t d _ l o g i c ) ;

END ENTITY;

ARCHITECTURE c l o c k _ a r c OF c l o c k IS

20

SIGNAL c l k _ s i g : s t d _ l o g i c := ’ 1 ’ ;

BEGIN

PROCESS( c l k _ s i g )

VARIABLE c l o c k _ v a l : s t d _ l o g i c := ’ 1 ’ ;

BEGIN

IF c l o c k _ v a l = ’ 0 ’ THEN

c l o c k _ v a l := ’ 1 ’ ;

ELSE

c l o c k _ v a l := ’ 0 ’ ;

END IF ;

c l k _ s i g <= c l o c k _ v a l AFTER 15 ns ;

END PROCESS;

c l k <= c l k _ s i g ;

END ARCHITECTURE;

Ottenuti gli elementi che implementano la nostra logica funzionale, il dispositivo

completo può essere ottenuto facilmente tramite un approccio strutturale, componendo i moduli presentati precedentemente. Il comportamento dei pass-transistor è stato

modellato lasciando commutare gli ingressi alla logica combinatoria sugli opportuni livelli e fronti del segnale di sincronizzazione utilizzando usando la clausola W HEN del

linguaggio VHDL.

ENTITY p i p e l i n e IS

PORT( Op1 , Op2 , Op3 : IN s t d _ l o g i c _ v e c t o r ( 3 downto 0 ) ;

gr , eq , l o : OUT s t d _ l o g i c ) ;

END ENTITY;

ARCHITECTURE p i p e l i n e _ a r c OF p i p e l i n e IS

COMPONENT sommatore4bitRC PORT( c_in : IN s t d _ l o g i c ;

A, B : IN s t d _ l o g i c _ v e c t o r ( 3 downto 0 ) ;

c_out : OUT s t d _ l o g i c ;

s : OUT s t d _ l o g i c _ v e c t o r ( 3 downto 0 ) ) ;

END COMPONENT;

COMPONENT c o m p a r a t o r e 4 b i t PORT( x1 , x2 : IN s t d _ l o g i c _ v e c t o r ( 3 downto 0 ) ;

g , e , l : OUT s t d _ l o g i c ) ;

END COMPONENT;

COMPONENT c l o c k PORT( c l k : OUT s t d _ l o g i c ) ;

END COMPONENT;

SIGNAL in1 , in2 , in3 , in4 , r i s 1 : s t d _ l o g i c _ v e c t o r ( 3 downto 0 ) := " 0000 " ;

SIGNAL r i s g , r i s e , r i s l , clk_in , c o u t : s t d _ l o g i c := ’ 0 ’ ;

BEGIN

c0 : sommatore4bitRC PORT MAP( ’ 0 ’ , in1 , in2 , cout , r i s 1 ) ;

c1 : c o m p a r a t o r e 4 b i t PORT MAP( in3 , in4 , r i s g , r i s e , r i s l ) ;

21

TestBench VHDL

clk_in

op1

op2

op3

in1

in2

in3

in4

equal

greater

lower

Analisi in Microwind 3.1

Clock

A

B

C

A-IN

B-IN

C-IN

Sum-IN

Out0

Out1

Out2

Tabella 5: Corrispondenza tra i segnali del testbench VHDL e i segnali dell’analisi del

layout completo

c2 : c l o c k PORT MAP( c l k _ i n ) ;

i n 1 <= Op1 WHEN c l k _ i n = ’ 1 ’ OR ( c l k _ i n = ’ 0 ’ AND clk_in ’ e v e n t ) ;

i n 2 <= Op2 WHEN c l k _ i n = ’ 1 ’ OR ( c l k _ i n = ’ 0 ’ AND clk_in ’ e v e n t ) ;

i n 3 <= Op3 WHEN c l k _ i n = ’ 0 ’ OR ( c l k _ i n = ’ 1 ’ AND clk_in ’ e v e n t ) ;

i n 4 <= r i s 1 WHEN c l k _ i n = ’ 0 ’ OR ( c l k _ i n = ’ 1 ’ AND clk_in ’ e v e n t ) ;

g r <= r i s g WHEN c l k _ i n = ’ 1 ’ OR ( c l k _ i n = ’ 0 ’ AND clk_in ’ e v e n t ) ;

eq <= r i s e WHEN c l k _ i n = ’ 1 ’ OR ( c l k _ i n = ’ 0 ’ AND clk_in ’ e v e n t ) ;

l o <= r i s l WHEN c l k _ i n = ’ 1 ’ OR ( c l k _ i n = ’ 0 ’ AND clk_in ’ e v e n t ) ;

END ARCHITECTURE;

Per analizzare il comportamento del dispositivo, è stato implementato tramite un

testbench lo stesso esempio riportato per il circuito progettato in Microwind 3.1 (Figura 29). I segnali in1, in2, in3 e in4 (vettori di 4 elementi) sono rispettivamente: il primo

operando del sommatore a 4 bit prelevato dopo il pass-transistor in ingresso; il secondo

operando del sommatore a 4 bit prelevato dopo il pass-transistor in ingresso; il primo

operando del comparatore a 4 bit prelevato dopo il corrispondente pass-transistor; il secondo operando in ingresso al comparatore a 4 bit prelevato dopo il pass-transistor il cui

ingresso è collegato all’uscita del sommatore. I segnali Op1, Op2 e Op3 sono gli operandi

in ingresso al circuito in pipeline, quindi i segnali posti in ingresso ai pass-transistor. La

Tabella 5 mostra la corrispondenza tra i segnali utilizzati nel testbench di Figura 30 e i

segnali riportati nel test di Figura 29.

ENTITY t e s t IS

22

END ENTITY;

ARCHITECTURE t e s t _ a r c OF t e s t IS

COMPONENT p i p e l i n e PORT( Op1 , Op2 , Op3 : IN s t d _ l o g i c _ v e c t o r ( 3 downto 0 ) ;

gr , eq , l o : OUT s t d _ l o g i c ) ;

END COMPONENT;

SIGNAL op1_val , op2_val , op3_val : s t d _ l o g i c _ v e c t o r ( 3 downto 0 ) := " 0000 " ;

SIGNAL g r e a t e r , e q u a l , l o w e r : s t d _ l o g i c := ’ 0 ’ ;

BEGIN

c0 : p i p e l i n e PORT MAP( op1_val , op2_val , op3_val , g r e a t e r , e q u a l , l o w e r ) ;

op1_val <= " 0001 " AFTER 0 ns , " 0000 " AFTER 33 ns , " 0001 " AFTER 66 ns ,

" 0000 " AFTER 99 ns ,

" 0001 " AFTER 132 ns , " 0000 " AFTER 165 ns ;

op2_val <= " 0000 " ;

op3_val <= " 1000 " AFTER 0 ns , " 0000 " AFTER 19 ns , " 1000 " AFTER 38 ns ,

" 0000 " AFTER 57 ns ,

" 1000 " AFTER 76 ns , " 0000 " AFTER 95 ns ,

" 1000 " AFTER 114 ns , " 0000 " AFTER 133 ns ,

" 1000 " AFTER 152 ns , " 0000 " AFTER 171 ns ;

END ARCHITECTURE;

23

Figura 17: Layout del sommatore a 4 bit realizzato in Microwind 3.1

24

Figura 18: Sommatore a 4 bit: test del dispositivo

Figura 19: Schematizzazione di un comparatore

25

Figura 20: 4-Bit Magnitude Comparator

26

Figura 21: 4-Bit Magnitude Comparator realizzato in Microwind 3.1

Figura 22: 4-Bit Magnitude Comparator: test del dispositivo

27

Figura 23: Dettaglio implementativo: AND a 4 ingressi

Figura 24: Funzionamento del circuito pipeline a due fasi che utilizza registri dinamici

28

Figura 25: Layout Pass-Transistor: test del dispositivo

Figura 26: Layout Pass-Transistor con level restorer: test del dispositivo

29

Figura 27: Worst Case usato per il calcolo dei tempi di ritardo

30

Figura 28: Layout del circuito completo in pipeline

31

Figura 29: Test del dispositivo finale

32

Figura 30: TestBench dell’implementazione VHDL del dispositivo

33