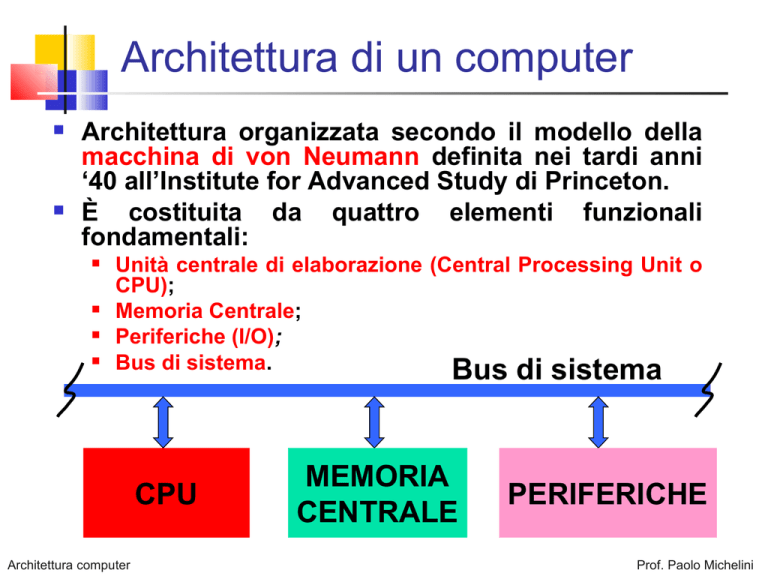

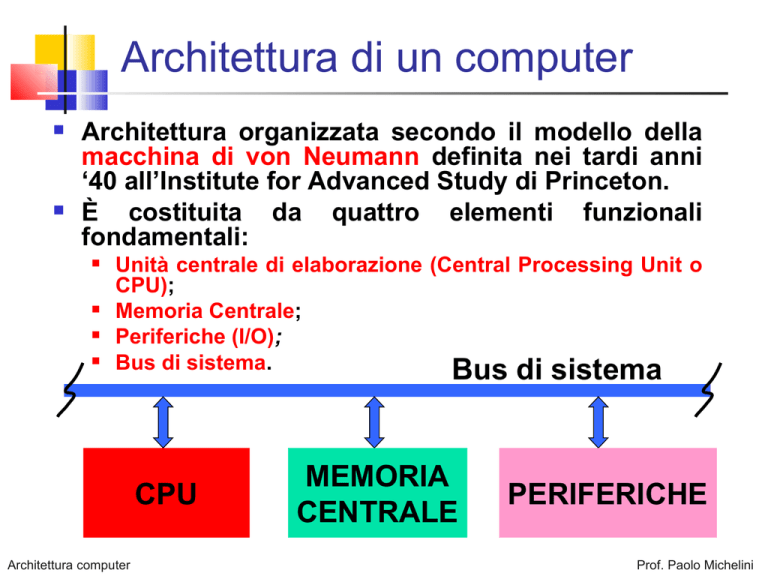

Architettura di un computer

Architettura organizzata secondo il modello della

macchina di von Neumann definita nei tardi anni

‘40 all’Institute for Advanced Study di Princeton.

È costituita da quattro elementi funzionali

fondamentali:

Unità centrale di elaborazione (Central Processing Unit o

CPU);

Memoria Centrale;

Periferiche (I/O);

Bus di sistema.

Bus di sistema

CPU

Architettura computer

MEMORIA

CENTRALE

PERIFERICHE

Prof. Paolo Michelini

La macchina di Von Neumann

A fianco di Von Neumann l'elaboratore IAS di Princeton o macchina di

Von Neumann, ultimata nel 1952. Nella parte bassa dell'elaboratore si

può vedere una fila di tubi catodici (CRT) utilizzati come memoria. Nel

1955 tali memorie vengono sostituite da quelle a nuclei di ferrite.

Architettura computer

Prof. Paolo Michelini

Elementi base

La CPU (Central Processing Unit) contiene i dispositivi elettronici

in grado di interpretare ed eseguire le istruzioni di ogni programma

presente nella memoria centrale e di trasformare i dati in essa

contenuti. Le istruzioni vengono comunemente eseguite in

sequenza.

La memoria centrale contiene sia le istruzioni che i dati

(informazioni necessarie per eseguire un programma). Ha

dimensioni limitate ed è volatile (cioè le informazioni memorizzate

vengono perse allo spegnimento del computer).

Le periferiche consentono uno scambio di informazioni fra

l’elaboratore e l’esterno (ingresso/uscita, memoria secondaria). In

particolare, la memoria secondaria (o memoria di massa) viene

utilizzata per memorizzare grandi quantità di informazioni in modo

persistente. Ha dimensioni elevate, ma l’accesso è meno rapido,

rispetto alla memoria centrale.

Il bus di sistema è un canale che collega i vari elementi funzionali.

Fornisce la connessione elettrica per la trasmissione dei dati tra i

vari elementi.

Architettura computer

Prof. Paolo Michelini

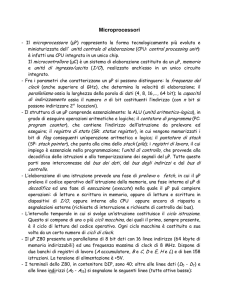

Central Processing Unit (CPU)

SR

PC

A

B

INTR

IR

DR

Architettura computer

ALU

CU

AR

Clock

Prof. Paolo Michelini

Elementi della CPU

l’unità aritmetico-logica (Arithmetic Logic Unit o ALU) esegue le

operazioni aritmetiche e logiche richieste per l’esecuzione delle

istruzioni;

l’unità di controllo (Control Unit o CU), controlla e coordina l’attività

della CPU. In particolare, è responsabile del prelievo, della decodifica

delle istruzioni e dell’invio dei segnali di controllo per effettuare i

passi per l’esecuzione di un’istruzione;

il clock (orologio) “cadenza” le operazioni elementari, permettendo il

sincronismo delle operazioni;

vari registri (ad esempio, A, B, PC, SR, etc.). Un registro è una

locazione di memoria utilizzata per contenere dati, istruzioni, o

indirizzi all’interno della CPU. L’accesso ai registri è molto veloce.

Nei moderni sistemi di elaborazione la CPU è realizzata da un unico

circuito integrato (chip): il microprocessore.

Architettura computer

Prof. Paolo Michelini

Registri principali

DR (Data register o registro dati): viene utilizzato per

trasferire dati da e verso la memoria centrale.

AR (Address Register o registro indirizzi): viene utilizzato

per memorizzare l’indirizzo della cella corrente nella

memoria

centrale

(la

sorgente/destinazione

del

trasferimento di dati).

PC (Program Counter), registro “contatore” del programma.

Contiene l’indirizzo della prossima istruzione da eseguire.

IR (Instruction Register), registro istruzione corrente.

Contiene, istante per istante, l’istruzione che è attualmente

in esecuzione.

A, B: Registri accumulatori o di lavoro. Contengono

operandi e risultati delle operazioni svolte dalle ALU.

INTR (Interrupt Register o registro interruzioni): legato alla

richiesta di operazioni dalle periferiche di I/O.

SR (Status Register o registro di stato), i cui bit forniscono

informazioni sul risultato dell’ultima operazione eseguita

dalla ALU (overflow, zero, riporti, segno).

Architettura computer

Prof. Paolo Michelini

ALU (Arithmetic Logic Unit)

Esegue le operazioni aritmetiche, logiche

ed altre manipolazioni (es: scorrimento) sui

dati.

Opera su alcuni registri specifici chiamati

accumulatori (es: A, B) e modifica i bit del

registro Status Register (SR).

Gli accumulatori contengono il valore degli

operandi

ed

il

risultato

finale

dell’operazione.

I bit dello SR o flag permettono di capire

l’esito

dell’operazione

(es:

overflow,

risultato positivo o negativo, ecc.)

Architettura computer

Prof. Paolo Michelini

CU (Control Unit)

Sovraintende a tutte le attività della CPU,

imponendo la corretta sequenzializzazione

delle operazioni da svolgere. In particolare:

Fetch

L’unità di controllo ha il compito di reperire dalla

memoria centrale le istruzioni di un programma (fetch)

da eseguire (il cui indirizzo è nel registro PC). Le

istruzioni sono organizzate in memoria in sequenza.

Decodifica

La CU interpreta l’istruzione che è stata caricata con il

fetch.

Execute

La CU manda in esecuzione (execute) l’istruzione

trovata (che è stata caricata nel registro IR) finché non

c'è un “halt” del microprocessore.

Architettura computer

Prof. Paolo Michelini

Operatività della CU

Architettura computer

Prof. Paolo Michelini

Le memorie cache

La cache è una memoria speciale della CPU e, a

differenza della memoria centrale, è più piccola e

più veloce. Funziona come un buffer e contiene la

copia delle istruzioni e dei dati che vengono

maggiormente utilizzati. La sua funzione è di

velocizzare eventuali accessi successivi sugli

stessi dati appena ricercati.

Tipicamente si dividono in

Cache di primo livello o L1 interna alla CPU (es: 32 kB).

Cache di secondo livello o L2, (es: 256, 512KB,.., 8 MB) è

esterna al processore.

Architettura computer

Prof. Paolo Michelini

Parametri caratteristici della CPU

Socket: lo zoccolo della scheda madre in cui viene

inserito il processore. In questo caso il numero

rappresenta oltre al nome anche il numero dei pin di

contatto.

N°Core: si intende il numero nuclei, cioè di

processori, montati sul package: 1 se "single core", 2

se "dual core" o 4 se "quad core".

Clock: la frequenza di funzionamento del processore.

Pr. Prod.: sta per "Processo produttivo" ed indica la

dimensione costruttiva (es: 130 nm, 90 nm, 65 nm) ed

il numero di transistor integrati nel processore

espresso in milioni.

Voltag.: sta per "Voltaggio" ed indica la tensione di

alimentazione del processore.

Bus: frequenza del bus di sistema.

Cache: dimensione delle cache di 1° e 2° livello.

Architettura computer

Prof. Paolo Michelini

Esempio di CPU

Nome Commerciale

Socket

N°Core

Core 2 Quad Q6600

4

Core 2 Quad Q6700

Architettura computer

Pr.Prod.

Voltag.

Bus

Cache

65 nm

582 mil.

1,35 V

1066

MHz

L1=4x64KB

L2=2x4MB

32 nm

731 mil.

0.8–1.375

V

1333

MHz

L2 =6×256 KB

L3 = 12 MB

(condivisa fra i

core)

2,4 GHz

775

Core i7 990X Extreme

Edition

Clock

2,66 GHz

1366

6

3.47 GHz

Prof. Paolo Michelini

La memoria centrale

È chiamata anche RAM (Random Access Memory) ed è

volatile (tutte le informazioni vengono perse allo

spegnimento).

Contiene i dati e le istruzioni relative al programma in

esecuzione. La CPU scambia informazioni solo con la

memoria centrale

È strutturata come una sequenza di celle (dette parole o

word) di dimensione prefissata (es: 8, 16, 32, 64 bit)

Ogni parola è univocamente identificata dal suo indirizzo

byte

Es: parola a 8 bit

0

1

2

n

Architettura computer

Prof. Paolo Michelini

Indirizzamento della memoria

L’indirizzamento di una cella di memoria è fatta attraverso il

registro di indirizzi (AR)

Se AR dispone di k bit, saranno indirizzabili 2k celle

Es: k= 32 > celle indirizzabili = 232 = 4 Gbyte

Il valore della cella indirizzato da AR viene

copiato nel registro dati (fase di lettura indicato con R)

scaricato dal registro dati (fase di scrittura indicato con W)

Le operazioni (R/W) vengono coordinate dalla Control Unit

Es: k = 20, word =16 bit

AR

0

2

4

00006

byte 0 byte 1

byte 2 byte 3

01101000|10101101

W

01101000|10101101

R

Notazione esadecimale

DR

FFFFE

Architettura computer

Prof. Paolo Michelini

Caratteristiche delle memorie

La memoria è realizzata con dispositivi a semiconduttore

(materiali che hanno una conducibilità intermedia tra i

conduttori e gli isolanti. Le proprietà dei semiconduttori

diventano interessanti se vengono opportunamente drogati

con impurità)

Il tempo di accesso ad una memoria è dell’ordine della

decina di nanosecondi.

Capacità: valori tipici 128, 256, 512 MB, 1 GB, 2 GB

Possono essere

Dinamiche (DRAM): hanno bisogno di un segnale di refreh, per

mantenere le informazioni in esse contenute.

Statiche (SRAM): più veloci delle precedenti, ma più costose.

Normalmente utilizzate per le memorie cache.

SDRAM (Synchronous DRAM): Permettono un accesso

multiplo su locazioni differenti in memoria. Un segnale di

clock temporizza e sincronizza le operazioni di scambio di dati

con il processore, raggiungendo velocità molto più veloci.

DDR SDRAM (Double Data Rate SDRAM): evoluzione della

SDRAM con velocità doppia alla stessa per il fatto che

consente il trasferimento dei dati sia sul fronte di salita del

clock sia su quello di discesa

Architettura computer

Prof. Paolo Michelini

Moduli di memoria

SIMM (Single Inline Memory module)

Moduli fino a 64 MB, 30 o 72 piedini (pin) con bus dati

a 32 bit

Normalmente montate in coppia per aumentare la

capacità di trasferimento nei processori a 64 bit di bus

dati

DIMM (Dual Inline Memory Module)

Moduli fino a 240 pin (la metà per ogni faccia del

circuito stampato)

Attualmente i più utilizzati con velocità e capacità

maggiore delle precedenti (fino a 8 GB)

DIMM

Architettura computer

Prof. Paolo Michelini

Altre memorie (non volatili)

ROM (Read Only Memory)

Non volatili: mantengono le informazioni anche senza

alimentazione (es: programma di inizializzazione dei

computer o boot)

PROM (Programmable ROM)

Permettono di essere programmate dall’utente tramite dei

dispositivi particolari (programmatori di ROM)

EPROM (Erasable PROM)

Possono essere riscritte più volte, cancellando il loro

contenuto con raggi ultravioletti.

Il software contenuto in queste memorie è normalmente

chiamato firmware (es: Basic Input-Output System o BIOS

dei computer)

Flash Memory

Memorie non volatili a transistor in lettura/scrittura usate

tipicamente nelle fotocamere digitali, smartphone, ecc.

Architettura computer

Prof. Paolo Michelini

Bus di sistema

CPU

MEMORIA

CENTRALE

PERIFERICHE

Data bus

Address bus

Command bus

Architettura computer

Prof. Paolo Michelini

Bus di sistema

È composto da connessioni elettriche (sul circuito

stampato o su un cavo) lungo le quali viene trasferita

l’informazione. Collega due unità funzionali alla volta: una

trasmette e l’altra riceve (master-slave). Il trasferimento

avviene sotto il controllo della CPU (Control Unit).

Architettura computer

Bus dati (Data bus): bidirezionale. Utilizzato dalla CPU per

trasmettere dati dalla memoria al registro dati e viceversa o

verso le interfacce di I/O.

Bus indirizzi (Address bus): unidirezionale. Viene utilizzato

dalla CPU per trasmettere il contenuto del registro indirizzi alla

memoria o alle interfacce di I/O per selezionare il dispositivo

da usare.

Bus comandi (Command bus): unidirezionale. Permette alla

CPU di inviare alla memoria o all’I/O i segnali di

comando/consenso fra le varie unità (es: lettura o scrittura).

Le uniche istruzioni che possono accedere direttamente alla

memoria centrale, sono quelle che trasferiscono i dati da e

verso i registri. Tutte le altre operano solo su registri.

Se la dimensione (numero di bit) del bus dati è uguale alla

dimensione della parola, si può trasferire in parallelo un intero

dato. Altrimenti occorrono più trasferimenti.

Prof. Paolo Michelini

Esempi di bus

I più comuni sono:

Architettura computer

PCI = Peripheral Component Interconnect (max 64 bit a

66 MHz = 528 MB/s di trasferimento dati)

AGP

=

Accelerated

Graphics

sviluppato

per

interfacciare le schede grafiche di nuova generazione.

PCI Express = È basato su un trasferimento dei dati

seriale, a differenza di quello parallelo del PCI, che

semplifica il layout delle schede madri ed è costituito da

una serie di canali (es: PCIx16, costituito da 16 canali,

potendo offrire così il doppio della velocità rispetto allo

standard AGP 8x, quindi teoricamente in grado di

trasferire 4 Gb/s)

Prof. Paolo Michelini

Esempio di operazione della CPU

Z (8 bit) W (8bit)

Circuiti di

controllo

Bus controllo

Registro istruzioni (8 bit)

Registro A

Registro B

Sommatore

Architettura computer

Memoria (a 8 bit)

Bus controllo

registro indirizzi

PC (16 bit)

CU

registro dati

+1

Bus indirizzi

16 bit

3E

0

20

1

27

2

03

3

C6

3A

4

10

20

76

5

6

7

8

Bus dati

8 bit

ALU

Prof. Paolo Michelini

Esempio di operazione della CPU

Le istruzioni contenute in memoria

normalmente consistono di

Codice operativo (operation code): serve

ad attivare un’azione opportuna (es:

somma, input/output, ecc.)

Operandi (operands): contiene gli

indirizzi degli operandi o gli operandi

stessi coinvolti nell’operazione (talvolta

sottintesi)

Architettura computer

Prof. Paolo Michelini

Esempio di operazione della CPU

I fetch

Architettura computer

Il contenuto del PC viene spostato nel registro

indirizzi e viene comandata una lettura in

memoria (lettura della cella 0 = 3EH)

Il dato viene spostato nel registro istruzione

Il PC viene incrementato e diventa = 1

Il codice del registro istruzione viene

decodificato come: muovi nel registro A il dato

che segue il codice operativo.

Il PC viene spostato nel registro indirizzi e

viene

ordinata

la

lettura

della

cella

corrispondente. Il valore 20H viene spostato nel

registro dati.

Il PC viene incrementato e diviene = 2

Prof. Paolo Michelini

Esempio di operazione della CPU

I esecuzione

II fetch

Il dato nel registro dati viene spostato nel

registro A della ALU.

Viene eseguita l’istruzione all’indirizzo 2 (27H )

che richiede di muovere nel registro B il dato

03H che segue il codice operativo (PC =3). PC

diventa 4.

Istruzione alla 4 (C6H) richiede di sommare il

contenuto di A e B e mettere il risultato in A.

II esecuzione

Architettura computer

La CU da indicazione alla ALU di eseguire la

somma.

Prof. Paolo Michelini

Esempio di operazione della CPU

III fase

L’istruzione all’indirizzo 5 (3AH) richiede di

acquisire l’indirizzo dell’operando. Il fetch

dell’indirizzo è fatta in 2 passi.

Architettura computer

Viene letto il valore all’indirizzo 6 (10H) e messo in W

e quello 7 (20H) in Z

Il contenuto di W e Z viene interpretato come un

unico indirizzo a 16 bit (1020H)

Il contenuto di A viene messo nel registro dati.

Viene ordinata una scrittura del dato in A (23H

= 20H + 03H ) nell’indirizzo (1020H)

L’istruzione all’indirizzo 8 (76H) ordina l’halt

della macchina

Prof. Paolo Michelini

Linguaggio assembly

Programmare in formato binario o

esadecimale è molto difficoltoso. Sono

stati così creati i linguaggi assembly, che

utilizzano una codifica simbolica per le

operazioni appena descritte. Questi

linguaggi sono dipendenti dal tipo di

processore usato, non sono quindi

portabili fra macchine con CPU diverse.

Assemblatore: traduce il programma

assembly

in

liguaggio

macchina

(sequenza di 0 e 1).

Architettura computer

Prof. Paolo Michelini

Linguaggio assembly

La traduzione del precedente programma

in pseudo-linguaggio assembly potrebbe

essere:

LD A,20H

load A con il valore 20

H

LD B,03H

ADD A,B

LD (1020H),A

load B con il valore 03H

somma A e B e metti il risultato in A

sposta il contenuto di A all’indirizzo

1020H

HALT

Architettura computer

Prof. Paolo Michelini