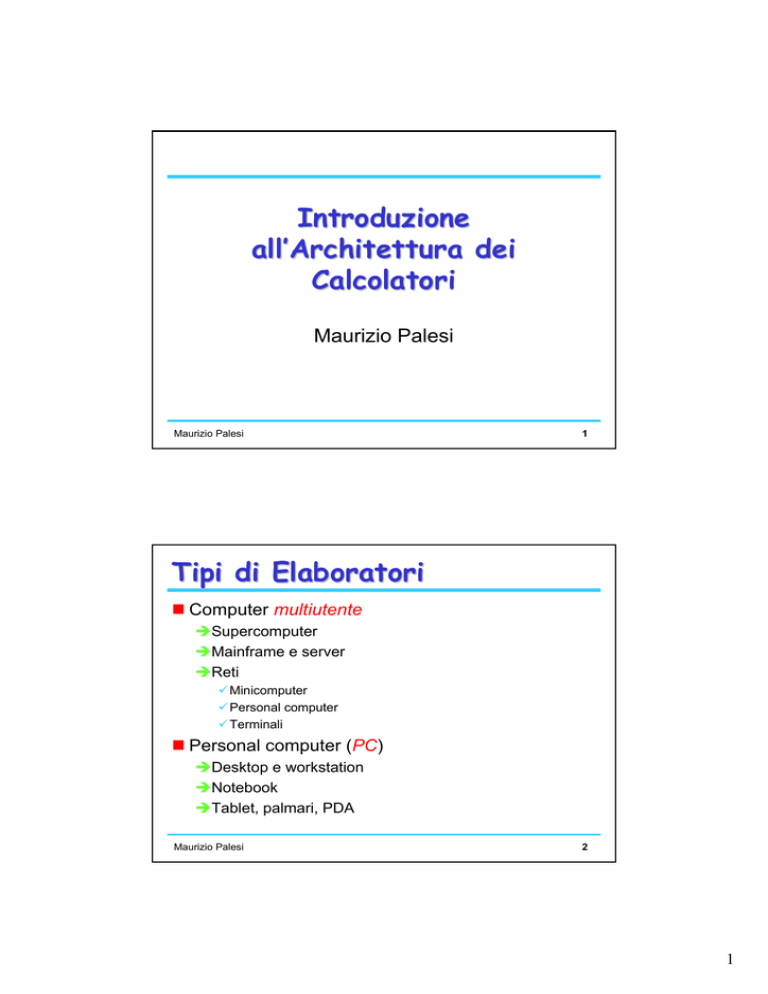

Introduzione

all’Architettura dei

Calcolatori

Maurizio Palesi

Maurizio Palesi

1

Tipi di Elaboratori

Computer multiutente

ÎSupercomputer

ÎMainframe e server

ÎReti

9 Minicomputer

9 Personal computer

9 Terminali

Personal computer (PC)

ÎDesktop e workstation

ÎNotebook

ÎTablet, palmari, PDA

Maurizio Palesi

2

1

Supercomputer

Negli anni ‘80 sembrava che fossero destinati a essere soppiantati

1996 Intel

Î 7000 processori

Î In un secondo poteva effettuare un numero di operazioni pari a quelle che

265 milioni di persone riuscirebbero ad eseguire in 125 anni utilizzando

una calcolatrice manuale

Maurizio Palesi

3

NEC SX-8

Vettoriale

4096 processori

65 Teraflop (65 trilioni di operazioni in FP al

secondo)

Maurizio Palesi

4

2

Mainframe e server

Svolgere funzioni centralizzate

ÎGestione contabilità

ÎControllo dei magazzini

Î…

Affidabilità

Storage

Maurizio Palesi

5

Reti

Minicomputer (o server)

Personal computer (PC)

Terminali

ÎTerminali stupidi

ÎTerminali intelligenti

Maurizio Palesi

6

3

Desktop, Workstation e Notebook

Maurizio Palesi

7

I più piccoli...

Tablet PC

Computer palmari

PDA (Personal Digital Assistant)

Maurizio Palesi

8

4

Maurizio Palesi

9

La Scheda Madre

Maurizio Palesi

10

5

La Legge di Moore

Nel 1965 Gordon Moore (uno dei fondatori di Intel) predisse che:

Î Il numero di transistor contenuti in un chip sarebbe raddoppiato ogni anno e mezzo

Î 1971: Intel 4004, 2300 transistor

Î 2005: Pentium IV, 125 milioni di transistor

Maurizio Palesi

11

Un’Evoluzione Continua

Maurizio Palesi

12

6

Coprocessori e Processori Paralleli

Maurizio Palesi

13

Microprocessori Embedded

Maurizio Palesi

14

7

Migliorare la Capacità Dati

Le strade di recente costruzione, più

ampie, consentono un traffico più

scorrevile rispetto a quelle vecchie e

strette

Lo stesso vale per gli elaboratori

Î I primi PC potevano elaborare solo 8 bit

alla volta

Î Oggi si elaborano 64 bit e, in alcuni casi,

128 bit e oltre alla volta

Dimensione di parola

Maurizio Palesi

15

Migliorare la Velocità di Elaborazione

Miglioramenti tecnologici

ÎAumento della frequenza di clock

Miglioramenti architetturali

ÎLa pipeline

ÎLa memoria cache

Parallelizzazione

Maurizio Palesi

16

8

Migliorare l’Efficienza

CISC (Complex Instruction Set Computer)

Per eseguire l’80% delle operazioni viene effettivamente

utilizzato il 20% delle istruzioni

RISC (Reduced Instruction Set Computer)

Attualmente i CISC hanno quasi raggiunto la potenza dei

RISC

ÎNel 1995 la velocità del più rapido RISC era circa il doppio del più

rapido CISC

ÎNel 1996 il divario era quasi colmato

9 Il processore della Intel aveva quasi raggiunto il 90% della velocità del

RISC

Maurizio Palesi

17

La Legge di Joy (1/2)

Comparare le prestazioni degli elaboratori è come

comparare le auto da corsa

Î…ciò che conta è la velocità!

Complicato

ÎMolti fattori da considerare

Km/h Î Milioni di istruzioni per secondo (MIPS)

Maurizio Palesi

18

9

La Legge di Joy (2/2)

Nel 1984 William Joy, uno dei fondatori di Sun Microsystem, formulò

l’ipotesi che le prestazioni degli elaboratori sarebbero aumentate

secondo un indice prevedibile

MIPS = 2(anno-1984)

Maurizio Palesi

19

Produrre un Chip

Progettazione

Fabbricazione

Controllo

Rivestimento

Maurizio Palesi

20

10

Progettazione

Linguaggi di descrizione dell’hardware

Strumenti CAD

Maurizio Palesi

21

Fabbricazione (1/3)

Maschere

ÎServono per fabbricare i chip

ÎLamine di quarzo su cui è inciso un disegno in

cromo simile ad una stampinatura

9Trasferito su una fetta di silicio tramite un proceso

fotografico

ÎI chip sono costituiti da diversi strati

ÎSono necessarie più maschere

Maurizio Palesi

22

11

Fabbricazione (2/3)

Il silicio è prodotto in lunghi lingotti cilindrici che

vengono poi affettati (wafer)

Il silicio è il principale componente della sabbia

ÎE’ il più comune elemento sulla terra dopo l’ossigeno

Maurizio Palesi

23

Fabbricazione (3/3)

La superficie di una fetta viene ricoperta da uno strato

isolante (diossido di silicio) e poi ulteriormente rivestita da

photoresist

ÎIl photoresist diventa solubile se esposto ai raggi

ultravioletti

Sopra il fotoresist viene posta la maschera

La maschera è sottoposta a raggi ultravioletti

ÎLe zone esposte diventano solubili

Î…e vengono rimosse insieme al diossido di Si

sottostante

ÎIl photoresist viene rimosso

ÎViene completato il primo strato del chip

Maurizio Palesi

24

12

Controllo

La fetta completa contiene centinaia di chip

ÎI quali a loro volta contengono milioni di transistor

Tutti i transistor vengono controllati tramite un test

automatizzato

ÎSonde a forma di ago, collegati a determinati punti della

fetta, eseguono più di 10000 controlli al secondo

ÎI chip che non funzionano bene vengono marcati con

un colore

Maurizio Palesi

25

Rivestimento

Le fette vengono tagliate in singoli chip (die)

I chip marcati vengono scartati

Il rivestimento serve a proteggere il chip e a

fornire i collegamenti elettronici necessari

Maurizio Palesi

26

13

La Memoria: ROM e RAM

ROM (Read Only Memory)

ÎMemoria non volatile

ÎSolitamente utilizzata per memorizzare il

firmware

RAM (Random Access Memory)

ÎMemoria volatile

Maurizio Palesi

27

Tipi di Memoria

DRAM: Dynamic RAM

Î FPM (Fast Page Mode) DRAM

9 Prima tipologia di memorie per sistemi desktop

Î EDO (Extended Data Out) DRAM

9 Leggermente più veloce della FPM

9 BEDO (Burst EDO) DRAM: sfrutta la sequenzialità degli indirizzi

Î SDRAM (Synchronous DRAM)

9 Evita problemi di sincronizzazione

9 Ha sostituito le EDO DRAM

Î DDR DRAM (Double Data Rate Memory)

9 Ha sostituito le SDRAM

9 Maggiore banda

SRAM: Static RAM

Î Più veloce ma più costosa

Î Utilizzata per le cache

Maurizio Palesi

28

14

SIMM e DIMM

In quasi tutti i sistemi non si installano singoli chip

bensì moduli di memoria

Due tipi di moduli

ÎSIMM (Single In-line Memory Module)

ÎDIMM (Dual In-line Memory Module)

I nomi si riferiscono all’involucro e non al tipo di

chip che contengono

I DIMM hanno ormai soppiantato i SIMM

ÎPossono essere usati singoarmente invece che in

coppia

Maurizio Palesi

29

La Memoria Virtuale

Maurizio Palesi

30

15

La Memoria Cache

Maurizio Palesi

31

I Bus di Input e Output

Bus di sistema

ÎGruppo di collegamenti che uniscono la CPU agli altri dispositivi del

computer

Bus locali

ÎPeriferiche ad alte prestazioni (schede grafiche), memoria e CPU

comunicano attraverso un bus locale

ÎISA (Industry Standard Architecture) e EISA (Extended ISA)

9 16 bit @ 8MHz e 32 bit @ 10 MHz

ÎPCI (Peripheral Component Interconnect)

9 256 MBps

ÎAGP (Accelerated Graphic Port)

9 266 MBps e 2.1GBps

Maurizio Palesi

32

16

Le Porte del Computer

Porte seriali

ÎHa il vantaggio di utilizzare solo 2 linee

ÎUn solo bit alla volta (basse prestazioni)

ÎLunghezze fino a 300 metri

Porte parallele

ÎLunghezza massima inferiore ai 30 metri

Maurizio Palesi

33

Porte USB e Firewire (1/2)

Usano cavi sottili

Consentono di connettere dispositivi in serie

Utilizzano la tecnologia Plug&Play

Hot plugging

Distribuiscono la corrente

Maurizio Palesi

34

17

Porte USB e Firewire (2/2)

USB (Universal Serial Bus)

Î127 dispositivi in cascata

Î480 MBps

Firewire

Î63 dispositivi in cascata

Î800 MBps

Maurizio Palesi

35

Caratteristiche Fondamentali

Capacità di eseguire sequenze di istruzioni

memorizzate

Calcolatore = Unità di Elaborazione + Unità

di Controllo

Î1. Preleva le istruzioni dalla memoria

Î2. Interpreta i codici di istruzione

Î3. Effettua le azioni che questi prevedono

Programma = Insieme organizzato di

istruzioni

Maurizio Palesi

36

18

Vista funzionale di un Calcolatore

Ambiente

Trasferimento

Controllo

Elaborazione

Memorizzazione

Maurizio Palesi

37

Componenti di un Computer

Computer

Computer

Processore

Processore

Dispositivi

Dispositivi

Unità di

controllo

Ingresso

Memoria

Memoria

Unità

operativa

Unità di elaborazione e

controllo o Central

Processing Unit (CPU)

Maurizio Palesi

Uscita

Contiene le istruzioni

da eseguire e i dati su

cui operare

Tastiera

Mouse

Monitor

Stampante

Insieme di dispositivi

che consentono la

comunicazione con e

da il mondo esterno

38

19

Organizzazione Generale

CPU

Memoria

Bus di sistema

Ingresso

Uscita

Maurizio Palesi

39

Bus e Master-Slave

Il bus è una linea a cui sono contemporaneamente

connesse le unità del calcolatore e che consente il

trasferimento di dati tra tali unità

ÎProblema: contesa su un mezzo condiviso!

ÎSoluzione: CPU = master, periferiche = slave

Maurizio Palesi

40

20

Bus e Master-Slave - Pregi

Semplicità: 1 sola linea di connessione ∀ # di

dispositivi

Estendibilità: nuovi dispositivi possono essere

aggiunti tramite un’interfaccia al bus senza

influenzare l’HW preesistente

Standardizzabilità: definizione di normative che

consentono a periferiche di costruttori diversi di

interagire correttamente

Maurizio Palesi

41

Bus e Master-Slave - Difetti

Lentezza: l’uso in mutua esclusione del bus

inibisce almeno parzialmente la parallelizzazione

delle operazioni di trasferimento di dati tra

dispositivi

Limitata capacità: al crescere del numero di

dispositivi la presenza di una sola linea comporta

un limite alla capacità di trasferire dati

Sovraccarico della CPU: l’unità centrale viene

coinvolta in tutte le operazioni di trasferimento di

dati

Maurizio Palesi

42

21

Lo Schema di Riferimento

Interfaccia

Interfaccia

I/O

I/O

Interfaccia

Interfaccia

I/O

I/O

Interfaccia

Interfaccia

I/O

I/O

Memoria

Memoria

centrale

centrale

CPU

CPU

Bus dati

Bus indirizzi

Bus di controllo

Maurizio Palesi

43

Tipi di Bus

Bus dati: utilizzato per trasferire dati (es. fra

memoria e CPU, fra CPU e interfacce di I/O)

Bus indirizzi: che identifica la posizione delle celle

di memoria un cui la CPU va a scrivere o leggere

Bus di controllo: in cui transitano i segnali di

controllo che consentono di selezionare le unità

coinvolte in un trasferimento dati (sorgente e

destinazione), di definire la direzione dello

scambio (scrittura o lettura)

Maurizio Palesi

44

22

Architettura di Von Neumann

Burks, Goldstein e Von Neumann sono stati i primi a proporre che il

codice del programma potesse essere memorizzato nella stessa

memoria dei dati

Indirizzi

CPU

CPU

Dati

Memoria

Memoria

Controllo

Memoria indifferenziata per dati o istruzioni

Solo l'interpretazione da parte di CPU stabilisce se una data

configurazione di bit è da riguardarsi come un dato o come

un'istruzione

Maurizio Palesi

45

Collo di Bottiglia Von Neumann

L’organizzazione di Von Neumann è quella più popolare

Consente al processore di manipolare i programmi in modo più

semplice

Svantaggi

ÎLa limitata larghezza di banda della memoria ha un’impatto

negativo sulla velocità di esecuzione dell’applicazione

ÎQuesto fenomeno è noto come “Von Neumann bottleneck”

Maurizio Palesi

46

23

Architettura Harward

Altre organizzazioni memorizzano dati e programmi in memorie diverse

Indirizzi

Memoria

Memoria

Istruzioni

Istruzioni

Dati

Indirizzi

Dati

CPU

CPU

Controllo

Controllo

Memoria

Memoria

Dati

Dati

E’ principalmente utilizzata nei processori ad alte prestazioni e nelle

architetture dedicate per applicazioni di elaborazione digitale dei

segnali (DSP)

Maurizio Palesi

47

Elementi di una CPU

Unità di controllo

ÎLegge le istruzioni dalla memoria e ne

determina il tipo

Unità aritmetico-logica

ÎEsegue le operazioni necessarie per

eseguire le istruzioni

Registri

ÎMemoria ad alta velocità usata per risultati

temporanei

ÎDetermina il parallelismo della CPU

ÎEsistono registri generici e registri specifici

CPU

Unità

Unitàdidi

Controllo

Controllo

Unità

Unità

Aritmetica

Aritmetica

Logica

Logica

Registri

9 Program Counter (PC)

9 Instruction Register (IR)

9…

Maurizio Palesi

48

24

L’Esecutore

Un calcolatore basato sull’architettura di

Von Neumann esegue un programma sulla

base dei seguenti principi

ÎDati e istruzioni sono memorizzati in una

memoria unica che permette sia la scrittura che

la lettura

ÎI contenuti della memoria sono indirizzati in

base alla loro posizione

ÎLe istruzioni vengono eseguite in modo

sequenziale

Maurizio Palesi

49

Tre Tipologie di Istruzioni

Istruzioni Aritmetico Logiche (Elaborazione dati)

ÎSomma, sottrazione, divisione, …

ÎAnd, Or, Xor, …

ÎMaggiore, minore, uguale, maggiore uguale, …

Controllo del flusso delle istruzioni

ÎSequenza

ÎSelezione

ÎCiclo a condizione iniziale, a condizione finale, …

Trasferimento di informazione

ÎTrasferimento dati e istruzioni tra CPU e memoria

ÎTrasferimento dati e istruzioni tra CPU e dispositivi di I/O

Maurizio Palesi

50

25

Linguaggio Macchina e Assembly

Linguaggio macchina

ÎRudimentale

ÎIl concetto di tipo di dato è quasi assente

ÎIl numero di operandi è limitato

ÎIl numero di operazioni previste è ridotto

Struttura di una istruzione della CPU codice operativo op1 op2

Specifica analoga alla codifica in assembly

SOMMA

Reg1 Reg2

Codifica in un ipotetico linguaggio macchina

10000011

001 010

Maurizio Palesi

51

Maurizio Palesi

52

26

Esecuzione delle Istruzioni

Ciclo Fetch-Decode-Execute

Î Prendi l’istruzione corrente dalla memoria e mettila nel

registro istruzioni (IR) [Fetch]

Î Incrementa il program counter (PC) in modo che

contenga l’indirizzo dell’istruzione successiva

Î Determina il tipo dell’istruzione corrente [Decodifica]

Î Se l’istruzione usa una parola in memoria determina

dove si trova

Î Carica la parola, se necessario, in un registro della

CPU

Î Esegui l’istruzione [Execute]

Î Torna al punto 1.

Maurizio Palesi

53

Registri di CPU

IR: Usato per contenere l'istruzione in corso di esecuzione

Î Caricato in fase di fetch

Î Rappresenta l'ingresso che determina le azioni svolte durante la fase di

esecuzione

PC: Tiene traccia dell'esecuzione del programma

Î Contiene l’indirizzo di memoria in cui è memorizzata la prossima istruzione

da eseguire

MAR: contiene l'indirizzo della locazione di memoria da leggere o

scrivere

Î La dimensione di MAR determina l'ampiezza dello spazio di memoria fisica

Î Dalla fine degli anni '80 vengono prodotti microprocessori con bus indirizzi

a 32 bit

MDR: Registro attraverso il quale viene scambiata l'informazione tra la

memoria e la CPU

Î Tradizionalmente la dimensione di MDR dà la misura del grado di

parallelismo della macchina (8, 16, 32, 64 bit)

R0, R1,...Rn: Registri di uso generale

Maurizio Palesi

54

27

Struttura Semplificata di una

CPU

Bus Controllo

Leggi

Scrivi

Unità di controllo

PC

Bus Indirizzi

M

A

R

stato

Indirizzo

Registro

Dato

Bus Dati

PSW

M

D

R

Registro

Operazione

IR

Esegui

Memoria

Memoria

centrale

centrale

oo

periferiche

periferiche

ALU

...

Registro

Unità centrale

Maurizio Palesi

55

Esempio: Lettura dalla Memoria

Fase di Fetch (1 di 2)

Bus Controllo

Leggi

Scrivi

Unità di controllo

PC

Bus Indirizzi

Dato

Bus Dati

M

A

R

M

D

R

stato

Indirizzo

PSW

Registro

Registro

...

Registro

Operazione

IR

Esegui

Memoria

Memoria

centrale

centrale

oo

periferiche

periferiche

ALU

Unità centrale

Maurizio Palesi

56

28

Esempio: Lettura dalla Memoria

Fase di Fetch (2 di 2)

Bus Controllo

Leggi

Scrivi

Unità di controllo

PC

Bus Indirizzi

Dato

Bus Dati

M

D

R

stato

Indirizzo

PSW

Registro

Registro

...

Registro

Operazione

IR

M

A

R

Esegui

Memoria

Memoria

centrale

centrale

oo

periferiche

periferiche

ALU

Unità centrale

Maurizio Palesi

57

Esempio: Lettura dalla Memoria

Decodifica

Bus Controllo

Leggi

Scrivi

Unità di controllo

PC

Bus Indirizzi

Dato

Bus Dati

M

A

R

M

D

R

stato

Indirizzo

PSW

Registro

Registro

...

Registro

Operazione

IR

Esegui

Memoria

Memoria

centrale

centrale

oo

periferiche

periferiche

ALU

Unità centrale

Maurizio Palesi

58

29

Esempio: Lettura dalla Memoria

Esecuzione (1 di 2)

Bus Controllo

Leggi

Scrivi

Unità di controllo

PC

Bus Indirizzi

Dato

Bus Dati

M

D

R

stato

Indirizzo

PSW

Registro

Registro

...

Registro

Operazione

IR

M

A

R

Esegui

Memoria

Memoria

centrale

centrale

oo

periferiche

periferiche

ALU

Unità centrale

Maurizio Palesi

59

Esempio: Lettura dalla Memoria

Esecuzione (2 di 2)

Bus Controllo

Leggi

Scrivi

Unità di controllo

PC

Bus Indirizzi

Dato

Bus Dati

M

A

R

M

D

R

stato

Indirizzo

PSW

Registro

Registro

...

Registro

Operazione

IR

Esegui

Memoria

Memoria

centrale

centrale

oo

periferiche

periferiche

ALU

Unità centrale

Maurizio Palesi

60

30

Esempio: Somma tra due registri

Fetch (come prima)

Bus Controllo

Leggi

Scrivi

Unità di controllo

PC

Bus Indirizzi

Dato

Bus Dati

M

D

R

stato

Indirizzo

PSW

Registro

Registro

...

Registro

Operazione

IR

M

A

R

Esegui

Memoria

Memoria

centrale

centrale

oo

periferiche

periferiche

ALU

Unità centrale

Maurizio Palesi

61

Esempio: Somma tra due registri

Decodifica

Bus Controllo

Leggi

Scrivi

Unità di controllo

PC

Bus Indirizzi

Dato

Bus Dati

M

A

R

M

D

R

stato

Indirizzo

PSW

Registro

Registro

...

Registro

Operazione

IR

Esegui

Memoria

Memoria

centrale

centrale

oo

periferiche

periferiche

ALU

Unità centrale

Maurizio Palesi

62

31

Esempio: Somma tra due registri

Esecuzione

Bus Controllo

Leggi

Scrivi

Unità di controllo

PC

Bus Indirizzi

Dato

Bus Dati

M

D

R

stato

Indirizzo

PSW

Registro

Registro

...

Registro

Operazione

IR

M

A

R

Esegui

Memoria

Memoria

centrale

centrale

oo

periferiche

periferiche

ALU

Unità centrale

Maurizio Palesi

63

32