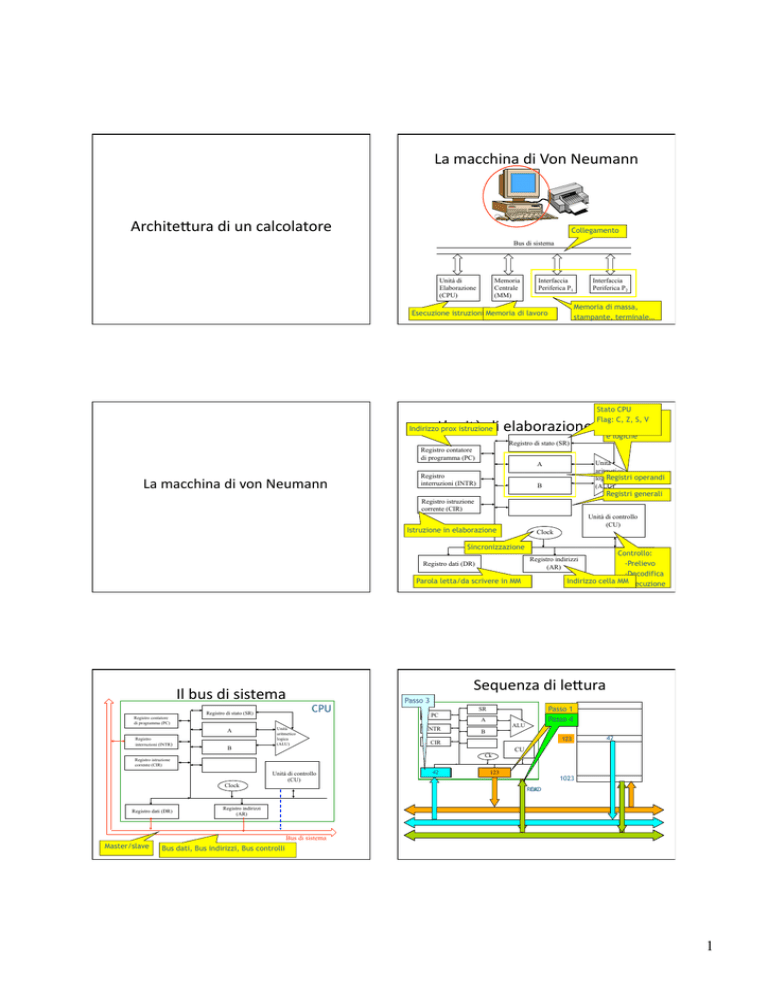

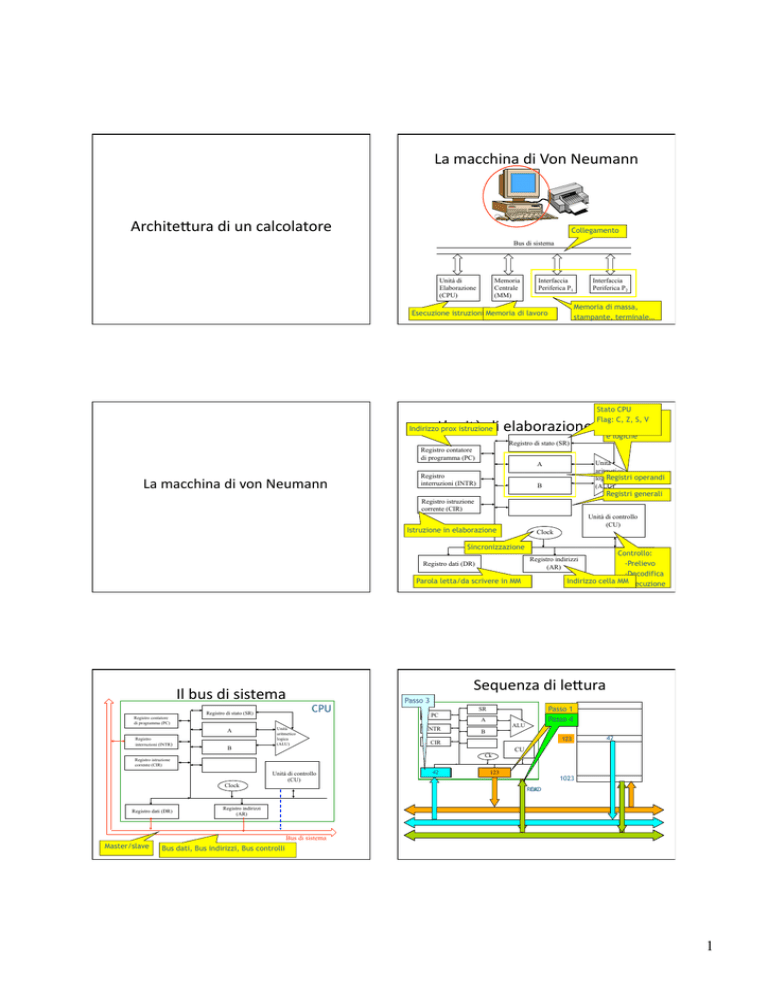

La

macchina

di

Von

Neumann

Archite(ura

di

un

calcolatore

Collegamento

Bus di sistema

Unità di

Elaborazione

(CPU)

Memoria

Centrale

(MM)

Interfaccia

Periferica P1

Interfaccia

Periferica P2

Memoria di massa,

stampante, terminale…

Esecuzione istruzioni Memoria di lavoro

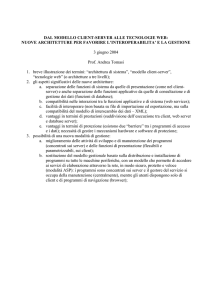

Stato CPU

Operazioni

Flag: C, Z, S, V

aritmetiche

e logiche

L’unità

di

elaborazione

(CPU)

Indirizzo prox istruzione

Registro di stato (SR)

Registro contatore

di programma (PC)

La

macchina

di

von

Neumann

Unità

aritmetico

Registri operandi

logica

(ALU)

A

Registro

interruzioni (INTR)

B

Registri generali

Registro istruzione

corrente (CIR)

Unità di controllo

(CU)

Istruzione in elaborazione

Clock

Sincronizzazione

Controllo:

-Prelievo

-Decodifica

Indirizzo cella MM-Esecuzione

Registro indirizzi

(AR)

Registro dati (DR)

Parola letta/da scrivere in MM

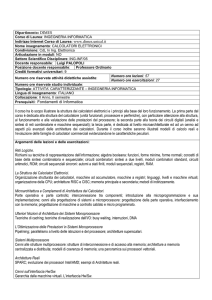

Il

bus

di

sistema

Registro contatore

di programma (PC)

Registro di stato (SR)

A

Registro

interruzioni (INTR)

B

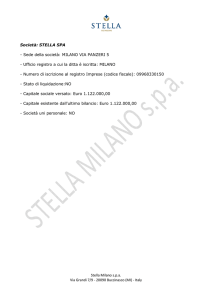

Sequenza

di

le(ura

CPU

Unità

aritmetico

logica

(ALU)

Passo 3

INTR

A

ALU

B

123

123

CIR

Ck

Registro istruzione

corrente (CIR)

Clock

Registro dati (DR)

0

Unità di controllo

(CU)

Passo 1

Passo 4

2

SR

PC

42

DR

42

CU

123

AR

1023

READ

OK

Registro indirizzi

(AR)

Bus di sistema

Master/slave

Bus dati, Bus indirizzi, Bus controlli

1

Sequenza

di

scri(ura

Passo 2

PC

INTR

0

SR

Passo 1

A

Passo 5

3

ALU

B

123

123

CIR

Ck

70

DR

CU

70

42

Passo 4

123

AR

Estensioni all’architettura di von

Neumann

1023

WRITE

OK

Problemi con l’architettura

di von Neumann

• L’esecuzione dei programmi avviene in

sequenza, senza sfruttare le potenzialità di

esecuzione in parallelo dei programmi stessi

• L’unità di elaborazione attende una risposta

da parte di componenti più lenti

• La velocità di accesso alla memoria centrale

(RAM) è bassa rispetto alla velocità

elaborazione della CPU (legge di Moore)

Legge di Moore

la legge di Moore mostra il crescente divario tra la

velocità dei processori e quella delle memorie

Possibili estensioni

• Eseguire in parallelo le fasi di una istruzione

– Architetture Pipeline

– Architetture con parallelismo a livello istruzione

• Usare gerarchie di memorie con costi e prestazioni diversi

– memoria di massa

– memoria centrale

– memoria cache

Architetture pipeline e

superscalari

• Usare più processori in un unico elaboratore

– co-processori

– processori grafici

– architetture multi-processore dotate di CPU indipendenti

2

Architettura Harvard

Architetture pipeline e con ILP

• Pipeline: ciascuna fase nell’esecuzione di

un’istruzione è affidata a un dispositivo specifico

• Memorie per i dati e per le istruzioni sono diverse

– mentre il processore sta eseguendo un’istruzione, può

contemporaneamente acquisire e interpretare le

istruzioni successive

– superpipeline: pipeline più lunga

• Architetture con ILP: replicano i componenti

interni del calcolatore in modo che sia possibile

lanciare l’esecuzione di più istruzioni in ogni

stadio della pipeline

• Tipologia di ILP:

– Dinamico: Architetture superscalari

– Statico: Architetture VLIW

Stadi della pipeline

Stadi della pipeline

• Fasi necessarie per interpretare ed eseguire

un’istruzione

• Esempio

1. Caricamento istruzione

2. Decodifica e preparazione operandi

3. Eventuale lettura di valori dalla memoria o

Esecuzione operazione Aritmetico Logica

4. Scrittura risultato

1

2

3

4

1

ISTR. 1 ISTR. 2 ISTR. 3

…

2

3

4

1

2

3

4

Architetture CISC

Architetture RISC

• CISC (Complex Instruction Set Computers)

• RISC (Reduced Instruction Set Computers).

– il linguaggio macchina contiene un grande

numero di istruzioni

– ogni istruzione è complessa

– l’esecuzione di ogni istruzione richiede più

tempo per la CPU

– poche istruzioni semplici

– è possibile creare pipeline più lunghe e più

efficienti

– i programmi richiedono l’esecuzione di molte

istruzioni

3

La memoria cache

Limitazioni della memoria

tradizionale

• Legge di Moore

– il tempo di accesso alla memoria è più lento rispetto

alla velocità del processore

• Quando il processore accede alla memoria deve

aspettare che i dati di cui ha bisogno vengano

caricati dalla memoria

– il processore spreca cicli di clock in attesa dei dati

senza poter fare del lavoro utile

– si dice che il processore va in stallo

Memoria cache

• Memoria ad alta velocità e

di capacità ridotta situata

tra la memoria principale e

il processore

• Contiene i dati utilizzati

con maggior frequenza dal

processore

– questi dati non devono

essere richiamati ogni volta

dalla memoria più lenta

– Possono esistere più livelli

di cache

Classificazione di Flynn

Architetture di calcolo parallele

Un solo flusso di istruzioni

Più flussi di istruzioni

Un solo flusso di dati

SISD

MISD

Più flussi di dati

SIMD

MIMD

4

Classificazione di Flynn

Memoria distribuita vs. condivisa

Architettura di un sistema SMP

SMP e CMP

Architetture CMP “dual core”

Multi-core vs. hyper threading

• Multi-core:

– due o più processori (chiamati core) sono

presenti sullo stesso chip

• Hyper-threading:

– il processore in certi casi è in grado, di eseguire

due serie (thread) di istruzioni allo stesso tempo

• funziona duplicando alcune parti del processore ma

non quelle responsabili dell’esecuzione delle

istruzioni.

5

Superscalar

Fine-grained

Multithreading

Simultaneous

Multithreading

Comparison of pipeline issue slots in

three different architectures

6