PROGRAMMA DI ELETTRONICA

CLASSE 4A SEZIONE A – Informatica “Abacus”

ANNO SCOLASTICO 2010 – 2011

Richiami e concetti preliminari

o

o

o

o

o

o

o

o

o

o

o

o

Richiami sull’algebra di Boole e sulle porte logiche integrate

Livelli logici TTL

Richiami sulle reti combinatorie

Richiami sulla tecnica di minimizzazione della mappe di Karnaugh

Sintesi di reti logiche combinatorie

Richiami sulle logiche sequenziali

Latches e Flip Flop

Il latch SR: struttura circuitale, tabella della verità, diagramma di

stato

Level Triggered e Edge Triggered Flip Flop

La tebella di transizione dei Flip Flop

Sintesi del FFJK dal FFSR

Il Flip Flop T

I contatori

o Circuiti sequenziali sincroni e asicroni

o Il contatore asincrono mod 4; uso degli ingressi asincroni dei Flip

Flop

o Contatori sincroni tipo UP e tipo Down: diagramma di stato, sintesi

del contatore

o Sintesi di generiche macchine sequenziali

o Determinazione della massima frequenza di clock nei sistemi

sincroni

o Il contatore ad anello

o Il contatore Johnson

o Contatori asincroni mod 2n, contatori sincroni tipo Down, contatori

sincroni modulo qualunque

o Determinazione della massima frequenza di clock nei contatori

asincroni

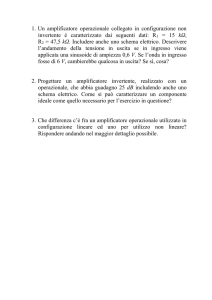

Amplificatori operazionali

o Proprietà di un generico amplificatore di segnale

o La reazione negativa come metodo per migliorare le

caratteristiche di un amplificatore

o Definizione di amplificatore operazionale

o Caratteristiche ideali e reali degli amplificatori operazionali.

o Configurazioni fondamentali:invertente e non invertente, concetto

di massa virtuale.

o Determinazione delle caratteristiche delle configurazioni

fondamentali nei casi ideale e reali:guadagno, impedenza di

ingresso, impedenza di uscita, banda passante.

o Circuiti lineari fondamentali ad operazionali:

• Amplificatore invertente;

• Amplificatore non invertente;

• Buffer;

• Sommatore;

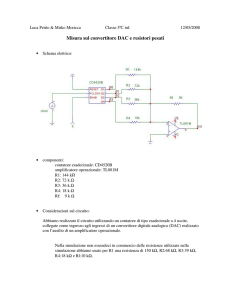

I convertitori Digitale – Analogico (DAC)

o Analisi del DAC a resistori pesati: struttura circuitale, formula

ingresso – uscita, esempi di calcolo

o La struttura e le proprietà di un generico DAC:

• L’intervallo di quantizzazione

• La tensione di fondo scala

• Il massimo valore in uscita

• La risoluzione

• La caratteristica di un DAC ideale

o Errori nei DAC

• Errori compensabili: errore di offset, errore di guadagno

• Errori non compensabili: errore di linearità

• Errori dinamici

• Il tempo di assestamento

o Il DAC R – 2R Ladder

• Struttura circuitale della rete R – 2R e relative proprietà

• Determinazione della formula ingresso – uscita

• Proprietà del DAC R – 2R Ladder

Acquisizione di segnali analogici

o Il problema della acquisizione in digitale di segnali analogici

o Richiami sul concetto di spettro in frequenza e definizione di

segnale a banda limitata

o Il teorema di Shannon ed il campionamento di segnali analogici

o Struttura a blocchi di un circuito di campionamento, l’elemento

circuitale Sample and Hold

o Il processo di quantizzazione dei campioni e l’errore dovuto alla

discretizzazione

o Dinamica del segnale, dinamica del quantizzatore, determinazione

del numero di bit necessari

o Il sistema di acquisizione: frequenza di campionamento, frequenza

di cifra, sincronizzazione delle operazioni (cenni), funzioni dell’

ADC

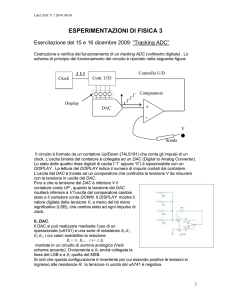

I convertitori Analogico – Digitale (ADC)

o Analisi e classificazione delle famiglie di ADC

o La caratteristica degli ADC

o Il tempo di conversione

o ADC Flash: principio di funzionamento, analisi del circuito nel caso

n=3bit, computo del numero di comparatori

o ADC Half Flash: principio di funzionamento, schema al blocchi per

il caso n=12bit

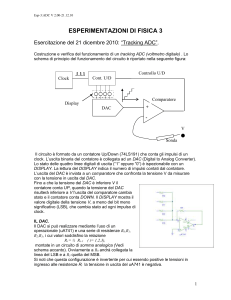

o ADC a reazione: principio di funzionamento e schema a blocchi di

riferimento

o Counting ADC: schema a blocchi, funzionamento, tempo di

conversione

o Tracking ADC: schema a blocchi, funzionamento, funzionamento in

“free running”

o SAR ADC: schema a blocchi, funzionamento, tempo di conversione.

Laboratorio

Realizzazione di un Latch SR a porte NAND come antirimbalzo.

Uso del FFJK come divisore di frequenza.

Realizzazione e collaudo di un contatore sincrono mod.4.

Realizzazione e collaudo di un contatore asincrono mod.3.

Realizzazione e collaudo di una sonda logica.

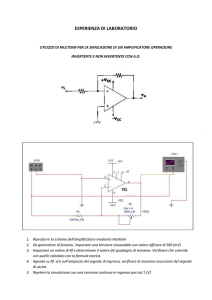

Rilievo della risposta in frequenza di un circuito RC.

Verifica dell’operazionale in configurazione invertente.

Rilievo della risposta in frequenza di un operazionale invertente

con capacità in reazione.

Verifica del circuito sommatore ad operazionale.

Verifica del circuito DAC a resistori pesati.

Verifica del circuito DAC R – 2R Ladder

Verifica del funzionamento dell’integrato DAC0800

Realizzazione e collaudo di un generatore di rampa con DAC0800

Gli alunni

__________________________

I docenti

Prof. Bruno Preite

__________________________

_______________________

__________________________

Prof. Vincenzo Realacci

_______________________