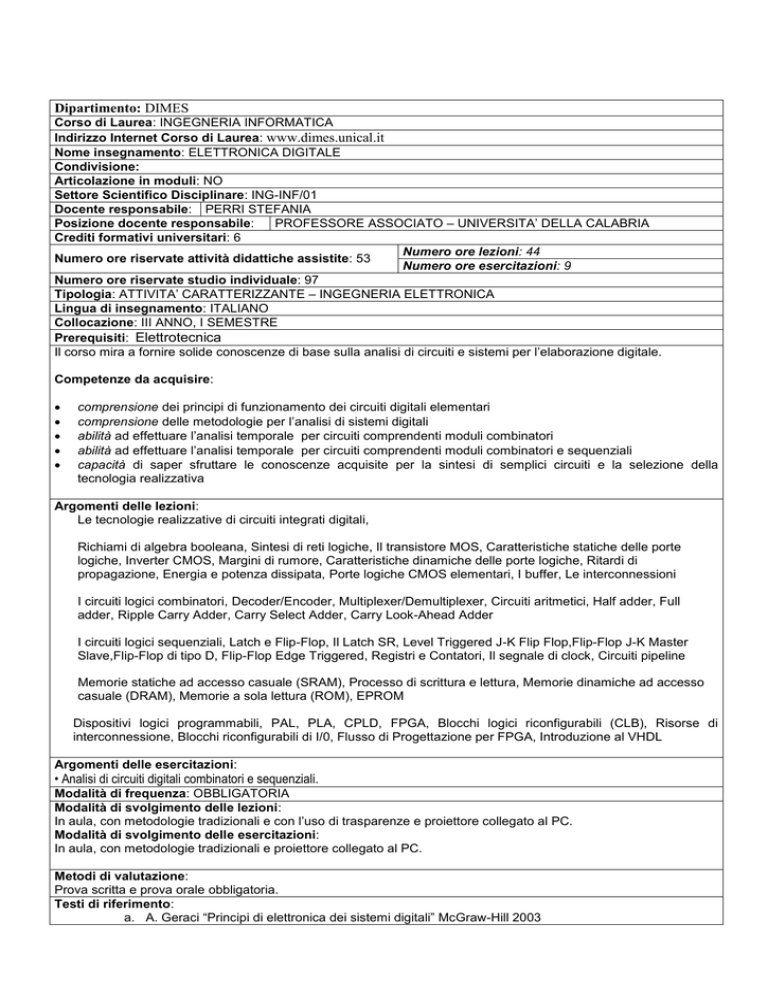

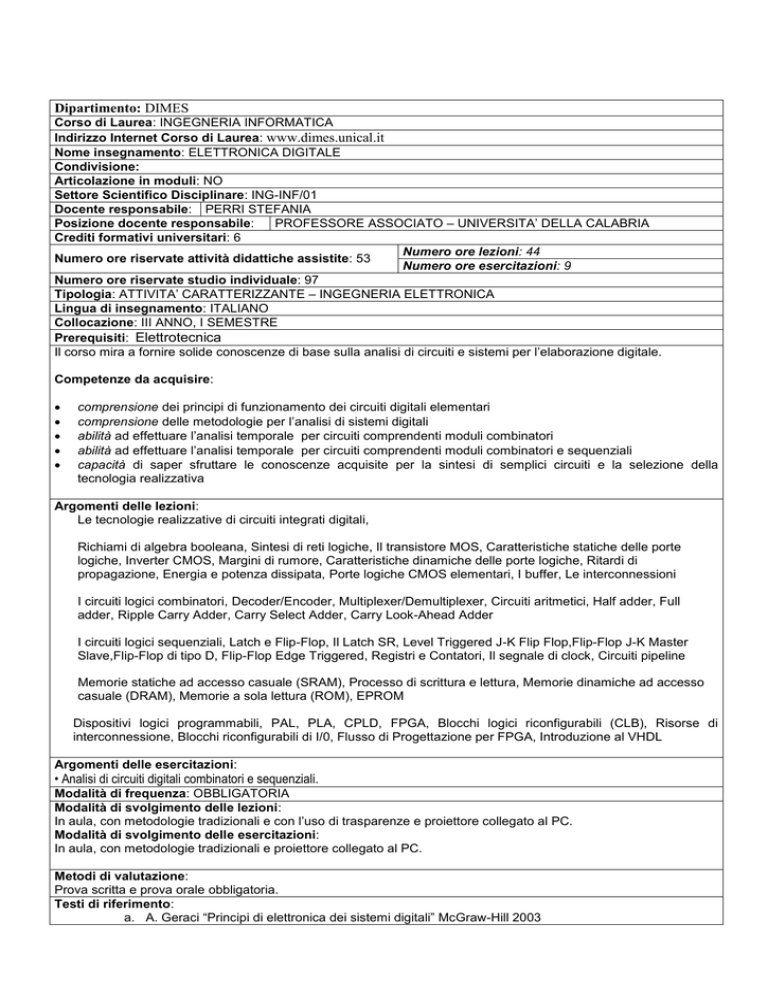

Dipartimento: DIMES

Corso di Laurea: INGEGNERIA INFORMATICA

Indirizzo Internet Corso di Laurea: www.dimes.unical.it

Nome insegnamento: ELETTRONICA DIGITALE

Condivisione:

Articolazione in moduli: NO

Settore Scientifico Disciplinare: ING-INF/01

Docente responsabile: PERRI STEFANIA

Posizione docente responsabile:

PROFESSORE ASSOCIATO – UNIVERSITA’ DELLA CALABRIA

Crediti formativi universitari: 6

Numero ore lezioni: 44

Numero ore riservate attività didattiche assistite: 53

Numero ore esercitazioni: 9

Numero ore riservate studio individuale: 97

Tipologia: ATTIVITA’ CARATTERIZZANTE – INGEGNERIA ELETTRONICA

Lingua di insegnamento: ITALIANO

Collocazione: III ANNO, I SEMESTRE

Prerequisiti: Elettrotecnica

Il corso mira a fornire solide conoscenze di base sulla analisi di circuiti e sistemi per l’elaborazione digitale.

Competenze da acquisire:

comprensione dei principi di funzionamento dei circuiti digitali elementari

comprensione delle metodologie per l’analisi di sistemi digitali

abilità ad effettuare l’analisi temporale per circuiti comprendenti moduli combinatori

abilità ad effettuare l’analisi temporale per circuiti comprendenti moduli combinatori e sequenziali

capacità di saper sfruttare le conoscenze acquisite per la sintesi di semplici circuiti e la selezione della

tecnologia realizzativa

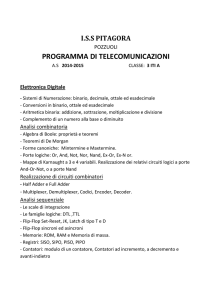

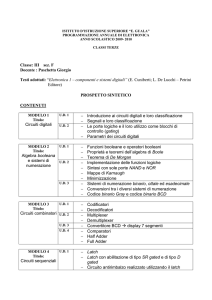

Argomenti delle lezioni:

Le tecnologie realizzative di circuiti integrati digitali,

Richiami di algebra booleana, Sintesi di reti logiche, Il transistore MOS, Caratteristiche statiche delle porte

logiche, Inverter CMOS, Margini di rumore, Caratteristiche dinamiche delle porte logiche, Ritardi di

propagazione, Energia e potenza dissipata, Porte logiche CMOS elementari, I buffer, Le interconnessioni

I circuiti logici combinatori, Decoder/Encoder, Multiplexer/Demultiplexer, Circuiti aritmetici, Half adder, Full

adder, Ripple Carry Adder, Carry Select Adder, Carry Look-Ahead Adder

I circuiti logici sequenziali, Latch e Flip-Flop, Il Latch SR, Level Triggered J-K Flip Flop,Flip-Flop J-K Master

Slave,Flip-Flop di tipo D, Flip-Flop Edge Triggered, Registri e Contatori, Il segnale di clock, Circuiti pipeline

Memorie statiche ad accesso casuale (SRAM), Processo di scrittura e lettura, Memorie dinamiche ad accesso

casuale (DRAM), Memorie a sola lettura (ROM), EPROM

Dispositivi logici programmabili, PAL, PLA, CPLD, FPGA, Blocchi logici riconfigurabili (CLB), Risorse di

interconnessione, Blocchi riconfigurabili di I/0, Flusso di Progettazione per FPGA, Introduzione al VHDL

Argomenti delle esercitazioni:

• Analisi di circuiti digitali combinatori e sequenziali.

Modalità di frequenza: OBBLIGATORIA

Modalità di svolgimento delle lezioni:

In aula, con metodologie tradizionali e con l’uso di trasparenze e proiettore collegato al PC.

Modalità di svolgimento delle esercitazioni:

In aula, con metodologie tradizionali e proiettore collegato al PC.

Metodi di valutazione:

Prova scritta e prova orale obbligatoria.

Testi di riferimento:

a. A. Geraci “Principi di elettronica dei sistemi digitali” McGraw-Hill 2003

b. R. Jaeger “Microelettronica” McGraw-Hill 2004

c. Dispense del docente.

Orario e aule lezioni:

Calendario prove valutazione:

www.dimes.unical.it