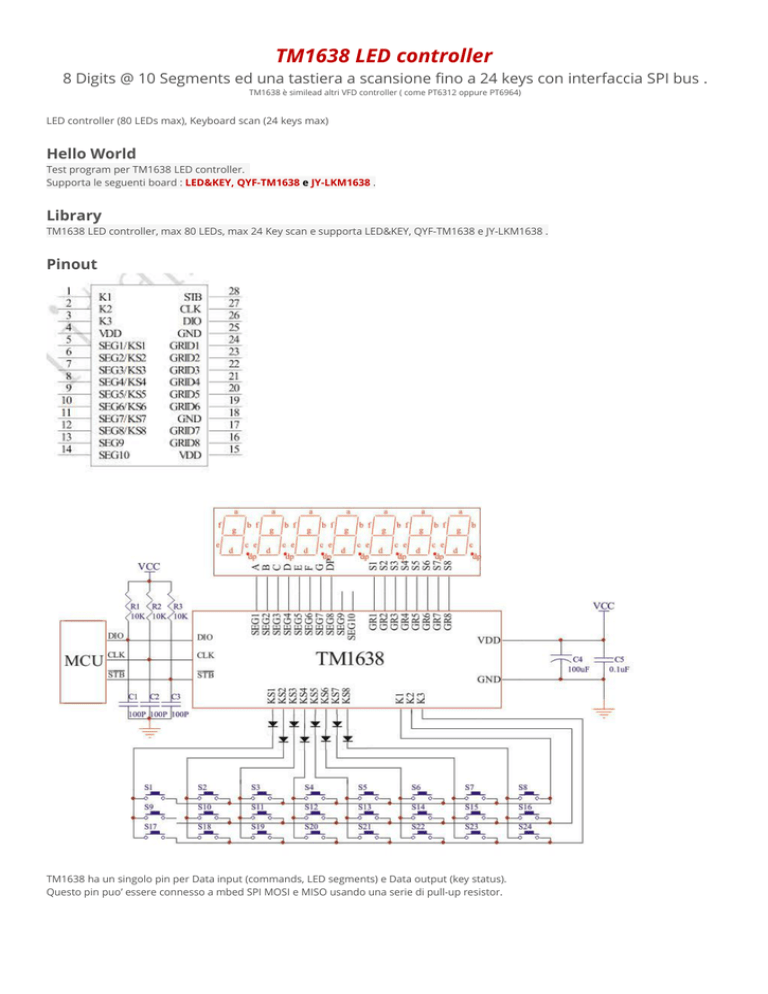

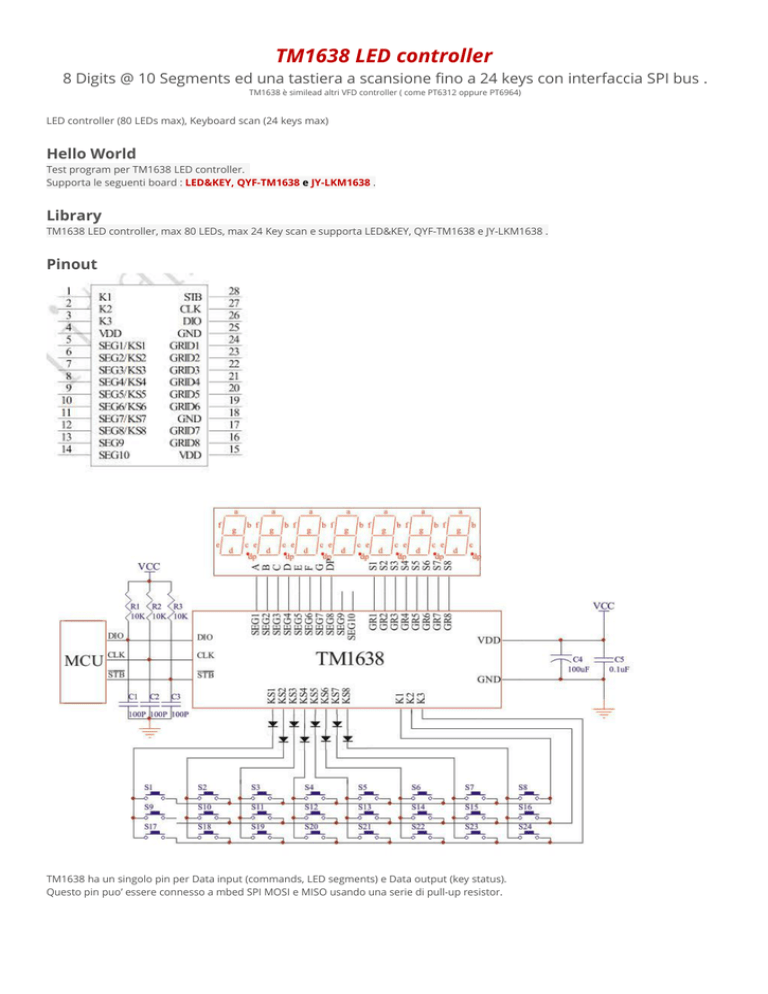

TM1638 LED controller

8 Digits @ 10 Segments ed una tastiera a scansione fino a 24 keys con interfaccia SPI bus .

TM1638 è similead altri VFD controller ( come PT6312 oppure PT6964)

LED controller (80 LEDs max), Keyboard scan (24 keys max)

Hello World

Test program per TM1638 LED controller.

Supporta le seguenti board : LED&KEY, QYF-TM1638 e JY-LKM1638 .

Library

TM1638 LED controller, max 80 LEDs, max 24 Key scan e supporta LED&KEY, QYF-TM1638 e JY-LKM1638 .

Pinout

TM1638 ha un singolo pin per Data input (commands, LED segments) e Data output (key status).

Questo pin puo’ essere connesso a mbed SPI MOSI e MISO usando una serie di pull-up resistor.

Codice di esempio testato su modulo seguente LED&KEY che ha 8 displays 7 segmenti con decimal point DP, 8 LEDs ed 8 pulsanti.

La library supporta metodo printf style per display int, hex e float.

Icons may be set and cleared, cursor locate, display clear and brightness setting are available, keys can be read back and tested.

Displays reperibili sul mercato in diversi formati.

Il piu’ noto è 7-Segment, che è supportato dal TM1638.

Displays con numero maggiore di segmenti per cifra [digit]sono piu’ adatti a mostrare caratteri e simboli.

Sono quindi a 14 o 16 segmenti DP [ DigitalPoint].

Comunque accentando un piccolo compromesso anche un display7 segmenti puo’ mostrare caratteri abbastanza bene, a seguire le

visualizzazioni possibili.

Sono supportate dalla libreria anche le seguenti schede [ board TM1638 ] :

************************************************************************

QYF-TM1638

QYF-TM1638 (8 display a 7 segmenti + 16 pulsanti )

************************************************************************

JY-LKM1638 ( 8 x Display 7 segmenti,Led, Pulsanti )

JY--MCU V:1.1 JY-LKM1638 (8 x Display 7 segmenti, Led Bi-Color, pulsanti, 2 x connettori )

*************************************************************************

Per selezionare la scheda, board TM1638, desiderata si usa

#defines nel file >>> TM1638_Config.h

Dove 1 significa attica e zero NON attiva

// Select one of the

#define TM1638_TEST

#define LEDKEY8_TEST

#define QYF_TEST

#define LKM1638_TEST

testboards for TM1638 LED controller

0

1

0

0

A seguire ripasso

La comunicazione seriale : Due sono i differenti tipi di comunicazione seriale che è possibile utilizzare, protocolli SPI e I2C.

Entrambi i sistemi hanno i propri pro e contro che li rendono più o meno convenienti per l’applicazione data.

Differenze tra SPI e I2C

SPI supporta la comunicazione full-duplex con un throughput molto più alto rispetto ad I2C. non è limitato a parole di 8 bit, in modo da poter

inviare messaggi di ogni genere e con contenuti e scopi arbitrari. L’interfaccia SPI non richiede resistenze di pull-up, il che si traduce in un

minore consumo di energia. Tuttavia, I2C è più semplice avendo meno linee il che significa che meno piedini sono richiesti per interfacciarsi

ad un circuito intergrato. Quando si comunica con più di un dispositivo slave, I2c possiede il vantaggio di un indirizzamento in banda, al

posto di avere una linea chip select per ogni slave. I2c supporta inoltre lo slave acknowledgment che significa che si è certi del dispositivo con

cui si sta comunicando. Con SPI, un master può inviare dati a vuoto e non saperlo. In generale SPI è consigliato per applicazioni che

comunicano lunghi flussi di dati e non solo parole come locazioni di memoria.

Lunghi flussi di dati sono presenti in applicazioni in cui si lavora con un processore di segnali digitali o con un ADC, per esempio, SPI sarebbe

perfetto per riprodurre dell’audio memorizzato in una eeprom e riprodotto attraverso un convertitore digitale analogico. Inoltre, dato che

SPI supporta elevate dimensioni di dati in confronto a I2C, soprattutto grazie alla sua capacità duplex, è molto raccomandato per applicazioni

veloci, che raggiungono le decine di MegaHertz. Inoltre dato che non ci sono dispositivi per l’indirizzamento sviluppati per SPI il protocollo è

molto più difficile da usare nel caso di più dispositivi slave. Questo significa che quando si utilizzano più di un nodo, in genere utilizzare I2C è

consigliato

Interfaccia SPI

come si può vedere nella figura, SPI ha 4 linee. La linea SCLK è la linea di clock, il clock è generato dal master e scandisce la comunicazione in

entrambe le direzioni, e questa linea è un ingresso per tutti gli slave. MOSI è la linea master output slave input e porta i dati dal master verso

lo slave. La linea MISO è l’opposto, prende l’output dello slave e lo indirizza al master. Per finire la linea SS conosciuta anche come CS è

utilizzata per selezionare lo slave a cui trasferire i dati. Di solito la sequenza di trasferimento consiste nel porre a livello basso la linea SS con

un piedino di I/O generico, inviare un numero di X segnali di clock con la giusta polarità e fase, porre a livello alto la linea SS per terminare la

comunicazione.

I dati sono trasmessi in entrambe le direzioni, per cui in un sistema “transmit only” i byte ricevuti saranno scartati e in un sistema “receive

only” deve essere mandato un byte fittizio. Bisogna aver cura di non invertire la il segnale SS durante la comunicazione siccome questo

introdurrà errori. La polarità e il controllo della fase del clock avvengono su ogni fronte del segnale di clock in cui i dati sono ricevuti o inviati.

Deve essere settato per coincidere tra master e slave. Esiste inoltre una versione di SPI 3-wire che tuttavia supporta solo la comunicazione

half duplex. Questa implementazione usa una linea SISO, questa linea bidirezionale singola trasporta i dati in entrata e in uscita dallo slave.

Questa modalità ha una tendenza a non essere supportato dai microcontroller ma può essere facilmente implementato via software.

I segnali

Esso si basa su 4 segnali (si riportano i nomi dei segnali che possono variare a seconda del costruttore. Consultare il datasheet del

componente che si intende utilizzare in caso di dubbi):

SCLK - SCK: Serial Clock (emesso dal master)

SDI – MISO – SOMI – DI - SO: Serial Data Input, Master Input Slave Output (ingresso per il master ed uscita per lo slave)

SDO – MOSI – SIMO – DO – SI: Serial Data Output, Master Output Slave Input (uscita dal master)

CS – SS – nCS – nSS – STE: Chip Select, Slave Select, emesso dal master per scegliere con quale dispositivo slave vuole comunicare

(dalla figura, il segnale SS negato, si comprende che per comunicare con il dispositivo slave deve venire messo a livello logico

basso)

Di questi il Chip Select (CS o SS) non è indispensabile in tutte le applicazioni.

È facile confondersi nei nomi, spesso ambigui, sui segnali di trasferimento dei dati (ingressi e uscite). In ogni caso la consultazione dei

datasheet dei dispositivi scelti dovrebbe chiarire ogni dubbio. Le denominazioni MOSI (Master Output Slave Input), MISO (Master Input Slave

Output) sembrano essere quelle che comportano meno equivoci. Il segnale SCLK è il clock seriale che scandisce gli istanti di emissione e di

lettura dei bit sulle linee di dati. È un segnale emesso dal master ed è quindi quest'ultimo a richiedere di volta in volta la trasmissione di una

"parola"[2]. Il segnale SDI/MISO è la linea attraverso cui il dispositivo (master o slave) riceve il dato seriale emesso dalla controparte. Sullo

stesso fronte di commutazione del clock, il dispositivo emette, con la stessa cadenza, il suo output ponendo il dato sulla linea SDO/MOSI

(linea di output di dato).

Dispositivi slave controllati singolarmente

Esempio di connessione diretta tra un master e tre slave controllati singolarmente

Vantaggi: comunicazione più rapida tra master e singoli slave.

Svantaggi: necessità di avere un pin SS per ogni dispositivo slave.

La linea CS è dedicata all'abilitazione del dispositivo slave da parte del master, il quale può abilitare un qualsiasi dispositivo slave connesso a

trasmettere. La linea CS, normalmente attiva bassa, in caso di disabilitazione (livello logico alto) lascia il dispositivo slave con uscita in alta

impedenza e quindi isolato completamente dal bus indifferentemente dall'esistenza del segnale di clock. Il numero di dispositivi slave che si

possono connettere al bus è limitato esclusivamente dal numero di possibili linee di chip select gestibili dal dispositivo master. La frequenza

di clock, e di conseguenza la velocità del bus, può raggiungere, con questo standard, livelli anche elevati nell'ordine delle decine di MHz ed

anche oltre.

Dispositivi slave connessi in catena (daisy chain)

Master connesso a tre slave connessi secondo una terminologia comune in Daisy chain (uscita di un dispositivo collegata all'ingresso del

dispositivo successivo nella catena)

Vantaggi: uso di un unico pin per selezionare i dispositivi.

Svantaggi: minore velocità di aggiornamento dei singoli slave.

In questo caso la linea SS serve per indicare agli slave quando campionare il dato presente nel registro (il master inietta i bit sulla linea MOSI,

partendo dal bit più significativo da inviare all'ultimo slave. Così facendo, una volta trasmessi tutti i bit destinati a tutti gli slave in questa

sequenza, può segnalare agli slave che i dati in loro possesso nel registro di comunicazione sono effettivamente quelli destinati a loro). Se lo

Slave Select fosse collegato, per esempio, fisso a massa, gli slave non potrebbero sapere se il dato presente nel loro registro di

comunicazione è completo e da campionare, o magari destinato ad uno slave successivo, oppure non allineato alla dimensione del registro

stesso. In questa configurazione è anche impossibile avere conflitto sulla linea MOSI del master (cosa che invece accadrebbe nella

connessione di dispositivi slave controllati singolarmente dove una eventuale abilitazione di più slave creerebbe un conflitto sulla linea MISO

creando problemi nella comunicazione (oltre ad un uso dei dispositivi con uscite in conflitto che non giova alla loro affidabilità nel tempo).

Come avviene la comunicazione

La trasmissione dei dati sul bus SPI si basa sul funzionamento dei registri a scorrimento (shift register). Ogni dispositivo sia master che slave

è dotato di un registro a scorrimento interno i cui bit vengono emessi e, contemporaneamente, immessi, rispettivamente, tramite l'uscita

SDO/MOSI e l'ingresso SDI/MISO. Il registro può avere dimensione arbitraria (ma uguale per i dispositivi master e slave) anche se usualmente

ha la dimensione di 8 bit. Il registro a scorrimento è un'interfaccia completa mediante la quale vengono impartiti comandi e trasmessi dati

che arrivano in modo seriale ma che internamente sono prelevati, a fine trasmissione, in modo parallelo. Ad ogni impulso di clock i

dispositivi che stanno comunicando sulle linee del bus emettono un bit dal loro registro interno rimpiazzandolo con un bit emesso dall'altro

interlocutore. La sincronizzazione è fatta sui fronti di clock di salita o di discesa regolata da 2 parametri impostabili: CPOL e CPHA. CPOL

regola la polarità del clock ovvero discrimina lo stato normale di riposo cui si porta la linea di clock quando non è attiva. Quando CPOL è

impostato a 0, il clock, nel suo stato di riposo, si porta a livello logico basso; viceversa il clock si porta a livello logico alto durante il tempo di

inattività se CPOL è impostato ad 1. CPHA regola la fase del clock, ovvero il fronte di clock in cui il ricevente campiona il segnale in ingresso.

Se CPOL=0 allora con CPHA possiamo scegliere di campionare il dato sul fronte di salita del segnale di clock, impostando CPHA=0, oppure sul

fronte di discesa, impostando CPHA ad 1. L'inverso accade se CPOL è settato ad 1.

Diagramma temporale dei segnali che illustra le possibili polarità di clock e fase dei dati seriali. La comunicazione illustrata è a 8 bit ("Z"

indica lo stato di alta impedenza)

Queste opzioni, in genere, sono impostabili sul dispositivo master e permettono di adattarlo a tutte le possibili varianti di dispositivi slave che

normalmente, invece, vengono progettati per avere uno dei 4 modi di comunicazione possibili (tutte le combinazioni di CPOL e CPHA). Le

modalità di funzionamento più spesso utilizzate dai dispositivi in commercio sono quelle con CPHA=CPOL=0 e con CPHA=CPOL=1. Il dato di

output è emesso sempre in corrispondenza del

la prima transizione del clock. La comunicazione viene intrapresa sempre su iniziativa del

dispositivo master che abilita lo slave tramite CS e successivamente impone il clock sulla linea dedicata. Con questa procedura ha inizio lo

scambio dei bit tra i due registri. Alla fine di ogni parola trasmessa il contenuto del registro dello slave sarà passato al master e viceversa.

Con opportune parole identificative si possono inviare comandi al dispositivo ricevente che potrà effettuare l'elaborazione assegnata

ponendo quindi nel suo shift-register il dato richiesto che al prossimo ciclo di trasmissione verrà trasmesso al richiedente.

Molti microcontrollori dispongono di un hardware dedicato per la gestione dell'SPI programmabile nei dettagli. Questo non è strettamente

necessario per poter comunicare con un dispositivo slave SPI (come ad esempio una memoria EEPROM): in ogni caso si potrà implementare

nel firmware delle funzioni dedicate al colloquio (che forse risulteranno più lente e occuperanno più spazio nel firmware di quelle disponibili

con un blocco hardware dedicato) ma che comunque permetteranno di comunicare in modo efficiente con la periferica SPI, in quanto non vi

è, nella temporizzazione dei dati, un limite di tempo massimo da rispettare (si tratta infatti di dispositivi statici, che possono cioè sospendere

a tempo indeterminato la comunicazione senza per questo avere perdita di dati; in altre parole hanno dei limiti per quanto riguarda la

velocità massima di trasmissione ma che possono funzionare anche in modo lento quanto si vuole).