IPSIA

DI

BOCCHIGLIERO

a.s. 2012/2013

-classe IV-

Materia: Elettronica Telecomunicazioni ed Applicazioni

---CONVERTITORI AD APPROSSIMAZIONI SUCCESSIVE---

alunna:

IACOVINO FRANCESCA

prof. Ing. Luigi Zumpano

IPSIA

Elettronica-Telecomunicazione ed Applicazioni

Convertoitori ad approssimazioni successive

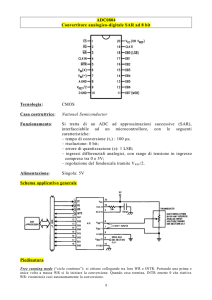

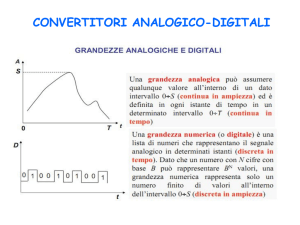

I “convertitori ad approssimazioni successive” sono attualmente i più diffusi nelle applicazioni

che non richiedono una velocità di conversione molto spinta. I componenti commerciali sono

disponibili per risoluzioni da 8, 10 e 12 bit e per tempi di conversione da 2 a 50 μs. Sono stati

realizzati

dispositivi che offrono una comoda interfaccia per la connessione diretta ai

microprocessori e microcontrollori, o che integrano al loro interno un multiplexer analogico, in

modo da essere collegati a più sorgenti di ingresso. Un ADC ad approssimazioni successive usa un

comparatore e un convertitore digitale-analogico, ad ogni passaggio l'ADC prova a impostare un

bit, partendo dal MSB e usando il DAC confronta il segnale campionato con il segnale di ingresso in

feedback. Questo convertitore individua un bit ad ogni iterazione in una sorta di ricerca binaria e

la risoluzione è limitata solo dalle esigenze di sample-rate e dal rumore in ingresso. Il tempo di

conversione dell'ADC ad approssimazioni successive è costante qualunque sia il valore del bit VIN.

TCONV = nTck

Il tempo di conversione si calcola:

Questo schema rappresenta il principio di un convertitore ad approssimazioni successive. Si tratta

di un sistema retroazionato, gestito da un circuito di controllo sequenziale.

CONTROLLO DI TEMPORIZZAZIONE

n

+

Fine conversione

n bit

SAR

-

DAC

VDAC

Esempio:

se consideriamo n=4

Un segnale di Star fa partire la conversione, azzerando il registro SAR (Successive Approximation

Register). Nell'istante successivo il contenuto del SAR viene incrementato di un valore pari alla

metà della dinamica massima (2 n/2=1000b). L'uscita del SAR è collegata ad un convertitore

analogico (ADC), mentre un comparatore permette di confrontare l'uscita del DCA con la tensione

di ingresso, VI. Se risulta VI >VDAC , si incrementa il contenuto del SAR di un valore pari alla metà

del valore precedentemente sommato (01000b), alrimenti si sottrae di tale valore. Questo

processo si ripete fino a che non si ripete l'ultimo bit.

Possiamo rappresentare l'andamento di VDAC nella conversione per approssimazioni successive a 4

Alunna: Iacovino Francesca

a.s 2012/2013

classe IV

pag.2 di 3

IPSIA

Elettronica-Telecomunicazione ed Applicazioni

Convertoitori ad approssimazioni successive

bit con il seguente grafico:

VDAC

15

14

13

12

11

10

9

VI

SAR

1100

1010

1001

1000

8

7

6

5

4

3

2

1

0

Alunna: Iacovino Francesca

t1

t2

a.s 2012/2013

t3

t4

classe IV

t

pag.3 di 3