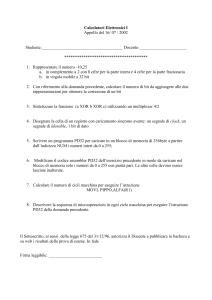

Controllo Digitale

a.a. 2005-2006

Architettura del PIC 18F452

Ing. Federica Pascucci

PIC 18F452

Caratteristiche

I

I

Frequenza operativa: 40 MHz

Memorie:

I

I

I

I

I

Program FLASH memory: 32 KBytes, 16 K-istruzioni

memorizzabili

Data RAM memory: 1536 Byte

Data EEPROM memory: 256 Byte

Porte di I/O: 5 (port A, B, C, D, E)

Comunicazioni seriali:

I

I

I

USART (universal synchronous asynchronous receiver

trasmitter)

3-wire SPI (serial peripheral interface)

I2 C (inter integrated circuit)

Caratteristiche

I

Comunicazioni parallele: PSP (parallel slave port)

I

Timers interni: 4

I

Convertitore A/D: a 10 bits con 8 canali analogici di

ingresso

I

Set di istruzioni: 75

I

Tensione di alimentazione: +5V stabilizzata

I

Moltiplicatore hardware

I

Codice sorgente compatibile con i pic 16 e 17

Clock

Tre configurazioni differenti

1. Oscillatore a cristalli o ceramico

I

I

I

I

LP

XP

HS

HS+PLL

2. Circuito RC

I

I

RC

RCIO

3. Clock esterno

I

I

EC

ECIO

Oscillatore esterno

I pin OSC1 OSC2 sono collegati ad un oscillatore esterno

LP low power crystal

XP crystal/resonator

HS high speed crystal/resonator

HS+PLL high speed crystal/resonator con PLL abilitato:

quadruplica la frequenza di oscillazione

Circuito RC ed clock esterno

RC OSC1 → RC

OSC2 fRC /4

RCIO OSC1 → RC

OSC2 pin I/O

EC OSC1 → EC

OSC2 fRC /4

ECIO OSC1 → EC

OSC2 pin I/O

ALU

Moltiplicatore hardware 8×8

VANTAGGI

– 1 solo ciclo macchina per eseguire moltiplicazione

– maggior throughput

– codice macchina più snello

Memoria

Tre blocchi di memoria in ogni dispositivo:

I

Program memory (FLASH)

I

Data RAM memory

I

Data EEPROM memory

Program e data memory utilizzano bus separati

(architettura Harvard)

Program memory

I

I

I

32 KB di FLASH memory

16 KB di istruzioni (1 istr = 2 Byte)

stack memory a 31 livelli

–

–

–

–

I

I

I

I

il contenuto del PC è inserito nello stack (PUSH/CALL)

viene eseguita la subroutine o servito l’interrupt

il contenuto del PC viene ripristinato (POP/RETURN)

particolari registri indicano lo stack overflow

1 ciclo macchina × istruzione

2 cicli macchina × chiamate a subroutine

pipeline delle istruzioni

La FLASH program memory è leggibile, scrivibile e

cancellabile durante le normali operazioni,

– lettura: 1 Byte alla volta

– scrittura: 8 Bytes in parallelo

– cancellazione: 64 Bytes contemporaneamente

Data memory

I

I

16 banchi da 256 Byte (4096 Bytes) di tipo RAM

indirizzabile tramite 2 bytes:

I

I

BSR 4 lsb seleziona quale banco di accesso

8 bit indirizzo all’interno del banco

I

GPR General Purpose Register

I

SFR Special Function Register

I

Status Register

N negative bit

OV overflow bit

Z zero bit

DC digit carry (sui lsb)

C carry (sui msb)

Interrupt

I

due livelli di priorità

– HIGH

– LOW

I

Interrupt interni

–

–

–

–

I

Scadenza di timer

Convertitore A/D

Modulo CCP

Comunicazione seriale

Interrupt esterni

– Cambiamento di stato sui pin delle porte di I/O

I

Bit di controllo

– Flag

– Enable

– Priority

Gestione degli Interrupt

– Il registro che abilita gli interrupt di una certa priorità viene

disabilitato

– L’indirizzo dell’istruzione del programma che si sta

eseguendo viene inserito nello stack

– Il vettore degli interrupt è caricato nel PC

– ISR individua l’interrupt che si è attivato

– Viene gestito l’interrupt

– A fine esecuzione della routine di interrupt vengono

riabilitati gli interrupt della stessa priorità

Porte di I/O

I

Cinque porte, che possono funzionare da ingresso o da

uscita, per grandezze sia analogiche che digitali

A : 7 bit, bidirezionale

B : 8 bit, bidirezionale

C : 8 bit, bidirezionale

D : 8 bit, bidirezionale

E : 3 bit, bidirezionale

I

Tre registri

TRISx definisce il verso del flusso di dati sul pin

PORTx serve per la lettura livello del pin

LATx mappato in memoria, serve per l’acquisizione

e l’invio dei dati

I

Alcuni pin sono legati anche a dispositivi interni e non

possono essere usati quando questi sono attivi

Timer

I

Quattro timer

TIMER0

TIMER1

TIMER2

TIMER3

I

I

Pre/post-scaler

Collegamento a oscillatori esterni

Timer0

I

I

I

I

I

8-16 bit di risoluzione

Interrupt generato da overflow

Va reinizializzato dopo l’interrupt

Prescaler a 8 bit

Può essere usato come contatore, rileva i

cambiamenti di stato di un pin

Timer1/Timer3

I

I

I

I

16 bit di risoluzione

Interrupt generato da overflow

Va reinizializzato dopo l’interrupt

Può essere usato come contatore

Sincrono: clock interno

Asincrono: clock esterno

I

I

Prescaler a 2 bit

Reset CCP

Timer2

I

I

I

I

I

I

8-bit di risoluzione

Registro del periodo a 8-bit

Interrupt al raggiungimento di PR2

Prescaler 2 bit

Postscaler 4 bit

Definisce il periodo della PWM

Convertitore A/D

I

8 canali in ingresso

I

10 bit di risoluzione

Vm ax e Vm in definibili via software

I

I

I

tensione di alimentazione

riferimenti letti da particolari pin

I

qualsiasi piedino del convertitore può essere un ingresso A

oD

I

i campioni sono generati con successive approssimazioni

I

il tempo di conversione è dato da

TACQ = TAST + THCC + τ

dove TAST è il tempo necessario per amplificare l’invresso,

THCC è il tempo di carica del condensatore di tenuta e τ è un

parametro dovuto alla temperatura, che va considerato solo se

quest’ultima supera i 25◦ .

I

2 moduli CCP

I

3 modalità di funzionamento

1. Compare

2. Capture

3. PWM

Modalità Compare/Capture

Compare Memorizza il valore del Timer1 (Timer3) al

verificarsi di particolari eventi sul piedino

RCx/CCPx

fronte di salita

fronte di discesa

n-esimo fronte (n=4,16)

Capture Compara il valore del Timer1 (Timer3) con il

registro CCPRX e al verificare dell’uguaglianza

pone il piedino RCx

alto

basso

invertito

invariato

Modalità PWM

PWM onda quadra di periodo prefissato TPWM all’interno

del quale il segnale può stare ad un valore alto per

un tempo Tdc , detto duty cycle.

TPWM viene realizzato impostando il registro del periodo

del timer2 PR2 e si può calcolare come

TPWM = PR2 · 4 · TOSC · Ptmr 2

dove TOSC è determinato dall’oscillatore esterno e

Ptmr 2 è il valore del prescaler del timer2

Tdc viene inserito in appositi registri del modulo PWM

ed ha una risoluzione di 10 bit