ELETTRONICA DELLE TELECOMUNICAZIONI

ESERCITAZIONE DI LABORATORIO - 5

Esercitazione 6: Convertitori A/D Delta e Sigma-Delta

Scopo dell’esercitazione

Gli obiettivi di questa esercitazione sono:

- Verificare il comportamento di un convertitore A/D differenziale

- Determinare la dinamica in ampiezza e frequenza di un A/D tipo delta

- Verificare il comportamento di un convertitore A/D tipo Sigma-Delta

- Determinare la dinamica in ampiezza e frequenza di un A/D tipo Sigma-Delta

Moduli e componenti da utilizzare

I circuiti richiesti devono essere predisposti sulle basette per montaggi senza saldature.

Informazioni sull'uso delle basette sono reperibili sul sito web:

Materiale didattico > Uso delle basette per montaggi senza saldature

Vengono utilizzati comparatori, amplificatori operazionali, e circuiti logici CMOS. Sono

necessarie alimentazioni positive e negative (5 V per entrambe).

I data sheet dei componenti sono reperibili sul sito web:

Materiale didattico > Data sheet

Strumenti richiesti

Alimentatore (+5 e -5 V), generatore di segnale (banda audio), oscilloscopio, frequenzimetro,

multimetro.

Le verifiche di funzionamento dei circuiti vanno eseguite con l’oscilloscopio.

Specifiche di progetto

Il convertitore deve coprire una banda da 10 Hz a 500 Hz, con cadenza di campionamento da

3 a 30 kHz, e segnale di ingresso fino a 5 Vpp.

Avvertenze

Ricordare che nei circuiti CMOS tutti gli ingressi devono essere collegati a una tensione

corrispondente a uno stato logico ben definito, e che a un circuito integrato non deve mai

essere applicata una tensione esterna all’intervallo tra le alimentazioni.

ETLClabDiff6h - © CS, DDC - rev 19/10/2006 10:01 AM

Page 1 of 6

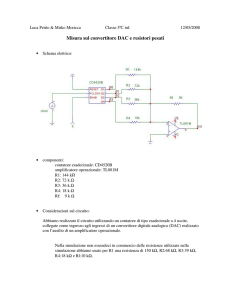

ELETTRONICA DELLE TELECOMUNICAZIONI

ESERCITAZIONE DI LABORATORIO - 5

Generatore di clock

I convertitori Delta e Sigma Delta richiedono un segnale di cadenza (Clock CK). Dato che il

generatore del banco di misura deve essere utilizzato per fornire il segnale di ingresso, il

segnale di clock viene generato da un circuito astabile realizzato con un amplificatore

operazionale.

Il circuito utilizza un comparatore di soglia con

isteresi, realizzato con un Amplificatore

Operazionale tipo TL082 (duale - sono utilizzabili

anche il TL081 o TL084). L’operazionale deve

essere alimentato con tensione simmetrica pari a

+/-5V. Questa stessa alimentazione può essere

direttamente utilizzata per i circuiti integrati CMOS

serie CD4000 (in particolare il FF CD4013), che

accettano tensioni di alimentazione fino a 15V. I

livelli di tensione d’uscita dell’amplificatore sono così

compatibili con quelli del circuito logico.

R2

R1

A1

C1

R3

P

L’operazionale A2 e i componenti R1, R2, R3 e C1 formano un generatore d’onda quadra.

L’operazionale reazionato con R1 e R2, forma un comparatore di soglia invertente con isteresi.

La tensione d’uscita del comparatore (con alimentazioni di + e - 5V) è di circa +3.5V e -3.5V.

Utilizzare due resistenze uguali per R1 ed R2, dell’ordine del centinaio di kΩ.

La tensione sul condensatore in ogni semiperiodo parte da una delle tensioni di soglia e tende

alla tensione d’uscita. Una volta raggiunta la seconda tensione di soglia, l’uscita cambia

segno e il condensatore si carica verso il nuovo livello di uscita.

Calcolare il valore di C1 necessario per ottenere il campo di frequenze di oscillazione voluto

(3 - 30 kHz +/- 20%), con R3 + P variabile da 10kΩ a 110kΩ (resistenza fissa da 10k,

potenziometro da 100k collegato come resistenza variabile).

I convertitori Delta e Sigma-Delta da realizzare in questa esperienza utilizzano lo stesso

circuito generatore di clock.

Montare e provare il generatore di clock prima delle altre parti di circuito.

Integratore

Per il convertitore Delta è realizzato con una cella RC

Per il Delta-Sigma è realizzato come integratore attivo, con amplificatore operazionale TL082

(lo stesso usato in precedenza come comparatore).

ETLClabDiff6h - © CS, DDC - rev 19/10/2006 10:01 AM

Page 2 of 6

ELETTRONICA DELLE TELECOMUNICAZIONI

ESERCITAZIONE DI LABORATORIO - 5

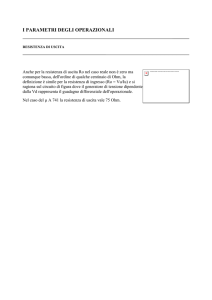

Convertitore A/D differenziale completo (tipo Delta)

La prima parte dell'esperienza prevede montaggio e misure su un convertitore differenziale,

realizzato con un campionatore a flip-flop. Rispetto al convertitore differenziale con

campionatore a interruttore descritto a lezione, questo circuito presenta in uscita una

sequenza di livelli (positivi o negativi), anzichè una sequenza di impulsi. Il segnale ricostruito

pertanto è formato da una serie di rampe (integrale dei gradini).

Le misure prevedono una verifica del funzionamento per segnali di ingresso in continua e

sinusoidali, e la verifica dei limiti di dinamica (rumore e sovraccarico), al variare dell’ampiezza

e della frequenza del segnale di ingresso.

Lo schema completo del circuito da utilizzare è riportato in figura.

-5V

FF1

R6

D Set Q

R4

Va

A1

Reset

R5

Vb

C3

Vd

-5V

C2

R2

R1

A2

C1

R3+P

Entrambi gli operazionali possono essere realizzati con un unico integrato del tipo TL082, che

deve essere alimentato con le stesse tensioni del CD4013 (alimentazione simmetrica pari a

+/- 5V). I livelli di tensione d’uscita del comparatore sono così compatibili con quelli del

circuito logico.

Il flip-flop, del tipo CD4013B, deve essere alimentato con alimentazione simmetrica pari a +/5V. Tutti gli ingressi del flip-flop non utilizzato presente nel CD4013 devono essere collegati al

livello basso (–5V).

ETLClabDiff6h - © CS, DDC - rev 19/10/2006 10:01 AM

Page 3 of 6

ELETTRONICA DELLE TELECOMUNICAZIONI

ESERCITAZIONE DI LABORATORIO - 5

Progetto

La resistenza R4 garantisce il passaggio della corrente di polarizzazione di ingresso

dell'operazionale, anche con accoppiamento capacitivo all'ingresso. Il suo valore deve essere

tale da non introdurre eccessivo offset, senza peraltro caricare più del necessario la sorgente

del segnale.

Il filtro passabasso d’anello (R5-C2) e quello di ricostruzione (R6-C3) devono essere identici.

La resistenza R5 ha vincoli analoghi a R4. Progettare i filtri in modo da ottenere uno step di

quantizzazione (γ) di 100mV circa, con clock a 20 kHz.

Verificare se il convertitore può operare nel campo di tensioni e frequenze indicato nelle

specifiche, senza introdurre distorsione da sovraccarico.

Verifiche e Misure

1. Montare dapprima il solo circuito dell’oscillatore, cioè A2, R1, R2, R3, C1. Alimentare il

circuito a +/-5V e verificare che in uscita si abbia un’onda quadra nel campo di frequenze

previsto. Impostare il segnale di clock su circa 20 kHz.

2. Montare il resto del circuito. Alimentare il CD4013 con il piedino di massa collegato al -5V

e il piedino di alimentazione al +5V (per questo circuito logico VH = +5V, e VlL = -5V).

Collegare allo stato basso (-5V) gli ingressi di Set e Reset del flip-flop usato e i piedini di

Set, Reset, Clock e Dato di quello non usato.

3. Lasciare inizialmente scollegato VA e misurare con l’oscilloscopio la tensione nei punti VD,

VB e sull’ingresso invertente di A2. In che condizione si trova in questo caso il

convertitore? Quale parametro del convertitore può essere misurato ?

4. Collegare a VA il generatore di segnale, impostando in uscita una sinusoide di ampiezza

pari a 1Vp. Come si modifica il segnale ricostruito all'aumentare della frequenza del

segnale di ingresso ? Qual è la massima frequenza convertita correttamente dal circuito?

Quale la minima?

5. Variare l’ampiezza della sinusoide e verificare la relazione esistente tra massima

frequenza convertibile e ampiezza del segnale.

6. Variare la frequenza di clock; analizzare e discutere le relazioni tra ampiezza e frequenza

del segnale di ingresso (convertito correttamente) e la frequenza del clock.

7. Quale caratteristica del convertitore peggiora al diminuire dell’ampiezza del segnale di

ingresso ?

8. Che cosa si dovrebbe collegare nel punto Vb per migliorare la qualità del segnale

ricostruito?

ETLClabDiff6h - © CS, DDC - rev 19/10/2006 10:01 AM

Page 4 of 6

ELETTRONICA DELLE TELECOMUNICAZIONI

ESERCITAZIONE DI LABORATORIO - 5

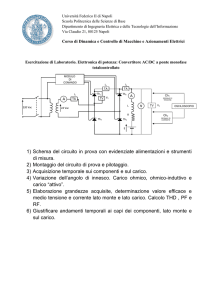

Convertitore Sigma-Delta

In figura è mostrato lo schema di un convertitore A/D tipo Sigma- Delta.

Rispetto al differenziale tipo Delta l’integratore è stato spostato prima del quantizzatore a un

bit (comparatore), e opera sulla somma tra segnale di ingresso e segnale di reazione. Questo

circuito può essere ottenuto dal precedente con lo spostamento di pochi collegamenti (C2,

R4, piedino di ingresso + del comparatore).

-5V

A1

FF1

R6

D Set Q

C3

Reset

C2

R4

-5V

Vu1

R5

Va

Vu2

R2

R1

A2

C1

R3+P

Viene utilizzato lo stesso generatore di clock e lo stesso schema di alimentazione.

Il flip-flop, del tipo CD4013B, deve essere alimentato con alimentazione simmetrica pari a +/5V. In questo modo i livelli di tensione di uscita e ingresso sono compatibili con il

funzionamento dell’integratore. Tutti gli ingressi del flip-flop non utilizzato presente nel

CD4013 devono essere collegati al livello basso (–5V, stato logico L).

Gli operazionali possono essere realizzati con un unico integrato del tipo TL082, che deve

essere alimentato con le stesse tensioni del CD4013. I livelli di tensione d’uscita

dell’integratore e del generatore di clock sono così compatibili con quelli del circuito logico.

ETLClabDiff6h - © CS, DDC - rev 19/10/2006 10:01 AM

Page 5 of 6

ELETTRONICA DELLE TELECOMUNICAZIONI

ESERCITAZIONE DI LABORATORIO - 5

Progetto

Le specifiche di progetto sono:

• dinamica di ingresso del circuito: +/-3V

• frequenza di clock: nominale 20kHz (variabile nel campo indicato in precedenza)

• frequenza massima di segnale: 500Hz

Occorre determinare il valore dei componenti passivi del circuito.

E’ possibile seguire la traccia “Progetto di un convertitore Delta-Sigma” presente sul sito web.

Verifiche e Misure

1. Modificare il circuito rispetto alla configurazione precedente (differenziale).

2. Collegare inizialmente Va a massa e misurare con l’oscilloscopio la tensione nei punti Vu1

e Vu2.

3. Generare una tensione continua nel campo +/-5V e collegarla a Va (utilizzare un

potenziometro collegato tra le alimentazioni + e – 5V).

• Che aspetto ha la tensione su Vu1’?

• E la forma d’onda su Vu2 ?

• Qual è la dinamica in continua del convertitore?

4. Collegare a Va il generatore di segnale, impostando in uscita una sinusoide di ampiezza

pari a 2Vp.

5. Che cosa si osserva su Vu1 e Vu2 al variare della frequenza?

6. E’ possibile stimare la “qualità” del convertitore ?

7. Variare l’ampiezza della sinusoide e verificare se esiste una relazione tra la massima

frequenza convertibile e l’ampiezza del segnale.

8. Quale caratteristica del convertitore peggiora al diminuire dell’ampiezza del segnale di

ingresso ?

ETLClabDiff6h - © CS, DDC - rev 19/10/2006 10:01 AM

Page 6 of 6