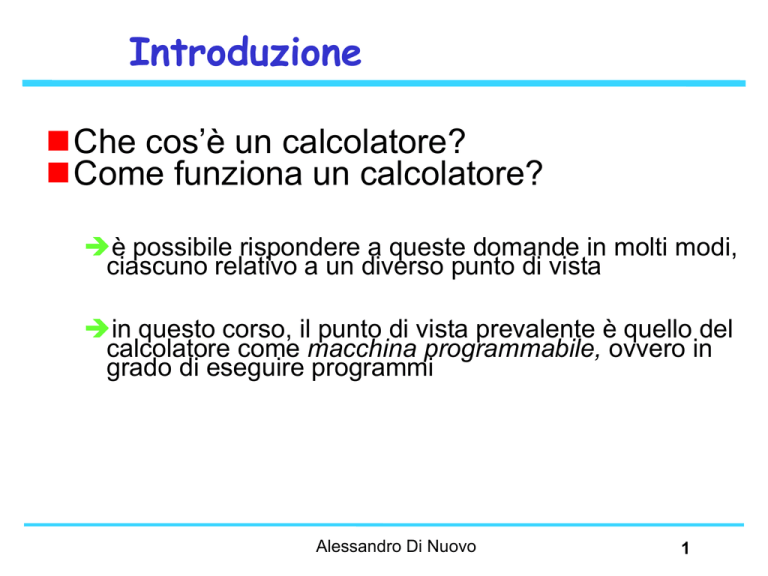

Introduzione

n Che cos’è un calcolatore?

n Come funziona un calcolatore?

è è possibile rispondere a queste domande in molti modi,

ciascuno relativo a un diverso punto di vista

è in questo corso, il punto di vista prevalente è quello del

calcolatore come macchina programmabile, ovvero in

grado di eseguire programmi

Alessandro Di Nuovo

1

Architettura dei calcolatori

n Che cos’è un calcolatore? Come funziona un calcolatore?

è un calcolatore è un sistema

è un sistema è un oggetto costituito da molte parti (componenti) che

interagiscono, cooperando, al fine di ottenere un certo

comportamento

n Studiare l’architettura di un sistema vuol dire

è individuare ciascun componente del sistema

è comprendere i principi generali di funzionamento di ciascun

componente

è comprendere come i vari componenti interagiscono tra di loro

Alessandro Di Nuovo

2

Caratteristiche dell’architettura

• Flessibilità nel calcolo,

architettura non specializzata per un solo tipo di utilizzo ma adatta a svolgere

diversi compiti;

• modularità della struttura

a ogni componente viene demandato lo svolgimento di una funzione specifica del

sistema complessivo;

• scalabilità dei componenti

ognuno dei quali può essere sostituito con uno funzionalmente equivalente ma in

grado di fornire prestazioni migliori;

• standardizzazione dei componenti

per facilitarne la sostituzione in caso di malfunzionamenti;

• abbattimento dei costi,

grazie alla produzione su vasta scala dei componenti;

• semplicità di installazione e di esercizio del sistema;

• disponibilità di applicazioni a basso prezzo di vendita.

Alessandro Di–Nuovo

Informatica e cultura dell’informazione

08/

capitolo 1 – Il

3

3

Hardware e software

n La prima decomposizione di un calcolatore

è relativa alle seguenti macro- componenti:

hardware

è la struttura fisica del calcolatore, costituita da

componenti elettronici ed elettromeccanici

software

è l’insieme dei programmi che consentono all’hardware di

svolgere dei compiti utili

è il software comprende il software di base (tra cui il

sistema operativo) e il software applicativo

Alessandro Di Nuovo

4

Organizzazione a livelli

n Hardware e software sono organizzati a

livelli (o strati).

n Ogni livello usa i servizi offerti dal livello

sottostante.

n Un utente agisce usando i servizi del

livello software applicativo (web,

videogames, programmi di grafica etc)

n Le applicazioni a loro volta usano i servizi

del software di base (es. sistema

operativo)

Utente

Software applicativo

Software di base

(sistema operativo)

n Il livello software di base, utilizza il livello

hardware.

Hardware

Alessandro Di Nuovo

5

Vista funzionale di un Calcolatore

Ambiente

Trasferimento

Controllo

Elaborazione

Memorizzazione

Alessandro Di Nuovo

6

Architettura di un PC

Il diagramma mostra lo

schema logico

dell’architettura di un

personal computer: la

cornice tratteggiata

include gli elementi che si

trovano all’interno della

scheda madre

Tra le periferiche indicate:

tastiera, mouse,

stampante e monitor

sono dispositivi

esterni

Hard Disk e Floppy Disk

sono solitamente

dispositivi interni, cioè

si trovano fisicamente

alloggiati all’interno

del cabinet che

racchiude il PC

Alessandro Di Nuovo

7

7

Tipologia dei calcolatori

n Computer multiutente

è Supercomputer

è Mainframe e server

è Reti

ü Minicomputer

ü Personal computer

ü Terminali

n Personal computer (PC)

è Desktop e workstation

è Notebook

è Tablet, palmari, PDA

Alessandro Di Nuovo

8

Server

n Svolgere funzioni centralizzate

è Gestione contabilità

è Controllo dei magazzini

è …

n Affidabilità

n Storage

Alessandro Di Nuovo

9

Reti

n Minicomputer (o server)

n Personal computer (PC)

n Terminali

è Terminali stupidi (ovvero dotati solo del

necessario hardware per permettere all’utente la

connessione alla rete, es. bancomat, postazioni

vendita di biglietti, etc…)

è Terminali intelligenti (dotati di capacità

computazionale propria, es.

Alessandro Di Nuovo

10

Supercomputer

n Negli anni ‘80 sembrava che fossero destinati a essere

soppiantati

n 1996 Intel

è 7000 processori

è In un secondo poteva effettuare un numero di operazioni pari a

quelle che 265 milioni di persone riuscirebbero ad eseguire in 125

anni utilizzando una calcolatrice manuale

Alessandro Di Nuovo

11

Bluegene

n Blue Gene è il nome di un'architettura progettata per realizzare la

nuova generazione di supercomputer a parallelismo massivo

sviluppati per lavorare con potenze di calcolo che vanno dalle

decine di teraflops per arrivare fino al petaflops. Il più potente

computer BlueGene attualmente sviluppa 478 teraflops. Il

progetto è una cooperazione del United States Department of

Energy (che parzialmente finanzia il progetto), industrie (IBM in

particolare) e Università. Vi sono cinque progetti Blue Gene, tra i

quali il Blue Gene/L, il Blue Gene/C e il Blue Gene/P.

Desktop, Workstation e Notebook

Workstation Rack –

per gentile concessione della Dell

Alessandro Di Nuovo

13

I più piccoli

n Tablet PC

n Smartphones

n Computer palmari

n PDA (Personal Digital Assistant)

Alessandro Di Nuovo

14

Componenti di un Calcolatore

Alessandro Di Nuovo

15

Scheda

Connettori per madre

schede di I/O

aggiuntive

Zoccolo per

la CPU

Connettori per la

memoria

Connettori per dischi

fissi

08/

Alessandro Di Nuovo

Informatica e cultura dell’informazione

– capitolo 1 – Il

1616

Lo schema di riferimento

RAM

CPU

Scheda madre

(motherboard)

Bus dati

Bus indirizzi

Bus di controllo

Interfacce di

I/O

Interfaccia di I/O

Tastiera e mouse

Schermo

Altoparlanti

Alessandro Di Nuovo

Interfacce di

I/O

Memoria di massa

1717

Bus e Master-Slave

n Il bus è una linea a cui sono

contemporaneamente connesse le unità del

calcolatore e che consente il trasferimento

di dati tra tali unità

è Problema: contesa su un mezzo condiviso!

è Soluzione: CPU = master, periferiche = slave

Alessandro Di Nuovo

18

Master-slave : pregi

n Semplicità: 1 solo insieme di linee di

connessione ∀ # di dispositivi

n Estendibilità: nuovi dispositivi possono

essere aggiunti tramite un’interfaccia al bus

senza influenzare l’HW preesistente

n Standardizzabilità: definizione di normative

che consentono a periferiche di costruttori

diversi di interagire correttamente

Alessandro Di Nuovo

19

Master-slave: difetti

n Lentezza: l’uso in mutua esclusione del bus

inibisce almeno parzialmente la

parallelizzazione delle operazioni di

trasferimento di dati tra dispositivi

n Limitata capacità: al crescere del numero di

dispositivi la presenza di una sola linea

comporta un limite alla capacità di trasferire

dati

n Sovraccarico della CPU: l’unità centrale

viene coinvolta in tutte le operazioni di

trasferimento di dati

Alessandro Di Nuovo

20

Schema di riferimento

Alessandro Di Nuovo

21

Tipi di bus

n Bus dati: utilizzato per trasferire dati (es. fra

memoria e CPU, fra CPU e interfacce di I/O)

n Bus indirizzi: che identifica la posizione delle celle di

memoria un cui la CPU va a scrivere o leggere

n Bus di controllo: in cui transitano i segnali di

controllo che consentono di selezionare le unità

coinvolte in un trasferimento dati (sorgente e

destinazione), di definire la direzione dello scambio

(scrittura o lettura)

n Tutti e tre i tipi di bus sono necessari per

interconnettere le unità. IL BUS propriamente detto

è quindi l'insieme di tutte linee che compongono i

bus dati, indirizzi e controllo.

Alessandro Di Nuovo

22

Archittettura di Von Neumann

n Burks, Goldstein e Von Neumann sono stati i primi

a proporre che il codice del programma potesse

essere memorizzato nella stessa memoria dei dati

n Memoria indifferenziata per dati o istruzioni

n Solo l'interpretazione da parte di CPU stabilisce se

una data configurazione di bit è da riguardarsi

come un dato o come un'istruzione

Alessandro Di Nuovo

23

Collo di bottiglia di Von Neumann

n L’organizzazione di Von Neumann è quella

più popolare

n Consente al processore di manipolare i

programmi in modo più semplice

n Svantaggi

è La limitata larghezza di banda della memoria

ha un’impatto negativo sulla velocità di

esecuzione dell’applicazione

è Questo fenomeno è noto come “Von Neumann

bottleneck”

Alessandro Di Nuovo

24

CPU

Central Processing Unit

Unità Centrale di Elaborazione

Alessandro Di Nuovo

25

Legge di Moore

Osservazione fatta da Gordon Moore nel

1965:

il numero dei transistor per cm2

raddoppia ogni X mesi

In origine X era 12/18. Correzioni successive

hanno portato a fissare X=18/24. Questo vuol

dire che c’è un incremento di circa il 40/60%

all’anno.

Alessandro Di Nuovo

26

# Transistor [CPU Intel]

Numero di transistor integrati

1'000'000'000

100'000'000

10'000'000

1'000'000

Andamento previsto dalla legge di Moore: il

numero di transistor integrati in un chip

raddoppia ogni 24 mesi

100'000

Anno

10'000

1978

1982

1986

1990

1994

Alessandro Di Nuovo

1998

2002

2006

2727

Legge di Moore e progresso

• Il progresso della tecnologia provoca un aumento del

numero di transistor per cm2 e quindi per chip.

• Un maggior numero di transistor per chip permette di

produrre prodotti migliori (sia in termini di prestazioni che di

funzionalità) a prezzi ridotti.

• I prezzi bassi stimolano la nascita di nuove applicazioni

(e.g. non si fanno video game per computer da milioni di

€).

• Nuove applicazioni aprono nuovi mercati e fanno nascere

nuove aziende.

• L’esistenza di tante aziende fa crescere la competitività

che, a sua volta, stimola il progresso della tecnologia e lo

sviluppo di nuove tecnologie.

Alessandro Di Nuovo

2828

La memoria

Alessandro Di Nuovo

29

La memoria

Supporto alla CPU: deve fornire alla CPU dati

e istruzioni il più rapidamente possibile

Archivio: deve consentire di archiviare dati e

programmi garantendone la conservazione

e la reperibilità anche dopo elevati periodi di

tempo

Diverse esigenze:

velocità per il supporto alla CPU

non volatilità ed elevate dimensioni per l’archivio

Diverse tecnologie

elettronica: veloce, ma costosa e volatile

magnetica e ottica: non volatile ed economica, ma molto lenta

Alessandro Di Nuovo

3030

Criteri di caratterizzazione di una memoria

Velocità

• tempo di accesso (access time)

(quanto passa tra una richiesta e la relativa risposta)

• velocità di trasferimento (transfer rate)

(quanti byte al secondo si possono trasferire)

Volatilità

• cosa succede quando la memoria non è alimentata?

• per quanto tempo i dati vi rimangono immagazzinati?

Capacità

• quanti byte può contenere? qual è la dimensione massima?

•

Costo (per bit)

Modalità di accesso

•

•

•

•

diretta (o casuale): il tempo di accesso è indipendente dalla posizione

sequenziale: il tempo di accesso dipende dalla posizione

mista: combinazione dei due casi precedenti

associativa: indicato il dato, la memoria risponde indicando l’eventuale

posizione che il dato occupa in memoria.

Alessandro Di Nuovo

3131

La memoria centrale

Alessandro Di Nuovo

32

La memoria centrale (RAM)

Mantiene al proprio interno i dati e

le istruzioni dei programmi in esecuzione

Memoria ad accesso “casuale”

Tecnologia elettronica

veloce ma volatile e costosa

Due “eccezioni”

• ROM: elettronica ma permanente e di sola

lettura

• Flash: elettronica ma non volatile e riscrivibile

Alessandro Di Nuovo

3333

Indirizzi di memoria

I bit nelle memorie sono raggruppati in celle:

tutte le celle sono formate dallo stesso numero di bit;

una cella composta da k bit, è in grado di contenere una

qualunque tra le 2k combinazioni diverse di bit.

Ogni cella ha un indirizzo:

serve come accesso all’informazione;

in una memoria con N celle gli indirizzi vanno da 0 a N–1.

La cella è l’unità indirizzabile più piccola.

In quasi tutti i calcolatori è di 8 bit (un byte).

I byte vengono raggruppati in parole (che oggi sono

di 32/64 bit), su cui la CPU esegue le operazioni.

Alessandro Di Nuovo

3434

Organizzazione della memoria

0

0

0

1

1

1

2

2

2

3

3

3

4

4

4

5

5

5

6

6

7

7

6 parole da 16 bit

8 parole da 12 bit

8

9

10

12 parole da 8 bit

Alessandro Di Nuovo

11

3535

Memoria e collegamenti con bus

• Viene selezionata la parola

di indirizzo 0110due

• il contenuto è 01101100;

• l’operazione è di lettura

(load) o di scrittura (store) a

seconda dei comandi

presenti sul bus di controllo

0110

Bus indirizzi

DECODIFICATORE

linee di

selezione parola

linea 0

0

linea 1

0

linea 2

0

linea 3

0

linea 4

0

linea 5

0

linea 6

1

linea 7

0

linea 8

0

linea 9

0

linea 10

0

linea 11

0

linea 12

0

linea 13

0

linea 14

0

linea 15

0

16 celle di memoria

di 8 bit ciascuna

0

1

1

0

1

1

0

0

0

1

1

0

1

1

0

0

parola

selezionata

leggi/scrivi

Bus di

controllo

Dato

(letto o da scrivere)

Bus dati

Alessandro Di Nuovo

36

Memoria vs. CPU

Le CPU sono sempre state più veloci delle memorie

l’aumento di integrazione ha consentito di realizzare CPU pipeline e super

scalari, molto efficienti e veloci;

nelle memorie è aumentata la capacità più che la velocità.

L’accesso alla memoria passa attraverso il bus

la frequenza di funzionamento del bus è molto più bassa di quella della CPU;

il bus può essere impegnato ad effettuare trasferimenti controllati da

dispositivi di I/O “autonomi” (e.g. DMA).

È difficile riordinare le istruzioni in modo da poter

sfruttare i tempi di attesa della memoria.

È possibile fare memorie molto veloci se stanno nel

chip della CPU, ma sono piccole e costose.

Alessandro Di Nuovo

3737

Le memorie gerarchiche

Memorie di gran capacità, relativamente lente,

economiche ed accessibili tramite il bus:

MGL ovvero Memoria Grossa e Lenta;

dimensioni pari a circa 10 unità;

tempo di accesso (TA) di circa 10 unità.

Memorie veloci, integrate nello stesso chip

della CPU, ma costose:

MPV ovvero Memoria Piccola e Veloce;

dimensioni pari a circa 1 unità;

tempo di accesso pari a circa 1 unità.

Obiettivo: realizzare una memoria grossa e

veloce

dimensioni pari a circa quelle della memoria grossa;

prestazioni pari a circa quelle della memoria veloce.

Alessandro Di Nuovo

3838

Una gerarchia di memoria

Memoria formata da una MPV e una MGL:

la MPV contiene una copia di alcune celle della MGL;

quando la CPU chiede una particolare cella di memoria la richiesta va

ad entrambe le memorie:

• se il dato si trova nella MPV, viene passato

direttamente alla CPU;

• se il dato si trova nella MGL, viene anche caricato

nella MPV.

Ipotesi: distribuzione uniforme delle richieste

• la frequenza con cui si trova il dato cercato nella MPV (hit ratio)

sarà in media il 10% (1/10), in questi casi il tempo di accesso (hit

time) sarà pari a 1 unità;

• la frequenza con cui è necessario accedere alla MGL (miss ratio)

sarà in media il 90% (9/10), in questi casi il tempo di accesso (miss

penalty) sarà pari a 10 unità;

• il tempo medio di accesso sarà 0.1*1+0.9*10=9.1 unità!

Alessandro Di Nuovo

3939

Gerarchia di memoria

Sistema di

memoria

CPU

Memoria piccola

e veloce

Livello 1

Trasferimento

di dati

Livello 2

Memoria grande

e lenta

Alessandro Di Nuovo

40

Il principio di località

Località spaziale: quando si accede all’indirizzo

A, è molto probabile che gli accessi

successivi richiedano celle vicine ad A.

le istruzioni del codice vengono in genere lette da locazioni consecutive

della memoria;

gli accessi ad array o a strutture dati sono “vicini”.

Località temporale: quando si accede

all’indirizzo A, è molto probabile negli accessi

successivi si richieda di nuovo la cella A.

cicli di istruzioni accedono ripetutamente alle stesse locazioni di

memoria;

istruzioni vicine tendono ad utilizzare le stesse variabili.

Alessandro Di Nuovo

4141

Come si sfrutta la località

Diversi approcci a seconda del tipo di località:

località temporale:

i dati prelevati dalla MGL vengono conservati

nella MPV il più a lungo possibile;

località spaziale:

quando si copia un dato dalla MGL alla MPV, si

copiano anche i dati vicini (blocco).

La frequenza di successo (hit ratio – h) cresce

fino a superare il 99%:

in effetti h dipende da due caratteristiche

contrastanti:

la dimensione dei blocchi

un blocco grande sfrutta meglio la località spaziale;

quanti sono i blocchi in memoria

se c’è spazio per tanti blocchi un dato resta in

memoria più a lungo e può sfruttare più a lungo la

località temporale;

c’è anche il problema del costo della cache!

Alessandro Di Nuovo

4242

L’effetto della località

Effetto del principio di località sull’esempio di

prima:

tempo di accesso alla cache pari a 1 unità (TAC = 1);

tempo di accesso alla memoria (detto anche miss penalty, ovvero

penalità di fallimento) pari a 10 unità (TAM = 10);

frequenza di successo (hit ratio, h = 0.99);

frequenza di fallimento (miss ratio, m = 1 – h = 0.01);

tempo di accesso medio pari a:

TA = h * TAC + m * TAM

TA = 0.99 * 1 + 0.01 * 10 = 1.09

Alessandro Di Nuovo

43

La memoria centrale

Tecnologia elettronica (veloce ma volatile)

Gerarchia di memoria:

ai livelli più alti corrispondono le tecnologie

più veloci ma anche più costose

cache interna (Static RAM – SRAM)

cache esterna (SRAM)

memoria RAM

(Dynamic RAM – DRAM e sue varianti)

area di swap su memoria di massa

Alessandro Di Nuovo

44

Una gerarchia di memoria

Ottenuta per “generalizzazione”

dell’applicazione del principio di località e

tipicamente costituita da

1.

2.

3.

4.

5.

registri contenuti nella CPU (qualche KB)

cache (da circa 32KB a circa 4096KB)

memoria principale (da circa 512MB a qualche GB)

dischi fissi (da qualche centinaio di GB a qualche TB)

nastri magnetici e dischi ottici (da qualche centinaio di GB a

qualche TB per ogni supporto)

Man mano che ci si sposta verso il basso

nella gerarchia aumenta il valore dei

parametri fondamentali:

aumenta il tempo di accesso;

aumenta la capacità di memorizzazione;

ma diminuisce il costo per bit.

Alessandro Di Nuovo

45

RAM

Supporti esterni

tecnologia

magnetica

(HD esterni)

tecnologia

ottica

(CD, DVD)

tecnologia

elettronica

(flash disk)

Involucro esterno del calcolatore (case)

Cache II liv

Scheda madre (motherboard)

Cache I liv

Circuito Integrato (chip)

Registri

CPU

Una gerarchia di memoria

Disco fisso (hard disk)

tecnologia magnetica

Alessandro Di Nuovo

4646

La memoria Cache

Alessandro Di Nuovo

47

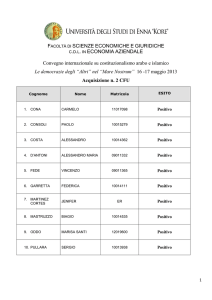

Caratteristiche dei diversi livelli

Livello

Capacità

Tempo di

accesso

Transfer rate

(GB/s)

Registri

~ 1 KB

~ 0.2 ns (1 ciclo

di clock)

–

Cache I livello

~ 32 KB

~ 0.4 ns (2/4

cicli di clock)

–

Cache II livello

~ 1/2 MB

~ 1/2 ns (5/10

cicli di clock)

~ 100

Cache III livello

~ 2/8 MB

~ 5 ns

~ 50

Memoria

centrale

~ 2/8 GB

~ 50 ns (1ª

parola richiesta)

~ 10 ns (parole

successive)

~ 5/10

Dischi interni

> 300 GB

~ 10 ms

0.15/0.6

Dischi esterni

> 300 GB

~ 10 ms

~ 0.05

Alessandro Di Nuovo

48

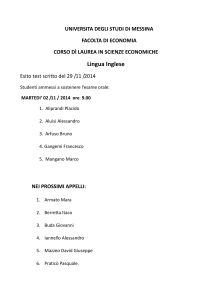

La memoria virtuale

Funzione del Sistema Operativo

Simula la presenza di maggiore memoria fisica utilizzando l’HD per

permettere a più programmi di essere caricati “contemporaneamente”.

Alessandro Di Nuovo

49