Front-End VLSI CMOS 0.35mm per

dispositivi SiPM mirato ad

applicazioni TOF con soglia

regolabile ed ampio range dinamico.

Davide Badoni – INFN Roma Tor Vergata

Collaborazione Altcriss-Sirad

1st Workshop su “Photon Detection” 13-14 giugno 2007

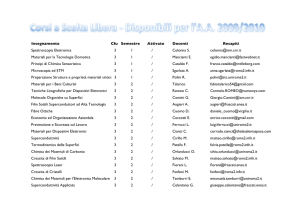

Sommario

L’ idea generale del presente progetto.

Caratterizzazione, studio e realizzazione del modello del SiPM (MEPHI

3x3 - 5625 pixels) finalizzato alla simulazione in un ambiente di

simulazione analogica (Spectre-Cadence) (SiPM del MEPHI)

Considerazioni sulla scelta del circuito di ingresso.

Il chip pilota.

Il canale analogico.

Risultati di simulazione.

Conclusioni.

I.N.F.N. Roma2

Davide Badoni

L’ idea generale del presente progetto

Generare un trigger quando un gruppo di fotoni colpisce il SiPM.

Trigger generato quando il segnale supera una soglia prefissata

regolabile.

Il range di regolazione della soglia copre tutto il range dinamico

del SiPM.

In caso di arrivo di gruppi di fotoni con rate bassa, vengono

selezionati gli eventi con intensità maggiore o uguale alla

corrispondente soglia.

I.N.F.N. Roma2

Davide Badoni

Modello semplificato del SiPM (1)

Singolo pixel

I.N.F.N. Roma2

Idark-pix tiene conto della corrente termica

temperatura e tensione di bias Vb.

Cd-pix: capacità di giunzione Vb profondità

dello strato di svuotamento.

La Rs-pix: resistenza ohmica per la limitazione nel

geiger mode.

Generatore di corrente Idark-pix: effetto del fotone

incidente: è stato scelto una forma quadra con una

fissata durata temporale T (molto breve).

Scegliendo differenti ampiezze I siamo in grado di

simulare diverse produzioni di carica Q(t)=I*T

guadagno del SiPM.

Davide Badoni

Modello semplificato del SiPM (2)

Le misure per ricavare i parametri possibili solo sull’array

completo di pixels.

Ipotesi:

approssimazione e riduzione: Parametri identici tra pixels. Stessa

struttura: parametri riscalati linearmente.

Modello

Array

Modello globale

I.N.F.N. Roma2

Davide Badoni

Modello semplificato del SiPM (3)

Misure al buio: i contributi

dei generatori di corrente

sono piccoli e si considerano

globalmente come una

corrente media.

Risposta al gradino per

stimare RS e Cd

L’andamento trovato è del

tipo:

1

Cd

Vb

I.N.F.N. Roma2

Davide Badoni

Modello semplificato del SiPM (4)

I.N.F.N. Roma2

MODELLO Array:

Impulso da singolo fotone

equivalente:

caricato su 50 W

caricato su 500 W

MODELLO Globale:

Impulso da singolo fotone

equivalente:

caricato su 50 W

caricato su 500 W

Davide Badoni

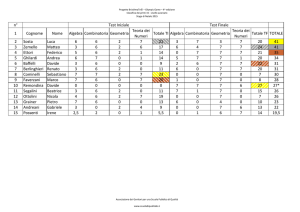

Parametri: linearità

Linearità dell’ampiezza di picco del segnale rispetto a n fotoni

incidenti: dipende dal numero M di pixels e n<M.

Il SiPM trattato M=5625 è lineare fino a circa 1000 pixels.

Guadagno tipico 106 Fissiamo 400 000 e- ovvero

64 fC/pixel.

FISSATA l’ impedenza di ingresso del preamplificatore che né

determina la costante di tempo

il valore di picco del segnale in corrente per 1 pixel vale è

una quantita’ K (volt o ampere) fissata.

I.N.F.N. Roma2

Davide Badoni

Parametri: range dinamico

40

Peak current (I) / k

n=2

n = 40

20

10

3

2

1

t

I.N.F.N. Roma2

Davide Badoni

Circuito di ingresso dell’amplificatore

per SiPM: vincoli e scelte

Range dinamico -- scelta di amplificatore in corrente

Velocità di risposta al fronte di salita.

Riduzione al minimo del recovery time del sistema:

Costante di tempo del circuito d’ingresso più bassa possibile.

Bassa impedenza Amplificatore di corrente

Esempio di possibile

accoppiamento

C

R

I.N.F.N. Roma2

Davide Badoni

Stadio di ingresso

Preamplificatore

Bassa impedenza

di ingresso

Chip prototipo pilota (1)

Implementazione in VLSI full-custom in tecnologia CMOS AMS 0.35μm

4 metalli di un front-and analogico per i SiPM.

Scopo del chip pilota è anche quello di verificare le caratteristiche della

catena analogica di preamplificazione-amplificazione.

Alcune peculiarità da mettere in evidenza:

Capacità di rivelazione di singolo fotone.

Range dinamico e linearità, legati alla saturazione del numero di pixel colpiti

(es. 1-1000 per il 3x3).

Elevate caratteristiche di timing (risoluzione temporale < 300 ps).

Guadagno elevato (ordine 106)

I.N.F.N. Roma2

Davide Badoni

Preamplificatore low-voltage

“Fully differential” in corrente (1)

SiPM

In +

Vb

RL

Differenziale A

Out +

Feedback

In -

I.N.F.N. Roma2

Differenziale B

Davide Badoni

Aumento della

banda

passante.

Out-

Diminuzione

dell’impedenza

di ingresso.

Immunità al

rumore di

modo comune

esterno.

Preamplificatore low-voltage differenziale in

corrente: schematico semplificato di un lato

del circuito

Vdd

Vdd

Ibf

Current In

Ib

Output feedback

Voltage

Out

Idea di base: Current amplifier “fully balanced” con current mirror.

Riduzione degli effetti negativi del mismatch tra i mosfets

I.N.F.N. Roma2

Davide Badoni

Preamplificatore low-voltage

differenziale in corrente

I.N.F.N. Roma2

Davide Badoni

Circuito di accoppiamento: coppia

differenziale

I.N.F.N. Roma2

E’ necessario ritornare al

single-ended perchè il

current comparator è uno

zero crossing single ended.

Si sfrutta la seconda uscita

in tensione per prelevare il

segnale da inviare ai buffer

di uscita.

Davide Badoni

Fast current comparator

I.N.F.N. Roma2

E’ uno zero crossing molto

veloce.

Lavora egregiamente con

piccole correnti ma anche per

correnti elevate.

La versione implementata è

più complessa ed elaborata di

questa di basa illustrata, per

ottenere maggiori prestazioni

in timing per basse correnti.

Davide Badoni

Pulse extender

Durata impulso in uscita regolabile.

I.N.F.N. Roma2

Davide Badoni

Chip prototipo pilota – schema generale

In+

Preamplificatore

differenziale

in corrente

In-

x1

x10

Double buffer

Out trigger

Pulse Extender

Accoppiamento

Discriminatore

a soglia

Lo schema a blocchi

rappresenta l’attuale

progetto di front-end

analogico per i SiPM in

cui ciascun canale

consiste di:

DAC in corrente

DIGITALE

Interfaccia

Controlli

I.N.F.N. Roma2

Preamplificatore fully

differential in corrente

Buffer di uscita in

tensione

Generatore di soglia

programmabile

Discriminatore in

corrente.

Registri soglia

Bias generators

Davide Badoni

Simulazioni: risultati preliminari:

prestazioni e parametri sensibili (1)

Effettuate simulazioni complete: TIPICA – CORNERS - MONTECARLO

Range dinamico di regolazione soglia:

160 uA per il massimo di 1000 pixels equivalenti regolabile a

step di 1 pixels (160 nA) con un valore minimo di 3 pixels.

Offset sulla soglia

Tempi di salita del segnale in ingresso al comparatore: circa 2 ns.

Delay (tra attraversamento soglia e start trigger)

Potenza dissipata: 16 mW

Jitter intrinseco stimato

I.N.F.N. Roma2

Davide Badoni

Simulazioni: risultati preliminari:

offset sulla soglia

Montecarlo

Corners: variazione temperatura 0-80 gradi C

Poiché l’offset può essere regolato indipendentemente per

ciascun canale e non c’è eccessivo drift in temperatura la

regolazione è efficace.

I.N.F.N. Roma2

Davide Badoni

Simulazioni: risultati preliminari: jitter

intrinseco.

Il jitter intrinseco è stato stimato con una analisi spettrale

del rumore intrinseco riportato in ingresso al comparatore

(~ 270 nA equivalenti)

Inoise

In+

Preamplificatore

differenziale

in corrente

In-

x1

x10

Double buffer

Out trigger

Pulse Extender

Accoppiamento

Discriminatore

a soglia

DAC in corrente

Il risultato è un valore massimo compreso tra 20ps e 50ps nelle

varie condizioni di simulazione

I.N.F.N. Roma2

Davide Badoni

Simulazioni: risultati preliminari: Soglia

massima impostata vs. segnale rivelato

I.N.F.N. Roma2

Soglia massima impostata

per ottenere il trigger in

funzione dell’ampiezza

dell’impulso di corrente

(n. di pixels).

Davide Badoni

Layout

I.N.F.N. Roma2

Davide Badoni

Conclusioni e prossimi passi

Il chip implementa 8 canali con un minimo di elettronica di readout.

I risultati della simulazione schematico sono soddisfacenti.

Il disegno del layout è appena terminato.

Si utilizza il circuito EUROPRACTICE (Multiwafer projects), l’area di

silicio prevista è di 10 mmq

Il run previsto è quello di luglio.

I test che sarà possibile attuare su questo prototipo permetteranno di

aggiustare e consolidare il tiro sulle scelte circuitali in atto.

I.N.F.N. Roma2

Davide Badoni