I.T.I.S. Santhià – Dipartimento di Informatica

Microprocessori per P.C.

Modulo didattico

“L’Hardware del P.C.”

Ultima revisione 07 gennaio 2005

Autore M. Lanino

Come opera la CPU

La progettazione di un processore è un insieme di trucchi ingegneristici e di

avanzate tecniche di costruzione, che permettono di stipare in pochi mm

quadrati milioni di transistor.

Osservando con occhio distaccato un

computer, si nota come questo non sia altro

che una macchina in grado di leggere

istruzioni, decodificarle ed eseguirle. Se il

comando in esecuzione necessita di

recuperare o immagazzinare alcuni dati, il

computer ricerca la locazione per i dati e li

sposta.

Possiamo dividere queste operazioni in una serie di passaggi intermedi.

I passi di funzionamento

Possiamo quindi appoggiarci a questo semplice schema per analizzare

anche le Cpu più complicate. I cinque stadi possono essere eseguiti

completamente per una singola istruzione prima di affrontarne una

nuova. La complessità delle Cpu inizia nel momento stesso in cui si cerca

di superare questo limite.

Accesso alle istruzioni

Un'istruzione codificata viene letta dal sottosistema di accesso alla

memoria ad un indirizzo (locazione) determinato da un contatore di

programma (Program Counter, PC). In questa analisi trattiamo la

memoria come un oggetto che affianca l'unità di esecuzione della Cpu.

Decodifica dell’istruzione

Dopo che l'istruzione codificata è stata letta, viene tradotta in comandi di

controllo che possono essere eseguiti dai circuiti logici del processore. Ogni "codice

operazione" (Opcode) rappresenta una differente istruzione e istruisce la macchina

ad operare in modi diversi. Incapsulate nelle Opcode (o immagazzinate nei Byte

seguenti all'istruzione, detti operandi) trovano posto informazioni di indirizzamento

o dati che devono essere processati immediatamente. Le informazioni aggiuntive

presenti nelle Opcode possono rappresentare un nuovo indirizzo che deve

essere caricato nel Contatore di Programma (branch address, indirizzo di

salto) o una locazione di memoria dati (caricare o salvare).

Esecuzione

Nello stadio di esecuzione la macchina esegue l'operazione comandata

dall'istruzione.

Questa

potrebbe

essere

un'operazione

matematica

(moltiplicazione, addizione, ecc.) o un'operazione per muovere alcuni dati. Se

l'istruzione implica l'azione su dati in memoria il processore deve calcolare un

"indirizzo effettivo" (Effective Address, EA); questo rappresenta l'attuale

locazione dei dati nel sottosistema di memoria, calcolato sullo sfasamento

(spiazzamento) degli indirizzi o risolvendo riferimenti indiretti.

Accesso ai dati

A questo livello vengono inviati gli Indirizzi Effettivi al sottosistema di

memoria, di modo che le istruzioni possano ricevere i dati di cui necessitano o

immagazzinare dati ad indirizzi specifici.

Write Back

Non appena il processore ha condotto a termine l'esecuzione dell'istruzione, dopo

l'eventuale lettura di dati in memoria, i risultati vengono scritti nei registri di

destinazione (se previsto).

Modelli diversi di CPU

Il modello che abbiamo appena presentato sembra molto semplice, ma in realtà il suo

funzionamento si complica molto quando si trova ad operare con lo schema di

indirizzamento di un processore x86. Questo tipo di processore è di tipo "registromemoria" (register-memory); ovvero presenta un'architettura in cui anche le istruzioni

della Alu (Aritmetic Logic Unit, Unità Logico Aritmetica) possono accedere alla memoria.

In contrapposizione l'architettura Risc (Reduced Instruction Set Computing) permette

soli comandi di lettura e scrittura per lo spostamento di dati; questo tipo di architettura

è denominata "registro-registro". Le istruzioni Cisc (Complex Instruction Set

Computing) vengono infatti tradotte in istruzioni del tipo Risc. Queste consentono una

più facile ottimizzazione dell'hardware e possono essere eseguite a una frequenza più

elevata.

L'approccio di tradurre internamente alla Cpu le istruzioni Cisc in

istruzioni Risc ha permesso all'architettura x86 di resistere

all'avanzata dell'architettura puramente Risc.

Il ruolo della memoria

Sia lo stadio di accesso alle istruzioni che quello di accesso ai dati necessitano di

appoggiarsi alla memoria. La ricerca di un'ottimizzazione dell'accesso alla memoria

ha portato già nel 1940 al modello di accesso denominato Architettura Harvard

(in questo schema di funzionamento la memoria viene suddivisa in due sezioni

distinte: una per le istruzioni e una per i dati; in questo modo ogni stadio ha un

accesso dedicato alla sua sezione).

Per rendere più semplice ai programmatori la realizzazione del software, la maggior

parte degli indirizzi sono "indirizzi virtuali" , che permettono di ottenere grandi blocchi

lineari di memoria. Gli indirizzi virtuali vengono poi tradotti in "indirizzi fisici" riferiti

alla effettiva memoria del computer. Nella quasi totalità dei chip x86, le memorie cache

contengono dati di memoria che sono indirizzati con indirizzi fisici. Prima di accedere alla

cache, gli indirizzi virtuali vengono tradotti all'interno del TLB (Translation Look-aside

Buffer).

Se l'indirizzo virtuale richiesto dalla Cpu non è presente nella tabella TLB, evento

denominato "TLB mancato" , allora la tabella deve essere aggiornata in base a una

tabella più grande presente nella memoria centrale; l'operazione di accesso alla

memoria centrale comporta però un notevole rallentamento.

La Pipeline

I cinque stadi possono essere processati completamente per una singola istruzione

prima di affrontarne una nuova. La complessità delle Cpu inizia nel momento stesso in

cui si cerca di superare questo limite.

Invece di attendere che una singola istruzione abbia completato tutti e cinque

gli stadi del nostro modello, è possibile inviare al primo stadio una nuova

istruzione non appena la precedente sia passata al secondo stadio. Il

meccanismo della pipeline è quello alla base di una catena di

montaggio; ogni stadio della pipeline è paragonabile ad un segmento

della catena di montaggio.

Con questo nuovo approccio il processore del nostro schema base è capace di elaborare

contemporaneamente cinque istruzioni, mantenendo pieni tutti e cinque gli stadi della

pipeline. In questo modo la Cpu processa cinque istruzioni in parallelo,

riferendosi al parallelismo a livello di istruzione (ILP, Instruction Level

Parallelism). Il microprocessore opera, in questo modo, cinque volte più

velocemente.

I rischi di pipeline

Quelle che si intravedono sono situazioni denominate rischi di pipeline (pipeline

hazard), e il loro effetto è uno stallo del processo di esecuzione. Esistono

principalmente tre tipi di pericoli:

• Il primo è un rischio sui dati che consiste nel cercare di usare dati ancora non

disponibili, generalmente causato da una dipendenza di dati.

• Il secondo è un rischio sul controllo, generato dalla presenza nella pipeline di

istruzioni che risiedono dopo una diramazione del codice.

• L'ultimo è un rischio di struttura, ovvero un conflitto di risorse, che accade in

presenza di una richiesta da parte di istruzioni differenti della stessa risorsa

hardware (registri); un esempio potrebbe essere la necessità di utilizzare la

stessa locazione di memoria per dati e istruzioni nello stesso momento.

La riduzione dei rischi

Esistono diversi accorgimenti per ridurre il rischio di stalli nella pipeline.

Nella pratica l’attuale schema di funzionamento della CPU comporta l’insorgere

di questi stalli.

Se un’istruzione provoca questa situazione, l’esecuzione di questa

viene bloccata, mentre le istruzioni che si trovano negli stadi successivi

procedono lungo la pipeline; quella che si crea è una sorta di bolla tra le

istruzioni bloccate e quelle che procedono lungo la catena di montaggio.

Quando l’istruzione bloccata riprende il suo percorso, la bolla viene spinta

lungo la fine della pipeline.

CPU superscalari

La suddivisione in stadi permette di eseguire le istruzioni più velocemente;

l’aumento degli stadi della pipeline comporta un maggiore rischio di stalli, ma

consente di incrementare le frequenze di funzionamento. I processori x86 che

verranno analizzati possiedono tutti pipeline con un numero di stadi superiore a 5.

Ad esempio nel caso di Pentium 4 questa tecnica prende il nome di “hyperpipelining”.

In un’architettura superscalare, vengono aggiunte risorse hardware

per permettere un parallelismo di esecuzione: un esempio può essere

la presenza di due pipeline distinte all’interno di una stessa CPU.

32 o 64 bit

La maggior parte dei processori dei Pc con i quali oggi lavoriamo (tutti i P4, i Celeron, gli

Athlon XP, molti Sempron...) si basano sul set di istruzioni denominato x86 o IA-32 (IA

è l'acronimo di Intel Architecture), dove il numero 32 indica la capacità della Cpu di

operare con dati e indirizzi ampi 32 bit.

La potenza di calcolo, misurata in termini di istruzioni eseguite per ciclo di clock (Ipc

ovvero instructions per clock), può essere incrementata in diversi modi:

•incremento della frequenza di funzionamento (Clock), ovvero il ritmo con il

quale sono scandite le operazioni all'interno del processore

•Particolari tecniche di elaborazione del codice x86 (previsione dei salti,

esecuzione speculativa, struttura a pipeline, per citarne alcune)

La richiesta di potenza da parte del software ha da qualche anno iniziato a

percorrere anche altre strade: utilizzare architetture a 64 bit.

Architettura a 64 bit

Progettare una CPU a 64bit non è cosa da poco; si può operare secondo seguendo

due strade diametralmente opposte:

1.

Progettazione ex-novo, senza cioè alcun riferimento nè compatibilità con il

vecchio mondo dei 32 bit. Una CPU di questo tipo necessita di S.O. e SW in

versione 64 bit.

2.

Progettazione che mantenga la compatibilità con la vecchia tecnologia. Una CPU

di questo tipo deve poter leggere indifferentemente SW scritto con codice a 32 o

a 64 bit e poter utilizzare S.O. Standard.

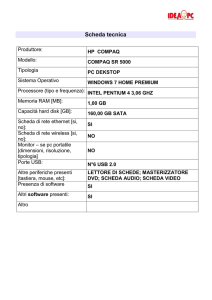

Le CPU di Intel

Anche per il 2005 la CPU di punta di Intel per sistemi di

fascia desktop sarà Pentium 4, mentre per i sistemi entrylevel sarà Celeron D. Per la fascia workstation e server la

cpu di Intel sarà Xeon. La tabella che segue fa il punto della

situazione, per districarsi meglio fra modelli e versioni delle

cpu menzionate.

In figura una nuova CPU Intel Pentium4 nel

nuovo formato Socket 775

Facciamo il punto

CPU

Socket

Package

Passo

Prod.

Freq.

Max

interna

Freq.

di BUS

Consumo

Tensione

alimentaz.

Core

Cache

L1/L2/L3

Data

introduz.

Celeron

478

mPGA

130 nm

2,8 GHz

400

MHz

68,4 W

1,5 V

Northwood

8K/128K

15/05/02

Celeron D

478

mPGA

90 nm

2,93 GHz

533

MHz

nd

nd

Prescott

16K/256K

24/06/04

Pentium 4

478

mPGA

130 nm

3,4 GHz

800

MHz

89 W

1,55 V

Northwood

c

8K/512K

06/01/02

Pentium 4

478

mPGA

90 nm

3,4 GHz

800

MHz

103 W

1,55 V

Prescott

16K/1M

01/02/04

Pentium 4

LGA775

LGA

90 nm

3,8 GHz

800

MHz

>103 W

1,425 V

Prescott

16K/1M

01/02/04

Xeon

603

mPGA

130 nm

3 GHz

400

MHz

85 W

1,50 V

Prestonia

8K/512K

27/01/02

Xeon

604

mPGA

130 nm

3,2 GHz

533

MHz

110 W

1,45 V

Prestonia B

8K/512K

18/11/02

Xeon

604

mPGA

90 nm

3,6 GHz

800

MHz

nd

1,40 V

Nocona

16K/1M

28/07/04

Xeon MP

604

mPGA

130 nm

3,0 GHz

400

MHz

97 W

1,475 V

Gallatin

8K/512K/2M

04/11/02

Situazione aggiornata al gennaio 2005 – Fonte PC Professionale - Mondadori

Architettura Net-burst di P4

L 'architettura NetBurst

I cambiamenti architetturali che si annidano sotto la dicitura

NetBurst consistono in una pipeline più profonda di quelle

attualmente diffuse, in una nuova architettura dei bus, maggiori

risorse di esecuzione e cambiamenti al sottosistema della

memoria.

La pipeline del Pentium 4 consiste di 31 stadi (nella versione core

Prescott), a differenza dei "soli" 10 stadi di cui disponeva

l’architettura del Pentium III. Uno degli elementi interessanti della

nuova architettura del Pentium 4 e la presenza di due stadi

dedicati a instradare i dati all'interno del chip.

Intel ha dovuto lavorare specialmente per evitare che si verifichino stalli della

pipeline; se una pipeline così profonda dovesse essere svuotata di frequente si

avrebbe un rapido degrado delle prestazioni, pur disponendo di una frequenza di

clock molto elevata.

Pipeline e frequenza di clock

Eventuali stalli che necessitino il completo svuotamento della profonda pipeline del

Pentium 4, comportano un notevole impatto sulle prestazioni. In questi casi i

benefici di una pipeline profonda vengono persi e un disegno più semplice potrebbe

risultare più performante. Il vantaggio della pipeline a più stadi è di eseguire

un minor lavoro ad ogni passo; in questo modo la lunghezza dei cicli può

essere ridotta, consentendo così di aumentare la frequenza di clock e

quindi la velocità di esecuzione. Di conseguenza una pipeline profonda

necessita di funzionare a frequenze più alte per eseguire la stessa quantità di lavoro

di una pipeline più corta funzionante ad una frequenza inferiore.

L'impiego di una pipeline profonda a molti stadi consente di avere in

esecuzione più istruzioni nello stesso momento; questo consente,

analizzando le istruzioni in esecuzione, di ricercare quelle che possono

essere eseguite in parallelo. Il Pentium 4 è capace di mantenere 126 istruzioni

in attesa, mentre attende che altre istruzioni completino il loro ciclo.

I pro e i contro

Va da sé che la pipeline profonda del P4 lo rende sensibile al codice molto

ramificato, come può essere quello presente negli applicativi di produttività

personale, non ottimizzati, mentre risulta molto performante nell’esecuzione di

processi sequenziali, come ad esempio la codifica video.

Riassumendo:

Pipeline molto lunghe:

uno dei motivi che spiega le elevate frequenze di clock disponibili per i

processori Pentium 4 è proprio la lunghezza delle pipeline. Ovviamente, più lunghe sono le pipeline di

calcolo, meno ne si potrà completare nell'unità di tempo. Al contrario, però, la maggior lunghezza della

pipeline permette di ottenere frequenze di lavoro più elevate e, di conseguenza, un maggior numero di

operazioni eseguite nell'unità di tempo.

Unità di Branch Prediction:

l'utilizzo di pipeline molto lunghe permette di salire di clock molto

facilmente a parità di processo produttivo, ma cresce il rischio di perdere fasi di calcolo e generare bolle

all'interno della pipeline, qualora parte dell'operazione non vada a buon fine. Un'unità di Branch Prediction

molto avanzata permette di minimizzare questi rischi e ottimizzare, pertanto, tutte le fasi dell'esecuzione

delle istruzioni.

Rapid Execution Engine:

due delle unità ALU (Arithmetic Logic Units) integrate nei processori

Pentium IV operano ad una frequenza di lavoro doppia rispetto a quella di clock. Le prestazioni di queste

unità ALU permettono di minimizzare gli effetti negativi dati dalla lunghezza delle pipeline, soprattutto

nell'esecuzione di calcoli interi.

Hardware Prefetch:

il processore è in grado di prevedere quale dato verrà richiesto all'interno

della pipeline per l'esecuzione delle operazioni. Il dato che si ritiene verrà utilizzato viene preso e

memorizzato nella memoria cache, così che sia immediatamente disponibile non appena se ne richiede

l'impiego. Ovviamente, se la previsione è corretta se ne ottiene un vantaggio in termini di prestazioni

complessive. Qualora invece essa non lo sia si otterrà uno spreco sia di memoria cache sia di bandwidth

(banda passante) della memoria.

E ancora …

Bus Quad Pumped:

il bus di sistema dei processori Pentium IV opera a 100 (200) Mhz ma è del

tipo quad pumped, cioè offre un quantitativo di bandwidth equivalente a quello di un sistema con bus a

400 (800) Mhz, quindi pari a 3,2 (6,4) Gbytes al secondo come massimo teorico.

SSE2:

il set di istruzioni multimediali Mmx e SSE, introdotto con i processori Intel Pentium III, è

stato ulteriormente migliorato e ora prende il nome di SSE2. Qualora si utilizzi codice ottimizzato,

questo set di istruzioni 3D pemette un aumento delle prestazioni in modo particolare con applicazioni di

grafica professionale o che richiedono numerose elaborazioni 3D.

Conclusioni sul P4

Il disegno del Pentium 4 è stato studiato per scalare verso l'alto le frequenze di

funzionamento; non è infatti un caso che attualmente il processore Intel sia l'unico

ad aver raggiunto i 3,8 GHz. A causa della sua particolare architettura, molto

sensibile ai "cache miss", ovvero alle situazioni in cui il dato richiesto non sia

presente nella cache, diventa un'operazione critica aumentare la memoria cache e

quindi i tempi di latenza per la sua lettura. L'aumento della frequenza di

funzionamento associato ad una corretta compilazione del codice, rende questo

microprocessore molto competitivo, soprattutto nelle versioni a core Northwood C

(130 nm) e Prescott (90 nm), dotati di un quantitativo maggiore di cache (8 e 16

KB per L1 e 512 KB e 1 MB per L2) rispetto alle versioni precedenti e capaci di salire

ulteriormente in frequenza. Come per AMD, anche Intel ha dovuto modificare

package (vedi figura) e relativi socket delle proprie cpu per venire incontro ad

accresciute richieste di potenza dissipabile e di numero di pin disponibili. Così il

socket775 sta soppiantando il vecchio 478 e il micro pin grid array (micro letto di

chiodi) ha lasciato il posto al land grid array (distesa di piazzole).

CPU Intel a 64 bit

La scelta strategica di Intel cira le CPU a 64 bit è stata per molti anni orientata al taglio

completo dei ponti con la vecchia architettura X86-32. Le CPU della categoria Itanium non

sono infatti compatibili con l’attuale codice a 32 bit. Se da un lato questa scelta assicura la

possibilità di creare ex-novo un nuovo standard di CPU, dall’altro costringe sviluppatori e

mercato a riscrivere completamente tutto il SW finora utilizzato

Per iniziare a colmare il gap rispetto ad AMD per quanto riguarda la tecnologia a

64 bit nel settore workstation e desktop, Intel ha recentemente (Agosto 2004)

messo in commercio cpu Xeon core Nocona in grado di supportare la tecnologia

EM64T (Extended Memory 64 Technology) in grado di utilizzare codice con

estensione a 64 bit. I primi PC ad esserne dotati sono usciti in dicembre. Intel,

suo malgrado, ha dovuto rivedere i suoi piani di sviluppo e di fronte alla

imminente uscita di Windows XP in versione 64 bit e alle versioni a 64 bit già in

commercio di Linux, ha dovuto estendere la propria offerta anche alle CPU a 64

bit compatibili con il codice a 32.

Conclusioni sul P4

Il disegno del Pentium 4 è stato studiato per scalare verso l'alto le frequenze di

funzionamento; non è infatti un caso che attualmente il processore Intel sia l'unico ad

aver raggiunto ad oggi i 3,2 GHz.

A causa della sua particolare architettura, molto sensibile ai "cache miss", ovvero alle

situazioni in cui il dato richiesto non sia presente nella cache, diventa un'operazione

critica aumentare la memoria cache e quindi i tempi di latenza per la sua lettura.

L'aumento della frequenza di funzionamento, associata ad una corretta compilazione del

codice rende questo microprocessore molto competitivo, soprattutto nelle versioni a

core Northwood (oggi giunte alla revisione C), realizzate con tecnologia a 0,13

micron, dotate di un quantitativo maggiore di cache (8 KB L1 e 512 KB L2) e capaci di

salire ulteriormente in frequenza nei prossimi mesi.

Le CPU di AMD

La CPU di punta di AMD per il 2005 sarà sempre Athlon, nelle sue diverse

varianti, cui si affiancano Sempron, dedicato ai sistemi entry-level e Opteron,

per gli ambienti workstation-server.

Per quanto riguarda l’offerta a 32 bit, le CPU, utilizzanti il socket A, sono Athlon

XP , Athlon MP e Sempron.

Per quanto riguarda il mercato 64 bit AMD commercializza Athlon64 e Sempron

(core Clawhammer) su socket 754 per il mercato desktop e Athlon64 e FX su

socket 939 per il mercato workstation. Questi ultimi modelli sono caratterizzati da

un controller integrato della memoria dotato di doppio canale a (64 bit x2).

Maggiori informazioni nelle slides successive

AMD Athlon

L'architettura del processore Athlon è più simile alla nostra prima

analisi di macchine con esecuzione speculativa e fuori ordine. Esso

può eseguire simultaneamente 9 istruzioni di tipo Risc (denominate

OP da AMD).

La scelta di AMD è stata di implementare una cache L1, di primo livello, di grosse dimensioni. I 128

KByte della L1, con associatività a due vie, sono suddivisi in eguale maniera per le istruzioni e per i

dati. La sezione L1 delle istruzioni ha un canale da 64 byte con 64 byte sequenziali di prefetch. La

parte di L1 destinata ai dati fornisce una seconda porta di accesso per evitare l'insorgere di rischi di

struttura generati da un disegno superscalare. La cache L2 è di 512 KByte unificati con associatività

a 16 vie ed è supportata dal veloce bus EV6. Le ultime versioni (core Thoroughbred e Barton),

supportano anche il prefetching e sono costruite con processo a 0,13m.

Per trattare la complessità del set di istruzioni x86-32, il , processore AMD effettua

una decodifica parziale delle istruzioni non appena queste vengono trasferite nella cache

L1. Alcuni bit extra posti all'inizio e alla fine delle istruzioni di lunghezza variabile

permettono una migliore e più rapida identificazione da parte delle unità di previsione

(prefetcher e predictor).

La pipeline dell'Athlon assomiglia molto al flusso descritto per il nostro modello base

di computer. I processi di accesso alle istruzioni e di decodifica di queste sono divisi in 6

stadi dalla pipeline.

Dentro Athlon XP

Tabella riassuntiva (gen. 2005) AMD

CPU

Socket

Package

Passo Prod.

Freq. Max

inter

na

Sempron

A

OPGA

130 nm

2 GHz

333 MHz

62 W

Sempron

A

OPGA

130 nm

2 GHz

333 MHz

Athlon XP

A

OPGA

130 nm

2,2 GHz

Sempron

754

OPGA

130 nm

Athlon 64

754

OPGA

Athlon 64

939

Athlon 64

Tensione

alimen

taz.

Data

intro

duz

Core

Cache

L1/L2/L3

1,60 V

Thoroughbred

128K/256K

27/07/04

62 W

1,60 V

Barton

128K/512K

17/09/04

400 MHz

77 W

1,60 V

Barton

128K/512K

10/02/03

1,8 GHZ

800 MHz

62 W

1,50 V

Clawhammer

128K/256K

27/07/04

130 nm

2,4 GHZ

800 MHz

89 W

1,50 V

Clawhammer

128K/1M

23/09/03

OPGA

130 nm

2,4 GHZ

1000 MHz

89 W

1,50 V

Newcastle

128K/512K

21/06/04

939

OPGA

130 nm

2,4 GHZ

1000 MHz

89 W

1,50 V

Clawhammer

128K/1M

14/10/04

Athlon 64FX

939

OPGA

130 nm

2,6 GHZ

1000 MHz

104 W

1,50 V

Clawhammer

128K/1M

23/09/03

Athlon MP

A

OPGA

130 nm

2,13 GHZ

266 MHz

60 W

1,65 V

Thoroughbred B

128K/256K

10/06/02

Athlon MP

A

OPGA

130 nm

2,13 GHZ

333 MHz

60 W

1,6 V

Barton

128K/512K

06/05/03

Opteron

940

CPGA

130 nm

2,4 GHz

400 MHz

85 W

1,55 V

Sledgehammer

128K/1M

22/04/03

OPGA = Organic Pin Grid Array

Freq. di

BUS

Consumo

Conclusioni su Athlon

Quello che emerge dall'analisi è che l'architettura dell'Athlon è più

tradizionale di quella introdotta dà Intel con il Pentium 4 e risulta più vicina

allo schema base di un sistema per l'esecuzione di istruzioni fuori ordine,

presentando una pipeline con meno stadi di quelli del Pentium 4.

Athlon mostra prestazioni superiori Pentium 4 a parità di frequenza di

clock in molte applicazioni; tuttavia Pentium 4 dispone attualmente

(gennaio 2005) di circa 1.2 GigaHertz di vantaggio in termini di clock, ciò

basta a concedergli prestazioni assolute migliori rispetto alle CPU a 32 bit

di AMD.

AMD e i 64 bit

Scelta di AMD:

AMD è stata la prima fra le case produttrici a sviluppare CPU a 64bit, sempre con il

vincolo della totale compatibilità con il codice X-86 (IA-32) di Intel. Dal 2003 sono in

commercio CPU di tipo Opteron e Athlon64 dotate di tecnologia a 64 bit per ambienti

server-workstation e desktop.

In questo settore il gap con Intel è grande, perchè due anni di vantaggio sono molti.

L’Athlon 64

Come già anticipato, AMD produce da almeno due anni CPU a 64 bit. Attualmente la

produzione è rappresentata dai seguenti modelli:

Athlon 64 – socket 754

Sempron – socket 754

Athlon 64 – socket 939

Athlon 64 FX – socket 939

Opteron

Modelli da 2800+ (1,8 GHz) a 3700+ (2,4 GHz). L1

128KB, L2 512KB. Controller della memoria a singolo

canale da 64 bit integrato nella CPU

Modello 3100+ (1,8 GHz), simile al modello precedente,

ma con solo 256 KB di L2.

Modelli da 3500+ (2,2 GHz) a 4000+ (2,4 GHz). L1

128KB, L2 1MB. Controller della memoria a doppio

canale (64+64 bit) integrato

Modello FX-55 (2,6 GHz) e caratteristiche simili al

precedente modello.

Modelli con model number da 140 (1,4 GHz) a 850 (2,4

GHz). L1 128 KB, L2 1 MB. Possibilità di funzionamento

multi CPU.

Intel Centrino

Centrino non è una CPU, ma un insieme di tecnologie rivolte al mondo dei

PC portatili.

L’architettura Centrino di Intel è stata progettata per equipaggiare i

notebook in modo da fornire a questi spiccate doti di maneggevolezza ed

autonomia. I notebook Centrino sono caratterizzati da: leggerezza, consumi

ridotti, quindi elevata autonomia e connettività facilitata.

Per architettura Centrino si intende un insieme di tre componenti:

v Processore Pentium M

v Chipset i855 nelle versioni con o senza grafica integrata

v Scheda di rete Wi-Fi Intel Pro/Wireless 2100 su slot mini-PCI

Architettura Centrino

Dati tecnici del Centrino

Conosciuto con il nome in codice BANIAS, il core del Pentium M è stato sviluppato in Israele.

Si è lavorato apportando modifiche sostanziali al core del Pentium III ottenendo un

processore estremamente efficiente che allo stesso tempo consuma poco.

La particolarità della nuova architettura evolve su binari opposti rispetto a Pentium4:

la tecnologia di funzionamento delle micro-Ops accorpa le microistruzioni interne prima del

passaggio alle unità di elaborazione, aumentando così l’efficienza per unità di clock. Una

previsione dei salti (branch prediction) ottimizzata è anch’essa di aiuto, ma un ruolo chiave lo

giocano gli accorgimenti impiegati nell’accesso alla memoria cache di II livello, di ben 1

Mbyte.

Con un disegno delle celle ottimizzato per limitare i consumi, il processore è in grado di

attivare solo la riga necessaria alla lettura volta per volta. Una versione migliorata dello

speed-step consente di variare dinamicamente frequenza e tensione di alimentazione (che

risulta compresa fra 0,85V e 1,5V). Attualmente (nov.2003) il PentiunM è disponibile in

volumi con frequenze di clock che vanno da 1,3 fino a 1,7 GHz con passi di 100MHz.

Esistono poi le versioni LV (Low voltage) e ULV (Ultra low voltage) con assorbimento

elettrico ancora inferiori.

Informazioni sul chipset

Il chipset i855 è disponibile in due versioni:

v

PM che è priva della grafica integrata e pertanto dispone di connessione

AGP 4x verso un chip grafico esterno avanzato, tipicamente ATI o Nvidia.

v

GM che dispone di sottosistema grafico integrato Intel Estreme Graphics 2,

che utilizza dinamicamente parte della memoria di sistema per la grafica. Ciò

permette di ridurre i costi finali ed il consumo energetico in cambio di prestazioni

grafiche più modeste.

Il chipset supporta memoria DDR266 fino a 2 GB e la versione i855PM anche la

DDR333. Il SB è l’ ich4-M e mette a disposizione un controllere Eide ATA100 e la

connettività USB2.0. L’interfaccia di rete Ethernet può essere di Intel o di terze

parti, mentre la scheda Wireless è la Intel Pro/Wireless 2100 su bus mini-PCI,

quindi facilmente upgradabile in futuro, che supporta lo standard 802.11b e g.

Modelli Centrino in commercio

Commercializzato in volumi dalla fine del 2003, il nuovo core Dothan, successore di

Banias, è implementato con processo produttivo a 90 nm, tecnologia “strained silicon”

e cache L2 di 2 MB (140 milioni di transistors). Il chipset di riferimento sarà i855GME

con supporto delle DDR333 e DDRII, al serial ATA e a PCI express ed Express-card. Il

prossimo Centrino disporrà anche di un nuovo sottosistema audio integrato

denominato Azalia, che sostituirà il datato AC’97 e supporterà l’audio THX e Dolby

Digital 5.1, 6.1 e 7.1.

Il Pentium M core Dothan viene identificato, come già da tempo fa AMD, con un

model number e precisamente:

Pentium M 725 è la versione a 1,6 GHz

Pentium M 735 è la versione a 1,7 GHz

Pentium M 745 è la versione a 1,8 GHz

Pentium M 755 è la versione a 2,0 GHz

Pentium M 765 è la versione a 2,1 GHz