Calcolatori:

La Macchina di Von Neumann

1

La Macchina di Von Neumann

• L’architettura della maggior parte dei Calcolatori è

organizzata secondo il modello della cosiddetta

Macchina di Von Neumann.

• John Von Neumann è stato il ricercatore americano che,

sollecitato dall’esercito americano durante il corso della

seconda guerra mondiale, dedicò i suoi studi alla

realizzazione dei primi Calcolatori Elettronici.

• Grazie ai suoi studi Von Neumann nel 1946 realizzò

ENIAC (Electronic Numerical Integrator and Computer).

• ENIAC era in grado di effettuare 300 moltiplicazioni al

secondo, ed occupava una stanza lunga più di 30 metri.

2

I Componenti fondamentali

• L’Unità di Elaborazione (CPU, Central Processing Unit):

contiene i dispositivi elettronici in grado di acquisire,

interpretare ed eseguire le istruzioni di un Programma.

• La Memoria Centrale: è il dispositivo dove si trovano le

informazioni necessarie all’esecuzione di un Programma,

ossia istruzioni e dati.

• Dispositivi di Input/Output o Periferiche: permettono di

trasferire informazioni tra memoria centrale e/o CPU e

l’ambiente esterno (es. schermo, tastiera, memoria di

massa).

• Bus di sistema: opera il collegamento tra i vari

componenti.

3

I Componenti fondamentali

CPU

Memoria di massa

Schermo/tastiera

Interfaccia di I/O

Interfaccia di I/O

Memoria

(centrale)

BUS

NOTA: la memoria di massa (tra cui il Disco fisso) e altri

dispositivi periferici di uso comune non rientrano tra i

componenti fondamentali, mentre ne fanno parte solo le

relative interfacce. L’ENIAC aveva un sistema a schede

perforate per l’I/O dei dati.

4

Principi di funzionamento

• L’unità di elaborazione (CPU) coordina le varie

attività, in particolare estrae istruzioni dalla memoria,

le decodifica comprendendo il loro significato e le

esegue.

• I contenuti della memoria sono indirizzati in base alla

posizione, indipendentemente dal tipo di dato o

istruzione contenuto.

• Le istruzioni vengono eseguite in modo strettamente

sequenziale (principale limite del modello di Von

Neumann).

5

Memoria centrale

• Affinché un Programma possa essere eseguito deve

necessariamente risiedere in Memoria centrale.

• La Memoria centrale è composta da un certo numero di

celle (o locazioni o posizioni), ciascuna delle quali può

memorizzare un’informazione in forma binaria.

• Le celle hanno generalmente dimensione di un byte (8

bit) o di una parola quindi, a seconda del tipo di

Calcolatore, 16, 32 o 64 bits.

• Le celle sono numerate con numeri interi da 0 a N-1, con

N il numero di celle totali.

• Ciascuna cella è individuata univocamente da un numero

intero che è il suo indirizzo.

6

Memoria centrale

• La capacità della Memoria (non solo quella centrale) si

misura in byte:

– Kilobyte (Kb) = 210 Byte = 1024 Byte.

– Megabyte (Mb) = 220 Byte = 1048576 Byte.

– Gigabyte (Gb) = 230 Byte = 1073741824 Byte

• Il numero di bit che costituiscono l’indirizzo definisce la

dimensione massima della memoria indirizzabile (lo spazio

di indirizzamento): con k bit si possono indirizzare 2k celle

diverse.

• E’ realizzata con circuiti a semiconduttori (memoria

elettronica) ed è volatile, ossia perde le informazioni in

essa contenute quando non alimentata (es. quando il

7

calcolatore viene spento).

Componenti della Memoria

centrale

• Oltre all’insieme delle celle, la Memoria centrale è

costituita da:

– Registro Indirizzi: contiene l’indirizzo della cella di

memoria che vogliamo leggere o scrivere.

– Decodificatore di indirizzi: è il dispositivo che

individua la cella rappresentata nel Registro indirizzi.

– Registro Dati: contiene l’informazione che deve essere

scritta nella cella o che è stata letta dalla cella

individuata dal Decodificatore di indirizzi.

• Il tempo necessario ad accedere ad una cella di memoria

è costante, ossia è indipendente dall’indirizzo della cella a

cui si accede (memoria RAM, Random Access Memory).

8

Altri tipi di Memoria

• Read Only Memory (ROM): memoria sempre a

semiconduttori ma di tipo non volatile e di sola lettura.

Utilizzata ad esempio per memorizzare i microprogrammi

a livello firmware (BIOS).

• Memorie flash: memorie elettroniche riscrivibili non volatili.

Sono più lente delle memorie RAM (soprattutto in

scrittura) ma sono sempre più diffuse in dispositivi portatili

(macchine fotografiche digitali, telefoni cellulari, etc.) e per

trasportare dati (collegandosi al calcolatore tramite

interfaccia USB).

• Memorie di massa: di grande capacità e non volatili, sono

più lente rispetto alla RAM. Sono principalmente

realizzate tramite tecnologie magnetiche (Hard Disk) e

9

ottiche (CD, DVD). Il tempo di accesso non è costante.

Bus di sistema

• Il Bus di sistema è costituito da un insieme di connessioni

elementari, o linee, lungo le quali viene trasferita

informazione.

• Ciascuna linea sarà preposta al trasferimento del segnale

elettrico relativo ad un solo bit (tensione alta=1, tensione

bassa=0) quindi si parlerà ad esempio di Bus a 16, 32 o 64

bits. I bit vengono trasferiti in parallelo, ossia

contemporaneamente.

• Il Bus è in genere sotto il controllo della CPU, che

seleziona l’interconnessione da attivare e indica

l’operazione da compiere.

• Le altre unità collegate al Bus entrano in azione solo

quando sono selezionate dalla CPU.

10

Bus di sistema

• Le linee del Bus si suddividono in tre categorie:

– Bus dati: usato per trasferire dati fra CPU e memoria o

interfacce di I/O. La sua ampiezza dovrebbe essere

quella della parola di memoria.

– Bus indirizzi: usato per trasferire l’indirizzo della cella di

memoria in cui la CPU va a scrivere/leggere. La sua

ampiezza dipenderà dallo spazio di indirizzamento.

– Bus di controllo: dove passano i segnali di controllo che

indicano il tipo di operazione da effettuare. Esempio,

supponiamo vi siano due linee:

• R/W: indica (se alto) un’operazione di lettura (READ)

oppure (se basso) di scrittura (WRITE).

• M/IO: distingue tra operazione con la memoria (alto) o

11

con un’interfaccia di I/O (basso).

Schema di funzionamento di

una RAM

cella da 8 bit

parola

da 8 bit

0 1 0 0 1 1 0 0

16 celle di memoria

Decodificatore

Bus controllo

Bus dati

Bus indirizzi

linee di selezione parola

0110

R/W

0 1 0 0 1 1 0 0

dato

(letto o da scrivere)

12

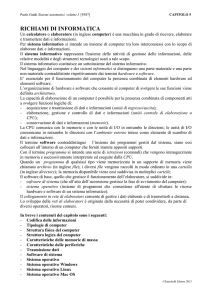

L’Unità di Elaborazione (CPU)

• La sua funzione è quella di eseguire i Programmi contenuti nella

memoria centrale.

• Si compone di tre componenti fondamentali:

– L’Unità di Controllo: è il dispositivo che coordina le

operazioni della CPU.

– L’Unità aritmetico-logica (ALU, Arithmetic and Logic

Unit): effettua le operazioni di tipo aritmetico e logico

richieste dalle istruzioni di un Programma.

– Registri: in pratica costituiscono la memoria interna alla

CPU, del tutto analoghi a celle di memoria, ma accessibili più

velocemente; contengono dati o istruzioni di uso frequente,

oppure risultati intermedi. Tra questi registri troviamo anche i

Registri Dati e i Registri Indirizzi.

13

L’Unità di Controllo

•

I suoi compiti principali sono:

1. Recuperare l’istruzione successiva da eseguire

2. Decodificarla

3. Organizzare la sua esecuzione

•

Contiene almeno tre registri fondamentali:

– Instruction register (IR): contiene l’istruzione

corrente.

– Program counter (PC): contiene l’indirizzo di

memoria della prossima istruzione da eseguire.

– Program status word (PSW): contiene dei bit speciali

che riflettono il risultato dell’ultima operazione (i

cosiddetti effetti collaterali).

14

Arithmetic-Logic Unit (ALU)

•

•

•

•

Esegue le operazioni logiche (AND, OR, NOT),

aritmetiche (somme, prodotti) e confronti.

In genere memorizza il risultato in un registro

predefinito.

Inoltre imposta i bit del Program Status Word in

accordo al risultato.

Operazioni su valori in virgola mobile e funzioni

trascendenti (trigonometriche, radici quadrate, etc.)

vengono in genere calcolate da un’unità apposita

della ALU detta Floating Point Unit (FPU).

15

Program Status Word (PSW)

•

Contiene una serie di bit (in questo caso denominati

flags) che se impostati ad 1 indicano il verificarsi di

alcune situazioni particolari:

– bit di carry: l’ultima addizione ha avuto un riporto.

– bit di zero: il risultato dell’ultima operazione è 0.

– bit di segno: segno del risultato dell’ultima

operazione.

– bit di overflow: ad esempio se il risultato

dell’ultima operazione è più grande del massimo

intero rappresentabile.

– etc..

16

Struttura della CPU e

collegamenti con la memoria

CPU

ALU

PSW

Address Bus

R01

R00

Data Registers

Data Bus

Control

Unit

Control Bus

op

R02

IR

R03

PC

Memory

17

Ciclo di esecuzione della CPU

•

Nell’esecuzione di un Programma, la CPU opera in

modo ciclico, ripetendo fino alla terminazione del

Programma almeno queste tre fasi (azioni atomiche):

1.

2.

3.

Lettura (fetch): acquisizione dalla memoria della

prossima istruzione da eseguire;

Decodifica (decode): riconoscimento dell’istruzione e

identificazione delle operazioni da svolgere per

completarne l’esecuzione;

Esecuzione (execute): effettuazione delle operazioni

corrispondenti all’istruzione.

18

Ciclo di esecuzione della CPU

•

Tutte le azioni eseguite all’interno della CPU (ma

anche di altri dispositivi) vengono sincronizzate da un

oscillatore a cristalli di quarzo (clock), che segna la

scansione temporale degli eventi:

ciclo di clock

•

•

In un ciclo di clock viene eseguita una singola azione

atomica. La frequenza di clock si misura in Hertz (cicli

o oscillazioni al secondo).

Le frequenze delle CPU dei moderni Calcolatori è

19

dell’ordine dei GHz (1 GHz = 1000000000 Hz).

CPU: Linguaggio Macchina

• Il linguaggio in cui sono scritti i Programmi che la

CPU è in grado di eseguire si chiama linguaggio

macchina.

• Ogni istruzione (es. lettura, somma, etc.) è definita da

un codice binario speciale detto codice operativo.

• Ogni CPU è caratterizzata da un suo insieme di

istruzioni elementari (instruction set) che ne

costituisce il linguaggio macchina.

• CPU diverse “parlano linguaggi” diversi (anche se

oggi, ad esempio, AMD e Intel “parlano” quasi lo

stesso linguaggio, molto diverso invece, ad esempio,

20

da quello delle CPU IBM)!

CPU: Linguaggio Macchina

• Un’istruzione è costituita da una stringa di bit

contenente:

– Il codice operativo dell’istruzione

– Gli operandi dell’istruzione

• Esempio di istruzione che effettua la somma di due

operandi src1 e src2 contenuti nei registri R02 e

R03 e salva il risultato nel registro R01 (dst):

codice operativo

000000 00000 100000

dst(R01) src1(R02) src2(R03)

00001

00010

00011

21

Linguaggio Assembler

• La scrittura di un Programma in Linguaggio Macchina è

un’operazione estremamente complicata, per via del fatto di dover

indicare istruzioni e operandi in codice binario.

• Il Linguaggio Assembler (o Assemblativo) è un linguaggio

simbolico, nel senso che vengono adoperati dei simboli per la

rappresentazione del codice operativo (tipo add per la somma) e

degli operandi di un’istruzione (direttamente il nome di un

Registro, es. R01, o un numero in esadecimale per indicare un

indirizzo di memoria).

• In pratica sussiste una corrispondenza biunivoca tra l’insieme

delle istruzioni in Linguaggio Macchina e quello delle istruzioni in

Linguaggio Assembler per una stessa CPU.

• Un Programma scritto in Assembler deve essere tradotto in

Linguaggio Macchina per essere eseguito dalla CPU, la

traduzione è effettuata da un Programma apposito, chiamato 22

Assemblatore.

Tipi di Istruzione

• Istruzioni aritmetico-logiche: manipolano dati in ingresso e

restituiscono il risultato in uscita, specificando dove depositare il

risultato (Registro).

• Istruzioni di salto: permettono di alterare l’esecuzione

sequenziale di un programma. Si dividono in istruzioni di:

– salto incondizionato: specificano l’indirizzo di memoria in cui si

trova la prossima istruzione da eseguire.

– salto condizionato: specificano inoltre una condizione che

deve essere verificata affinché il salto abbia luogo, altrimenti

l’elaborazione prosegue in sequenza.

• Istruzioni di ingresso/uscita: servono a trasferire dati da e

verso la CPU, specificando l’unità periferica da usare (es.

memoria di massa) e la posizione del dato sia nella periferica che

nel Calcolatore (es: Registro o cella di Memoria).

23

Esempi di Istruzioni in

Assembler

Istruzione

add R01,R02,R03

addi R01,R02,421

lw R01,R02,421

sw R01,R02,421

j 8B2F0

beq R01,R02,-421

Significato

R01 ← R02 + R03

R01 ← R02 + 421

R01 ← M[R02 + 421]

M[R02 + 421] ← R01

vai a 8B2F0

se (R01=R02) vai a PC-421

Tipo

aritmetico-logica

aritmetico-logica

ingresso/uscita (I)

ingresso/uscita (O)

salto (incondizionato)

salto (condizionato)

24

Esecuzione di un Programma

nella Macchina di Von Neumann

•

Come abbiamo visto, ciascuna istruzione di un Programma viene eseguita

in tre fasi: l’acquisizione dalla Memoria, l’interpretazione e l’esecuzione.

•

L’acquisizione (fetch) si svolge a sua volta in quattro passi:

•

Il contenuto del PC viene trasferito attraverso il Bus Indirizzi al Registro

Indirizzi della Memoria Centrale. Attraverso il Bus di Controllo viene

specificata un’operazione di Lettura.

•

Avviene l’operazione di Lettura dalla Memoria Centrale: il contenuto

della Cella specificato dal Registro Indirizzi viene copiato nel Registro

Dati della Memoria.

•

Attraverso il Bus Dati viene trasferita la nuova istruzione nell’IR della

CPU.

•

Viene incrementato di 1 il valore del PC (ma in caso di “salto” il PC sarà

25

aggiornato con un altro valore)

Esecuzione di un Programma

nella Macchina di Von Neumann

•

La fase di interpretazione (decode) consiste nell’analisi

dell’IR per identificare l’operazione da eseguire. In questa

fase viene analizzato solo il Codice operativo dell’istruzione

corrente.

•

La fase di esecuzione (execute) dipende dal tipo di

operazione (aritmetico-logica, salto o trasferimento dati). Se

l’operazione è di tipo aritmetico-logica sarà eseguita con

l’ausilio dell’ALU.

26

Dispositivi Periferici

• Le Periferiche comunicano con la CPU tramite delle

interfacce di I/O.

• Un’interfaccia contiene Registri per inviare comandi

alla Periferica, scambiare dati e controllarne il

funzionamento.

• Le interfacce sono molto diverse tra loro a seconda

del tipo di Periferica considerata:

– Tastiera

– Stampante

– Dispositivi di Memoria di massa

– Scheda Video

– Strumenti di misurazione

– Sensori e attuatori di robot

– etc.

27

Dispositivi Periferici

• Le Periferiche possono essere più o meno

“intelligenti”, ovvero possono essere dotate di proprie

unità di controllo, capaci di convertire ed elaborare

dati.

• In questo caso le Periferiche saranno in grado di

cooperare con la CPU, occupandosi di eseguire

operazioni più o meno complesse (si pensi, ad

esempio, alla Scheda Video).

28

Memorie di massa: dischi

magnetici

• Il dispositivo di Memoria di massa (o Memoria

secondaria) che riveste un’importanza maggiore in

un Calcolatore è sicuramente il Disco fisso (o Hard

Disk)

• Un Disco fisso è composto da uno o più supporti

circolari di pari diametro ricoperti su entrambe le

facce da un sottile strato di materiale magnetico, le

cui condizioni di magnetizzazione consentono di

memorizzare i dati.

• Ogni unità atomica di memorizzazione si può trovare

in due sole condizioni di magnetizzazione,

corrispondenti ai valori 0 e 1.

29

Memorie di massa: dischi

magnetici

• I Dischi magnetici sono supporti di memorizzazione

non volatile, però presentano un tempo di accesso

ai dati molto maggiore rispetto a quello richiesto

dalla Memoria centrale.

• D’altra parte, la loro capacità può superare

notevolmente quella della Memoria centrale, e ciò

rende questi dispositivi particolarmente adatti alla

funzione di storage di Dati e Programmi.

30

Organizzazione di un disco

magnetico

• Le operazioni di lettura/scrittura sono eseguite da

una testina che viene posizionata in prossimità della

zona magnetizzata coinvolta nell’operazione.

• Le informazioni sono memorizzate in cerchi

concentrici detti tracce la cui larghezza è pari alla

dimensione della testina, e che contengono tutti la

stessa quantità di dati (la densità di memorizzazione

cresce dalla periferia al centro del disco).

• Le tracce sono suddivise in settori ed ogni settore

ospita dei blocchi di dati (records), in genere l’unità

minima di trasferimento tra disco e memoria

centrale.

31

Organizzazione di un disco

magnetico

tracce

e

settor

spazi tra

tracce

spazi tra

record

32

Funzionamento di un disco

magnetico

•

•

•

Per poter essere utilizzato un disco deve essere

formattato: in pratica si organizza la sua superficie in

tracce e settori.

Durante il funzionamento, il disco ruota a velocità

costante.

Per accedere ad un determinato record del disco si deve:

1. Posizionare la testina nella traccia contenente il record

(seek time o tempo di posizionamento).

2. Attendere che la rotazione posizioni il settore cercato

sotto la testina (latency time o tempo di latenza,

dipende dalla velocità di rotazione del disco).

3. Attivare la lettura/scrittura (trasferimento) dei dati.

33

Estensioni della Macchina di

Von Neumann

•

Se ci limitiamo a considerare il modello classico di Von Neumann, i

fattori che influiscono sulla velocità di elaborazione e potenzialità del

Calcolatore sono:

–

Dimensione dei Registri: determina la quantità di informazione su

cui la CPU può lavorare in un certo istante. I moderni Calcolatori

hanno Registri a 32, 64 e talvolta 128 bit.

–

Dimensione della RAM: più grande è la disponibilità di Memoria

centrale, meno accessi al Disco fisso sarò costretto a fare per

caricare in Memoria Dati e Istruzioni dei Programmi.

–

La frequenza di clock della CPU: infatti, la CPU usa le oscillazioni

delle molecole di un cristallo di quarzo (come l’orologio) per

scandire il tempo delle sue operazioni. I primi PC avevano una

frequenza pari a 4.77 MHz.

–

Ampiezza del Bus Dati: determina quanti bit alla volta vengono

trasmessi fra CPU e gli altri dispositivi.

–

Ampiezza del Bus Indirizzi: determina il numero di byte di

Memoria che la CPU è in grado di indirizzare.

34

Estensioni della Macchina di

Von Neumann

•

Il modello classico di Von Neumann presenta però tre

limiti fondamentali che ne limitano le prestazioni:

1. L’esecuzione dei Programmi avviene in maniera

sequenziale, un’istruzione dopo l’altra.

2. Impiego eccessivo del Bus di sistema per

l’interscambio delle informazioni con la Memoria

centrale e gli altri dispositivi.

3. I tempi di accesso alla Memoria centrale sono alti

rispetto alla velocità di funzionamento della CPU.

35

Estensioni della Macchina di

Von Neumann

•

Al fine di incrementare al massimo le prestazioni, nel corso dei

decenni sono state studiate e realizzate alcune modifiche

apportate al modello classico di Von Neumann:

–

–

–

Esecuzione separata ed in parallelo da parte di dispositivi appositi

delle varie fasi di un’istruzione (fetch, decode e execute):

architetture di tipo Pipeline.

Utilizzo di memorie Cache, ossia memorie estremamente veloci ma

anche più costose e ridotte da inserire tra CPU e Memoria centrale,

dove conservare Dati e Istruzioni di uso più frequente.

Architetture che utilizzano più processori:

• Processori dedicati: affiancano la CPU eseguendo dei compiti

specifici, quali il calcolo numerico (coprocessori matematici), la

gestione della grafica (GPU), la gestione dei canali di I/O (DMA,

Direct Memory Access).

• Sistemi multiprocessore: architetture dotate di molteplici CPU

indipendenti.

36

Architetture Pipeline

•

•

•

•

Nelle CPU dotate di Pipeline, l’esecuzione delle istruzioni di un

Programma vengono eseguite mediante un meccanismo simile

a quello di una catena di montaggio.

In pratica, mentre la CPU sta eseguendo una determinata

istruzione, è in corso l’acquisizione e decodifica dell’istruzione

successiva.

Questa tecnica prende anche il nome di Parallelismo Virtuale,

perché il flusso delle istruzioni procede dando l’impressione, in

termini di prestazioni, di disporre di più processori.

Per ottenere il massimo delle prestazioni è necessario però che

non ci siano istruzioni consecutive dipendenti tra di loro, ad

esempio:

– y ← x + 1; z ← y + 1

37

Memoria Cache

•

•

•

•

•

Ogni volta che la CPU deve accedere a Istruzioni e Dati, questi

devono essere caricati dalla RAM, il cui tempo di accesso è

molto più lento rispetto alla velocità della CPU.

La Memoria Cache è un’area di memoria particolare ad alta

velocità di accesso e di dimensioni piuttosto piccole rispetto alla

RAM.

Contiene Dati e Istruzioni utilizzati con maggior frequenza dalla

CPU, e questo determina l’incremento delle prestazioni.

In fase di Lettura, se alla CPU serve un Dato o un’Istruzione, la

ricerca viene fatta prima nella Cache, e se l’informazione non è

presente viene prelevata dalla RAM e copiata nella Cache.

In fase di Scrittura, l’informazione viene scritta sia in RAM che

nella Cache.

38

Memoria Cache

•

•

L’esistenza della Cache è del tutto trasparente dal punto di

vista del Linguaggio Macchina, in quanto la CPU è

“convinta” di lavorare solo con la RAM.

La Memoria Centrale non può essere sostituita con una

memoria realizzata come la Cache, per due motivi

principali:

– La Cache è molto più costosa di una memoria di tipo

tradizionale.

– Per garantire un tempo di accesso estremamente

basso, la Cache deve fisicamente risiedere vicino alla

CPU, possibilmente integrata sullo stesso chip, così da

non richiedere l’utilizzo del Bus di sistema per l’accesso.

Quindi è fisicamente impossibile, per ragioni puramente

di spazio, realizzare Cache veloci e allo stesso tempo

39

molto capienti.

Architetture a più processori

•

•

•

•

Un’architettura a più processori (o parallela) è un sistema

di calcolo costituito da un insieme di processori in grado di

comunicare e cooperare tra loro.

Se si considerano i sistemi multiprocessore (quelli dove

sono presenti N CPU), teoricamente sarebbe lecito

aspettarsi un aumento delle prestazioni direttamente

proporzionale al numero di CPU (N processori, allora

sistema N volte più veloce).

In realtà l’incremento di prestazioni è inferiore, e il motivo

principale risiede nel fatto che è complicato scrivere

programmi che siano in grado di sfruttare appieno tale

architettura.

Infatti, il problema delle istruzioni dipendenti (vedi Pipeline)

riguarda anche questo tipo di architettura.

40

Architetture a più processori

•

•

L’impiego di architetture a più processori comporta

l’importante scelta di come gestire e sincronizzare gli

accessi alla Memoria centrale.

In genere si distinguono due approcci:

–

–

Architetture a Memoria Distribuita: ciascuna CPU è dotata

di una memoria privata. Ad esempio i processori dedicati

GPU (Graphics Processing Unit) delle schede grafiche più

sofisticate, dispongono anche di una memoria propria.

Architetture a Memoria Condivisa: tutte le CPU

condividono l’accesso ad una memoria comune, utilizzando

anche uno stesso BUS di sistema. La necessità di dover

utilizzare un BUS comune riduce le prestazioni del sistema

introducendo un “collo di bottiglia” nell’accesso alla memoria.

Il problema può essere affrontato adottando memorie Cache

locali per ciascuna CPU. I moderni sistemi “dual core” (due

CPU nello stesso chip) rientrano in questa categoria. 41

Architetture CISC e RISC

•

E’ possibile classificare i Calcolatori anche rispetto al numero e alla

complessità dell’insieme di istruzioni componenti il Linguaggio

Macchina della CPU.

–

Architetture CISC (Complex Instruction Set Computers): su

questo tipo di architettura è stata basata a lungo la maggior parte

dei Calcolatori sul mercato, si caratterizza per:

• Il Linguaggio Macchina è costituito da un numero grande di

istruzioni.

• L’elaborazione di ogni singola istruzione è piuttosto complessa.

• Comporta una struttura hardware della CPU complessa.

–

Architetture RISC (Reduced Instruction Set Computers): queste

architetture sono caratterizzate da un ridotto insieme di istruzioni,

inoltre le istruzioni sono progettate in maniera tale da rendere

l’hardware della CPU il più semplice possibile, con notevoli

vantaggi in termini di prestazione.

42

Architetture CISC e RISC

Processori Intel CISC (“famiglia x86”)

Modello

8086

80286

80386

80486

Anno

Bus Dati

produzione

(bit)

1978

1982

1985

1989

16

16

32

32

Registri

Memoria

(bit)

Indirizzabile

16

16

32

32

1 Mb

16 Mb

4 Gb

4 Gb

Frequenza massima

CPU (MHz)

8

20

33

100

43

Architetture CISC e RISC

Processori Motorola CISC (“famiglia 680x”)

Modello

68000

68020

68030

68040

68060

Anno

Bus Dati

produzione

(bit)

1979

1984

1987

1989

1993

16

32

32

32

32

Registri

Memoria

(bit)

Indirizzabile

32

32

32

32

32

16 Mb

4 Gb

4 Gb

4 Gb

4 Gb

Frequenza massima

CPU (MHz)

8

16

32

40

66

44

Architetture CISC e RISC

Processori Intel “ibridi” (CRISC)

Modello

Anno

Bus Dati

produzione

(bit)

Pentium

P MMX

Pentium II

Pentium III

Pentium 4

Itanium-2

1993

1997

1997

2000

2002

2003

64

64

64

64

64

128

Registri

Memoria

(bit)

Indirizzabile

32

32

32

32

32

64

4 Gb

4 Gb

4 Gb

4 Gb

4 Gb

128 Gb

Frequenza massima

CPU (MHz)

150

266

450

1000

3200

1500

45

Architetture CISC e RISC

Processori IBM-Motorola RISC

Modello

Anno

Bus Dati

produzione

(bit)

MPC 601

PowPC 750

MPC 7400

MPC 7455

PowPC 970

1994

1997

1999

2002

2004

64

64

64

64

2 da 32

Registri

Memoria

(bit)

Indirizzabile

32

32

32

32

64

4 Gb

4 Gb

4 Gb

4 Gb

4 Tb (42 bit)

Frequenza massima

CPU (MHz)

120

466

500

1250

2500

46