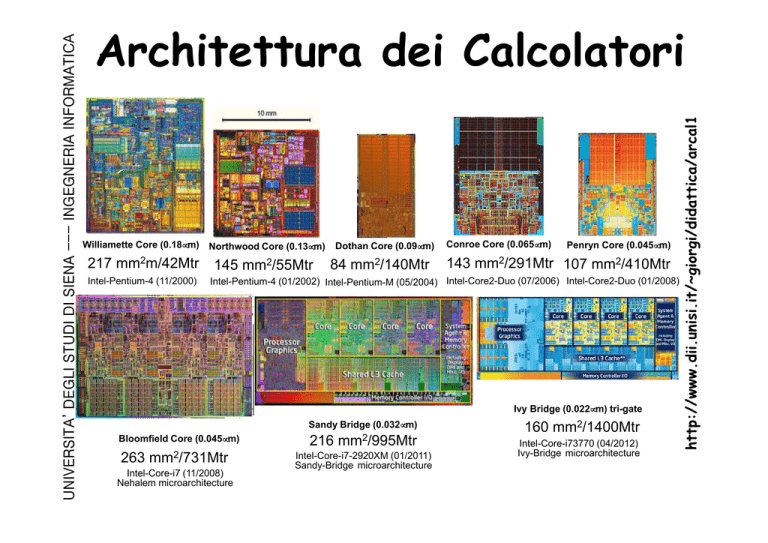

Architettura dei Calcolatori

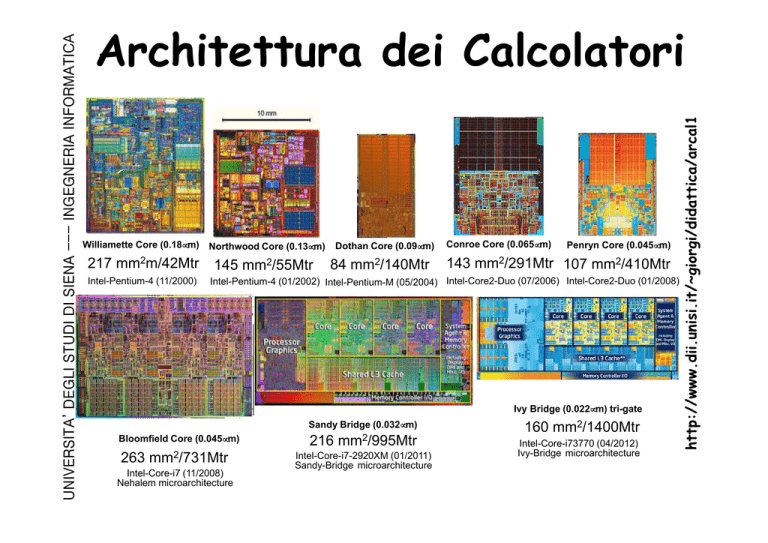

Williamette Core (0.18µm) Northwood Core (0.13µm)

2

217 mm2m/42Mtr

145 mm /55Mtr

Intel-Pentium-4 (11/2000)

Dothan Core (0.09µm)

84 mm2/140Mtr

Conroe Core (0.065µm)

Penryn Core (0.045µm)

143 mm2/291Mtr 107 mm2/410Mtr

Intel-Pentium-4 (01/2002) Intel-Pentium-M (05/2004) Intel-Core2-Duo (07/2006) Intel-Core2-Duo (01/2008)

Ivy Bridge (0.022µm) tri-gate

Bloomfield Core (0.045µm)

263

mm2/731Mtr

Intel-Core-i7 (11/2008)

Nehalem microarchitecture

Sandy Bridge (0.032µm)

216 mm2/995Mtr

Intel-Core-i7-2920XM (01/2011)

Sandy-Bridge microarchitecture

160 mm2/1400Mtr

Intel-Core-i73770 (04/2012)

Ivy-Bridge microarchitecture

Legge di Moore

• Il numero di transistor RADDOPPIA ogni 18 mesi

(successivamente modificato in “24 mesi”)

• Consentito sia da una maggiore densita’ che da chip di

maggiori dimensioni

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 2

Obiettivi del Corso

e Come Raggiungerli

1) Saper scegliere un calcolatore

esaminando i parametri che ne influenzano le prestazioni

Analisi quantitativa dei fattori che influenzano le prestazioni

e discussione su come le architetture incidono su tali fattori

2) Capire l’architettura dei moderni calcolatori

Analisi dell’organizzazione interna dei principali elementi:

processore, memoria, I/O, elementi di progettazione logica

3) Essere in grado di valutare l’efficacia dei meccanismi

architetturali atti a migliorare le potenzialita’ dei

calcolatori

Analisi di soluzioni architetturali non necessarie ma ormai

universalmente presenti quali cache, memoria virtuale, pipeline

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 3

1) Imparare a misurare e analizzare le prestazioni

• Definizione “software” della macchina

• Metriche e Benchmarks

• Influenza dei criteri prestazionali sulla definizione

“software” della macchina

IPC

OOO

SPEC2000

multithreading

Tempo di esecuzione

ILP

multiprocessore

TPC

CMP

multicore

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 4

2) Analisi dell’architettura di un calcolatore

• Il processore: parte di controllo e parte datapath

• Le reti di interconnessione e interfacciamento

• Il sistema di Input/Output

• La Memoria

Processor

Input

Dal 1946 tutti i computer

hanno questi 5 componenti!

Control

Memory

Datapath

Output

L’interno di ciascuno di questi

componenti e’ pero’ cambiato

in maniera impressionante!

• Progettazione Logica: come si passa dal dispositivo fisico,

agli elementi logici ed architetturali

• equazioni booleane, macchine a stati finiti, componenti logici

Understanding the TECHNOLOGY!!!

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 5

3) Architetture per Migliorare le Potenzialita’

• Memoria Cache

Spatial locality

• Memoria Virtuale

Striding

Loops

Locality Surface

25

30

• Pipeline

Temporal Locality(stride=0)

30

20

15

10

25

5

12

page offest

4096

1024

128

8

stride

32

2

0

-2

-8

-128

256

16

1,70E+07

64

1

stride

4

-4

1048576 distance

-1

-64

-16

-256

0

Temporal locality

10

P2 index

90

80

70

60

50

40

30

20

10

0

1

16

256

4096

65536

5

Spatial Locality(distance=1)

-32

10

10

P1 index

64

distance

15

Sequentiality

256

4

1

16

0

20

1K

foglie

1 radice

4KB

Tempo

F

4 bytes

D

X

M

F

D

X

M

F

D

X

M

F

D

X

M

F

D

X

M

F

D

X

Flusso di programma

4 bytes

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 6

W

W

W

W

W

M

W

Conoscenze di base dai corsi precedenti

• Saper formalizzare un problema descritto in linguaggio

naturale in modo che possa essere seguito dal calcolatore

• Saper leggere e saper scrivere semplici programmi C

• Struttura base della macchina

• Modello di Esecuzione

ovvero principi di una macchina astratta in grado di eseguire

programmi (ciclo fetch-execute, struttura di Von Neumann)

• Capire i passi che vengono compiuti

per generare un programma:

• compilazione, link, caricamento e esecuzione

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 7

Informazioni

Logistiche

Amministrazione del Corso

• Docente:

Roberto Giorgi ([email protected])

• Telefono:

0577-191-5182

• Ricevimento:

Lunedi 16:30/19:00

• Dispense:

http://www.dii.unisi.it/~giorgi/didattica/arcal1

• Testi di Riferimento:

• Patterson and Hennessy, Computer Organization and Design: The

Hardware/Software Interface, Fifth Edition, Morgan Kauffman, 2014

• Quarta edizione in Italiano (basata sulla precedente ed. In inglese):

D. A. Patterson, J. L. Hennessy, Struttura e Progetto dei Calcolatori,

Zanichelli, 2015

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 9

Formato dell’insegnamento

• STUDIO

• LEZIONI+ ESERCITAZIONI (totale 60 ore)

• Circa 40 ore di teoria, 20 ore di esercitazioni

• VALUTAZIONE

• 1 COMPITINO FINALE (65% valutazione) – 3 domande

-

MODALITA’ RECUPERO COMPITINO:

-

Scritto ad un appello ordinario – 5 domande

• 1 PROGETTO (35% valutazione) – dettagli nei prossimi giorni

-------------------------------------------ALTRI INSEGNAMENTI CORRELATI

• High Performance Computer Architecture (Master Degree)

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 10

Compitino

• La data del compitino e’ tentativamente il

• Giovedi

18-12-2015 ore 14/16

QUESTE INFORMAZIONI SONO TUTTE

RIPORTATE ANCHE SUL SITO DEL CORSO

http://www.ing.unisi.it/~giorgi/didattica/arcal1

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 11

Organizzazione della lezione di oggi

• Tipologie di calcolatori

• Definizione di Architettura di un Calcolatore

• Introduzione al processore MIPS

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 12

Tipologie

di Calcolatori

I 3 tipi principali di calcolatori oggi

Embedded

Desktop

Server

• Calcolatori ‘Desktop’/’Embedded’

Architettura dei Calcolatori

• Calcolatori ‘Server’/’Desktop’

High Performance

Computer Architecture

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 14

Parti principali di un calcolatore ‘desktop’

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 15

Contesto di lavoro di un Calcolatore

Web Server

Applicazioni

Kernels

SPEC

Benchmarks

Database

Operating System

MMU

Status

Registers

Real Time

Clock

Terminal

I/O MMU

Controller

DMA

Controller

IRQ

Controller

Serial Port

Processore

RAM

Calcolatore

Adattatore (Bridge)

PCIe Bus

INTERNET

Ethernet

Controller

SD-card

Audio

Card

Storage

Storage

Controller

…

Graphics

Card

Storage

I/O

• Tutti questi componenti hanno

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 16

• una propria interfaccia e

• una propria organizzazione interna

Livelli di Astrazione di un Calcolatore

Applicazione

Operating

System

SW

Compiler

Firmware

Instruction Set

Architecture

Instr. Set Processor

HW

I/O Subystem

Datapath & Control

Progetto Digitale

Progetto Circuitale

Layout

• Coordinamento fra molti livelli di astrazione

• Cambiamenti tecnologici che avvengono ogni giorno

• Ciclo virtuoso: progettazione simulazione valutazione

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 17

Il Set di Istruzioni: un’interfaccia critica

SW

instruction set

HW

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 18

Livelli di rappresentazione

temp = v[k];

Programma in

Linguaggio di Alto Livello

v[k] = v[k+1];

v[k+1] = temp;

Compilatore

Programma in

Linguaggio Assembly

Assemblatore

Programma

in Linguaggio Macchina

lw $15,

lw $16,

sw $16,

sw $15,

0($2)

4($2)

0($2)

4($2)

0000

1010

1100

0101

1100

0101

1010

0000

1001

1111

0110

1000

0110

1000

1111

1001

1010

0000

0101

1100

1111

1001

1000

0110

0101

1100

0000

1010

Esecuzione

Specifica dei Segnali di Controllo

°

°

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 19

ALUOP[0:3] <= InstReg[9:11] & MASK

1000

0110

1001

1111

Architettura

dei Calcolatori

Architettura dei Calcolatori

• “Il termine ARCHITETTURA e’ usato qui per

descrivere l’insieme degli attributi di un sistema, cosi’

come questo appare al programmatore*, ovvero la sua

struttura concettuale e il suo funzionamento, con una

distinzione dell’organizzazione delle reti che gestiscono

il flusso dei dati e delle reti di controllo, rispetto alla

progettazione logica e rispetto all’implementazione

fisica”

-- Gene Amdahl, IBM Journal of R&D, Apr. 1964

Una definizione piu’ “moderna” (da http://www.cs.wisc.edu/~arch/www/ )

“Con Architettura dei Calcolatori si intende la scienza e l’arte di

selezionare e collegare componenti hardware per creare calcolatori che

soddisfano determinati requisiti funzionali, di prestazioni e di costo.

L’architettura dei calcolatori non ha niente a che vedere con l’uso dei

calcolatori per progettare edifici.”

*programmatore ==

programmatore di sistema (operativo)

o ingegnere del compilatore

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 21

Cosa e’ la “Architettura di un Calcolatore”

Computer Architecture

=

Instruction Set Architecture +

Machine Organization

• Instruction Set Architecture:

• Come l’Hardware viene visto dal Software

• Machine Organization:

• Implementazione fisica

(in termini di blocchi funzionali e logici)

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 22

Instruction Set Architecture (es. MIPS 3000)

Registri FP

Registri INT

$0

$1

$f0

$f1

•

•

•

0

1

32

CAUSE

STATUS

232-1

BADVADDR

32 bit

32 bit

• Categorie di Istruzioni

•

•

•

•

•

•

•

EPC

$f31

32 bit

Memoria e I/O

PC

HI

LO

•

•

•

$31

Registri Speciali

Load/Store

Calcolo (per Interi e per Frazionari)

Jump/Branch

Istruzioni speciali

• Formato delle Istruzioni:

• lunghezza FISSA a 32 bit

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 23

CPU a 32 bit

8 bit

Organizzazione fisica del Calcolatore

• Caratteristiche e Prestazioni

delle principali Unita’ Funzionali

• (e.g., Registers, ALU, Shifters, Logic Units, ...)

• Metodi con cui tali componenti sono interconnessi

• Tipo di informazione che viene scambiata fra i

componenti

• Logica e Metodi per controllare tale scambio di

informazioni

• Insieme delle Unita’ Funzionali e loro interfacciamento

• Descrizione in termini di linguaggio

Register Transfer Level (RTL), ove necessario

Roberto Giorgi, Universita’ di Siena, C116L01, Slide 24