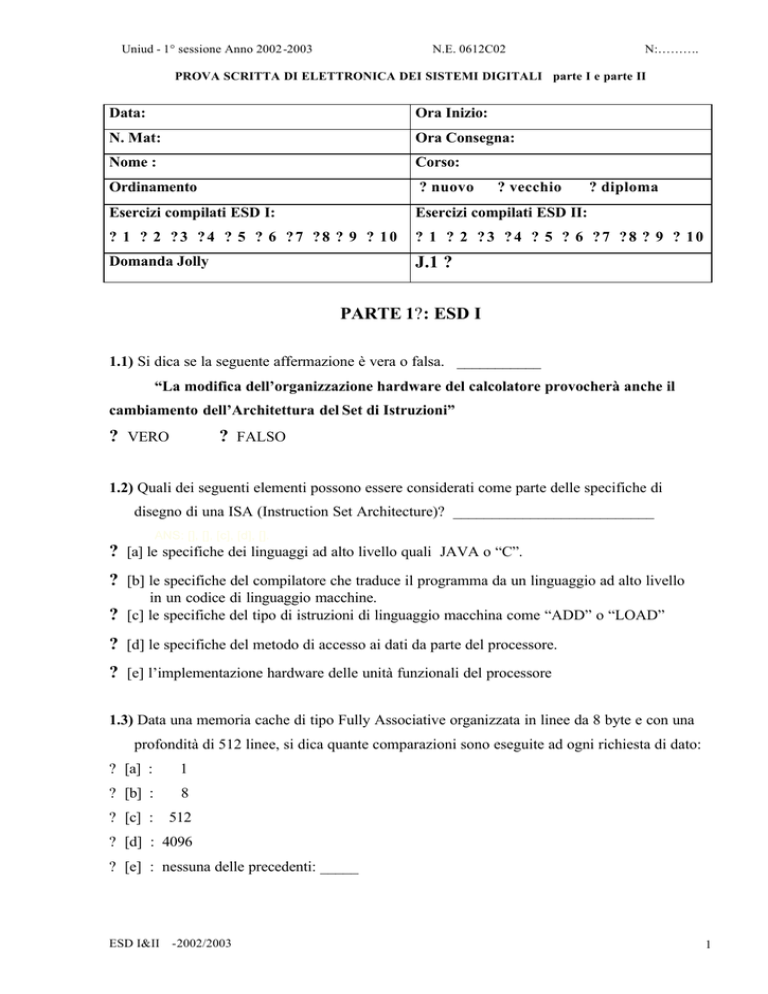

Uniud - 1° sessione Anno 2002-2003

N.E. 0612C02

N:……….

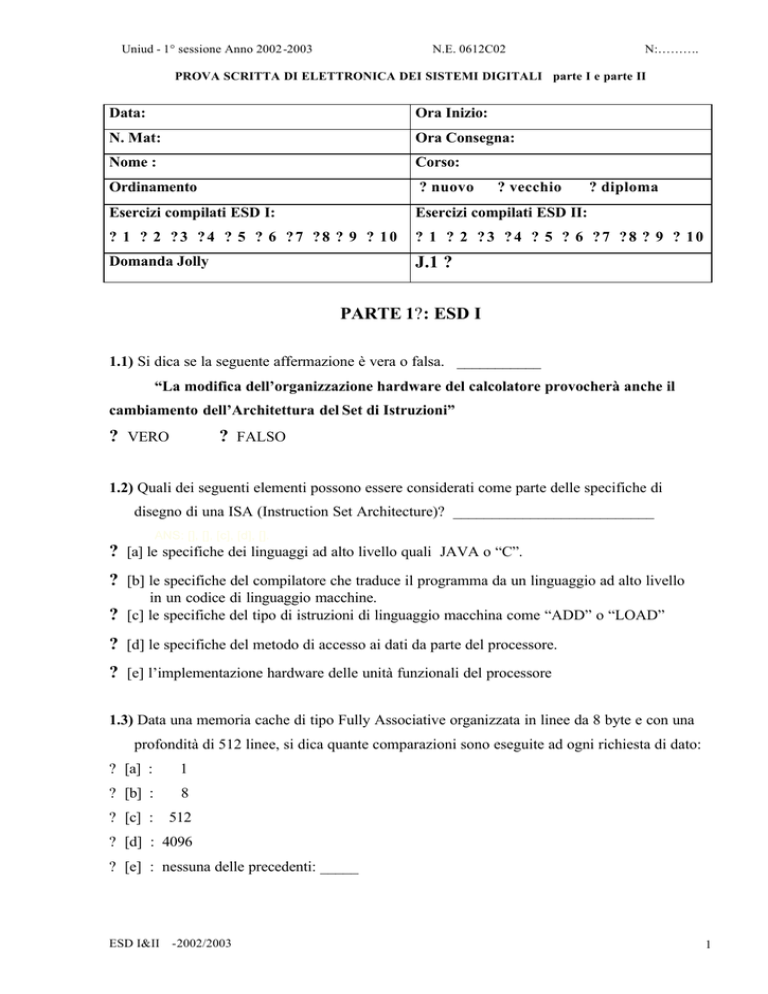

PROVA SCRITTA DI ELETTRONICA DEI SISTEMI DIGITALI parte I e parte II

Data:

Ora Inizio:

N. Mat:

Ora Consegna:

Nome :

Corso:

Ordinamento

? nuovo

Esercizi compilati ESD I:

Esercizi compilati ESD II:

? 1 ? 2 ?3 ?4 ? 5 ? 6 ?7 ?8 ? 9 ? 10

? 1 ? 2 ?3 ?4 ? 5 ? 6 ?7 ?8 ? 9 ? 10

Domanda Jolly

J.1 ?

? vecchio

? diploma

PARTE 1?: ESD I

1.1) Si dica se la seguente affermazione è vera o falsa. ___________

“La modifica dell’organizzazione hardware del calcolatore provocherà anche il

cambiamento dell’Architettura del Set di Istruzioni”

? VERO

? FALSO

1.2) Quali dei seguenti elementi possono essere considerati come parte delle specifiche di

disegno di una ISA (Instruction Set Architecture)? __________________________

ANS: [], [], [c], [d], [].

? [a] le specifiche dei linguaggi ad alto livello quali JAVA o “C”.

? [b] le specifiche del compilatore che traduce il programma da un linguaggio ad alto livello

in un codice di linguaggio macchine.

? [c] le specifiche del tipo di istruzioni di linguaggio macchina come “ADD” o “LOAD”

? [d] le specifiche del metodo di accesso ai dati da parte del processore.

? [e] l’implementazione hardware delle unità funzionali del processore

1.3) Data una memoria cache di tipo Fully Associative organizzata in linee da 8 byte e con una

profondità di 512 linee, si dica quante comparazioni sono eseguite ad ogni richiesta di dato:

? [a] :

1

? [b] :

8

? [c] :

512

? [d] : 4096

? [e] : nessuna delle precedenti: _____

ESD I&II -2002/2003

1

Uniud - 1° sessione Anno 2002-2003

N.E. 0612C02

N:……….

PROVA SCRITTA DI ELETTRONICA DEI SISTEMI DIGITALI parte I e parte II

1.4) Si realizzi la funzione XOR a due ingressi a partire dal minor numero possibile di porte

NAND a due ingressi.

1.5) Alcuni processori sono dotati internamente di TLB . Si completino le affermazioni seguenti

relativamente alla tabella TLB:

a) Serve per la gestione della :________________________________________________

b) Ha la funzione di : _______________________________________________________

_______________________________________________________________

c) Dovendo fare un paragone tra TLB e un livello della struttura gerarchica della memoria, a

quale lo si può rapportare? : _________________________________________________

1.6) Si calcoli la memoria massima indirizzabile per una delle seguenti CPU, dati la larghezza

del bus dati e del bus indirizzi.

a) 8 bit di bus dati e 16 bit di bus indirizzi (risultato in K byte):

_________________________________________________________________

_________________________________________________________________

b) 16 bit di bus dati e 24 bit di bus indirizzi (risultato in Mega byte):

_________________________________________________________________

_________________________________________________________________

ESD I&II -2002/2003

2

Uniud - 1° sessione Anno 2002-2003

N.E. 0612C02

N:……….

PROVA SCRITTA DI ELETTRONICA DEI SISTEMI DIGITALI parte I e parte II

c) 32 bit di bus dati e 48 bit di bus indirizzi (risultato in Mega byte, Giga byte, Tera byte):

_________________________________________________________________

_________________________________________________________________

1.7) Si consideri un computer dotato di processore con una ISA che dà la seguente distribuzione

sul programma di benchmark:

Istruz.

ALU r/r

Load

Store

Branch

Freq.

50%

20%

10%

20%

Cicli

1

2

2

2

L’ISA del processore del computer in esame è dotato di istruzioni ALU che lavorano solo tra

registri e non tra memoria e registri.

Si decide di modificare l’ISA del processore al fine di dotarlo di istruzioni ALU r/m da 2 cicli

di clock, che agiscano cioè tra Registri e Memoria, sapendo che la loro introduzione comporta un

allungamento delle istruzioni di Branch da 2 a 3 cicli. (Queste nuove ALU r/m sono equiva lenti

nell’ ISA originario alla sequenza di due istruzioni : Load e ALU r/r )

Si calcoli di quanto devono diminuire in percentuale le istruzioni di Load affinché si abbiano dei

vantaggi da questa modifica (ovvero quanto deve incidere nel mix di istruzio ni la percentuale

delle nuove operazioni di ALU r/m).

ISA 1

Istruz.

Freq.

Cicli

ISA 2

ALU r/r

Load

Store

Branch

50%

20%

10%

20%

1

2

2

2

Istruz.

ALU r/r

Load

Store

Branch

ALU r/m

Freq.

Cicli

_____

_____

_____

_____

_____

1

2

2

3

2

a) Calcolare il CPI dell’ ISA 1:

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

b) Calcolare la percentuale di Load nell’ ISA 2 tale da renderlo equivalente o più vantaggioso

rispetto all’ISA 1:

ESD I&II -2002/2003

3

Uniud - 1° sessione Anno 2002-2003

N.E. 0612C02

N:……….

PROVA SCRITTA DI ELETTRONICA DEI SISTEMI DIGITALI parte I e parte II

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

1.8) Dato un calcolatore dotato di una struttura della memoria a tre livelli con le seguenti

caratteristiche:

Memoria Interna Cache

: Tempo di Accesso T1= 20 ns

Memoria Interna Principale : Tempo di Accesso T2= 60 ns

Memoria Esterna Disco

: Tempo di Accesso T3= 12 ms

Percentuale di Hit sul primo Livello : H1=0,9

Percentuale di Hit sul secondo Livello : H2=0,6

Si calcoli il Tempo Medio di Accesso alla Memoria vista come un tutt’uno.

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

1.9) Le leggi di scala si basano sulla stessa formula del tasso composto di interesse: F=P*(1+t)^n

(dove F è il valore futuro, P è il valore presente, t è il tasso di crescita e n è il numero di

periodi, es. numero di anni). Si diano le risposte ai seguenti questi:

ESD I&II -2002/2003

4

Uniud - 1° sessione Anno 2002-2003

N.E. 0612C02

N:……….

PROVA SCRITTA DI ELETTRONICA DEI SISTEMI DIGITALI parte I e parte II

a) Se su un periodo di 10 anni, dal 1989 al 1998, la banda di picco della memoria DRAM è

migliorata di 12 volte, quanto è stato il tasso di crescita?

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

b) Se nel decennio di cui al punto precedente la latenza è diminuita del 47% all’anno e nel 1989

la latenza della memoria DRAM era di 6us, che valore ha raggiunto nel 1998?

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

c) La legge di Moore prevede una raddoppio del numero di transistor ogni 18 mesi; di che tasso

di crescita stiamo parlando ?

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

1.10) Si considerino due computer A e B con lo stesso ISA. Il computer A è cinque volte più

veloce del computer B nella maggior parte dei casi. L’unica eccezione è rappresentata dalla

moltiplicazione, infatti il computer B dispone di un hardware dedicato per la

moltiplicazione tale per cui essa è 4 volte più veloce rispetto al computer A. Si assuma che

le performance relative dei due computer sia no 5 ad 1 se non si usano moltiplicazioni.

a) Si chiede di calcolare qual è la performance relativa tra i due computer nel caso si esegua un

programma che spenda il 5% del tempo in moltiplicazioni. Si faccia la stessa valutazione nel

caso in cui la percentuale sia del 20%.

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

ESD I&II -2002/2003

5

Uniud - 1° sessione Anno 2002-2003

N.E. 0612C02

N:……….

PROVA SCRITTA DI ELETTRONICA DEI SISTEMI DIGITALI parte I e parte II

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_______________________________________________________________

b) Disegnare il grafico che raffigura lo speed- up in funzione della percentuale di

moltiplicazioni:

Funzione:

Grafico

c) Quali considerazioni si possono trarre dalle risposte di cui al punto precedente?

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

d) Usando la classificazione dei computer paralleli indicare a quale classe appartiene un

calcolatore uniprocessore:

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

ESD I&II -2002/2003

6

Uniud - 1° sessione Anno 2002-2003

N.E. 0612C02

N:……….

PROVA SCRITTA DI ELETTRONICA DEI SISTEMI DIGITALI parte I e parte II

DOMANDA JOLLY

J.1) Dato un bus Asincrono, con un unico master (iniziatore del bus) e più slave (target), dotato

dei seguenti segnali :

D0:7

A0:15

R /W

M /IO

/TR

/MR

bus dati 8 bit

bus indirizzi 16 bit

segnale di controllo : indica lettura quando è alto e scrittura quando è basso

segnale di controllo : indica accesso in memoria quando è alto ed in I/O quando è basso

segnale di controllo : indica al master se il target è pronto a ricevere o trasmettere

segnale di controllo : indica al target se il master è pronto a ricevere o trasmettere

a) Si disegni un possibile ciclo di Write in Memoria seguito da un ciclo di Read in I/O:

A0:15

D0:7

R/W

M/IO

/TR

/MR

b) Con i segnali messi a disposizione è possibile per il Master allungare i cicli di lettura/scrittura

al fine di adattarsi a periferici lenti? Si giustifichi la risposta.

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

ESD I&II -2002/2003

7

Uniud - 1° sessione Anno 2002-2003

N.E. 0612C02

N:……….

PROVA SCRITTA DI ELETTRONICA DEI SISTEMI DIGITALI parte I e parte II

PARTE 2 ?: ESD II

2.1) Si dia la definizione dell’acronimo MTBF.

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

Si dica relativamente a quali argomenti si è incontrato il termine MTBF durante il corso:

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

2.2) Barrare le affermazioni che sono vere:

? a) Le famiglie logiche sono tanto migliori tanto più grande è il margine di rumore.

? b) In generale le logiche ad alta velocità consumano più potenza.

? c) La dissipazione cresce linearmente con la frequenza nelle logiche TTL.

2.3) Si supponga che una linea indirizzi di un microprocessore debba pilotare 5 carichi standard

TTL e ulteriori 10 carichi HCMOS, pin di ingresso dei chip di memoria DRAM.

a) Usando la tabella 1 calcolare la corrente minima necessaria a pilotare questi ingressi nel caso

del valore logico “0” e “1”.

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

ESD I&II -2002/2003

8

Uniud - 1° sessione Anno 2002-2003

N.E. 0612C02

N:……….

PROVA SCRITTA DI ELETTRONICA DEI SISTEMI DIGITALI parte I e parte II

TABELLA 1

Characteristics

Std TTL

LSTTL

ALSTTL

HCMOS

Vcc

5V

5V

5V

5V

Vih

2.0V

2.0V

2.0V

3.15V

Vil

0.8V

0.8V

0.8V

1.1V

Voh

2.4V

2.7V

2.7V

3.7V

Vol

0.4V

0.4V

0.4V

0.4V

Iil

-1.6mA

-0.36mA

-0.2mA

-1uA

Iih

40uA

20uA

20uA

1uA

Iol

16mA

8mA

4mA

4mA

Ioh

-400uA

-400uA

-400uA

-4mA

Propag. delay

10ns

9.5ns

4ns

9ns

Static Power (F=0)

10mW

2mW

1mW

0.0025nW

Dynamic Power

10mW

2mW

1mW

0.17mW

(F=100KHz)

b) Assumendo che il pin di indirizzo del microprocessore abbia come specifiche di pilotaggio

Ioh=400uA e Iol=2mA, dire se queste sono sufficienti per pilotare i carichi di cui al punto a).

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

2.4) Quale disturbo nei dispositivi digitali veloci è quantizzato dalla formula: V=L di/dt ?

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

ESD I&II -2002/2003

9

Uniud - 1° sessione Anno 2002-2003

N.E. 0612C02

N:……….

PROVA SCRITTA DI ELETTRONICA DEI SISTEMI DIGITALI parte I e parte II

2.5) Facendo uso di quale delle famiglie logiche di cui alla tabella 1 è più probabile che le piste

di un PCB si debbano trattare come linee di trasmissione? (barrare la casella relativa e

motivare la propria scelta).

Std TTL

LSTTL

ALSTTL

HCMOS

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

2.6) Si comple ti il diagramma del circuito logico di interfaccia tra la CPU e le memorie

utilizzando il minor numero di porte NOR. La mappa della memoria è la seguente:

0000h – 3FFFh SRAM

4000h – 7FFFh EPROM

8000h – BFFFh SRAM

C000h – FFFFh EPROM

CPU

D0..D7

A0..A15

D0..D7

SRAM

A0..A13

16KB

D0..D7

SRAM

A0..A13

16KB

/WE

/WE

/OE

/OE

/CE

/CE

D0..D7

EPROM

D0..D7

16KB

/MemR

EPROM

16KB

A0..A13

A0..A13

/OE

/OE

/MemW

/CE

ESD I&II -2002/2003

/CE

10

Uniud - 1° sessione Anno 2002-2003

N.E. 0612C02

N:……….

PROVA SCRITTA DI ELETTRONICA DEI SISTEMI DIGITALI parte I e parte II

2.7) Dire quali delle seguenti affermazioni è vera relativamente al segnale AEN presente nel bus

ISA:

?

?

?

?

?

a)

b)

c)

d)

e)

è un segnale di input

è un segnale di output

segnala la presenza di un ciclo di interrupt

segnala la presenza di un ciclo di DMA

segnala un ciclo di wait

2.8) Data una linea di trasmisione senza perdite (loss-free) con impedenza caratteristica

Z=60Ohm e capacità caratteristica C=0,4pF :

a) Si trovi il Tp (tempo di propagazione caratteristico) della linea:

_________________________________________________________________

_________________________________________________________________

b) Si stimi la lunghezza oltre la quale per un segnale con Tr (Time-rise) = 1,5ns la linea debba

essere trattata come linea di trasmissione.

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

2.9) Data una linea di trasmissione senza perdite collegata ad una sorgente e ad un ricevitore, si

determinino le relazioni tra Rs, Z e Rt con Z=50 Ohm, se al punto di inizio della linea

(Near-End) viene misurato un segnale con andamento come riportato in figura:

a) determinare le relazioni:

ESD I&II -2002/2003

11

Uniud - 1° sessione Anno 2002-2003

N.E. 0612C02

N:……….

PROVA SCRITTA DI ELETTRONICA DEI SISTEMI DIGITALI parte I e parte II

b) Si definiscano i segni dei coefficienti di riflessione al Near-End (inizio della linea) ed al FarEnd:

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

2.10) Si risponda alle seguenti domande, relative ad un sistema digitale:

a) Perché l’impedenza di una linea di interconnessione di un bus è minore dell’impedenza di

una linea di interconnessione punto a punto?

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

b) Quando e perché è buona norma terminare le linee di interconnessione di un bus?

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

c) Cosa si intende per commutazione su onda riflessa ? Si faccia un esempio.

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

_________________________________________________________________

ESD I&II -2002/2003

12