LOGICA BOOLEANA

l'OR logico ⇒ unione tra due insiemi A e B

componente elettronico::::: famiglia delle porte logiche

più generale: una porta logica OR formata da un numero arbitrario n di ingressi e da una sola uscita

l'AND ⇒ intersezione tra due insiemi A e B

più generale: una porta logica AND formata da un numero arbitrario n di ingressi e da una sola uscita.

NOT logico ⇒

complemento di A rispetto all'insieme universale U (in questo caso U = {0, 1}); Un insieme di porte logiche collegate tra loro, formano una cosiddetta rete combinatoria o R.C

I teoremi dell'algebra di Boole hanno proprio lo scopo di studiare, risolvere e semplificare le R.C

ALTRE PORTE IMPORTANTI

­ Insiemi/Sistemi funzionalmente completi

COME SI SELEZIONA L'INDIRIZZO?

IL DECODER

Multiplexer e Demultiplexer

Il Multiplexer o MUX rappresenta un commutatore elettronico: riceve in ingresso n segnali logici ed è in grado di selezionare in uscita uno solo di essi. per selezionare una tra n possibili linee in ingresso, abbiamo bisogno di m linee di selezione con: 2m = n ⇒ m = log2n esempio: MUX a n=4 ingressi ⇒ m=2 linee di selezione; con 2 bit possiamo gestire 22=4 configurazioni diverse (4 numeri binari differenti). colleghiamo i 4 ingressi del MUX a 4 porte AND

grazie alle 2 linee di selezione possiamo abilitare solo una delle porte AND che trasferisce in uscita l'ingresso ad essa collegato. (MUX da 4 a 1)

L'ingresso E (Enable) permette di attivare o disattivare l'intero MUX

Le 2 linee S0 e S1 rappresentano gli ingressi di selezione ponendo ora E=0 (MUX attivo)

* Se S0 = 0 e S1 = 0 si ottiene Y = a0.

* Se S0 = 1 e S1 = 0 si ottiene Y = a1.

* Se S0 = 0 e S1 = 1 si ottiene Y = a2.

* Se S0 = 1 e S1 = 1 si ottiene Y = a3. Demultiplexer o DMUX

il DMUX riceve in ingresso un unico segnale logico, ed è in grado di trasferirlo su una sola tra le n linee di uscita: m = log2n linee di selezione. struttura della R.C. che implementa un DMUX a 1 ingresso e 4 uscite ( DMUX da 1 a 4)

S0 e S1 sono gli ingressi di selezione, D è l'unico ingresso per i dati, E l'ingresso di abilitazione;

le 4 uscite del DMUX sono Y0, Y1, Y2 e Y3. * Se S0 = 0 e S1 = 0 si ottiene Y0 = 0, Y1 = 1, Y2 = 1, Y3 = 1.

* Se S0 = 1 e S1 = 0 si ottiene Y0 = 1, Y1 = 0, Y2 = 1, Y3 = 1.

* Se S0 = 0 e S1 = 1 si ottiene Y0 = 1, Y1 = 1, Y2 = 0, Y3 = 1.

* Se S0 = 1 e S1 = 1 si ottiene Y0 = 1, Y1 = 1, Y2 = 1, Y3 = 0. Comparazione tra numeri binari

–

–

–

istruzioni per il controllo del flusso: permettono ad un programma di prendere delle decisioni in base al risultato di una operazione appena eseguita;

IF, THEN, ELSE, DO WHILE, REPEAT UNTIL, etc. Dal punto di vista della CPU tutte queste istruzioni si traducono in una serie di confronti tra numeri binari; tutte le CPU sono dotate di apposite R.C. che permettono di effettuare comparazioni tra numeri binari. •

•

Il confronto ha senso solo se i due numeri binari

hanno lo stesso numero di bit. Due numeri binari sono uguali quando

hanno i bit corrispondenti (di pari posizione) uguali tra loro; esempio: confronto tra nibble (1 nibble == 4 bit;1 byte == 8 bit)

la prima uscita (quella più in alto) presenta un livello logico alto solo se Ai è maggiore di Bi (cioè Ai=1 e Bi=0); la seconda uscita presenta un livello logico alto solo se Ai è uguale a Bi (cioè Ai=0 e Bi=0, oppure Ai=1 e Bi=1). La terza uscita infine presenta un livello logico alto solo se Ai è minore di Bi (cioè Ai=0 e Bi=1). ­ presenza di tre connessioni I1, I2 e I3; servono per il collegamento in parallelo di due o più comparatori quando si ha la necessità di confrontare tra loro numeri con più di 4 bit. Addizione tra numeri binari: Half Adder

Full Adder

Una volta realizzati l'H.A. e il F.A., possiamo realizzare circuiti per sommare numeri binari di qualsiasi dimensione (si deve tener conto del riporto.....)

l riporto finale C3 contiene il valore (0 o 1) che verrà assegnato al Carry Flag (nel registro dei flags) Anche nel caso dell'addizione (e di tutte le altre operazioni), un computer con architettura, ad esempio, a 16 bit, sarà dotato di circuiti in grado di sommare via hardware numeri a 16 bit; se vogliamo sommare tra loro numeri a 32 bit, dobbiamo procedere via software suddividendo i bit degli addendi in gruppi da 16. Circuiti complementatori

Principio: 1 ­ n2 = n1 + (­n2) l'opposto di un numero binario si ottiene effettuando il complemento a 2 del numero stesso.

uso una R.C. in grado di eseguire anche altre operazioni

* Per S0 = 0 e S1 = 0 si ottiene in uscita il complemento a 1 del nibble in ingresso. * Per S0 = 0 e S1 = 1 si ottiene in uscita lo stesso nibble in ingresso. * Per S0 = 1 e S1 = 0 si ottiene in uscita il nibble 1111b. * Per S0 = 1 e S1 = 1 si ottiene in uscita il nibble 0000b. Il programma

Macchina di Von Neumann: la memoria è destinata a contenere non solo i dati da elaborare, ma anche le relative istruzioni di elaborazione; nel loro insieme i dati da elaborare e le istruzioni di elaborazione formano un cosiddetto programma:

–

–

–

area memoria dati in ingresso e in uscita ⇒ il blocco dati del programma.

altra area della memoria alle istruzioni ⇒ il blocco codice del programma

Inizializziamo un apposito contatore caricando in esso l'indirizzo di memoria dove si trova la prima istruzione da eseguire; a questo punto il controllo passa alla CPU che può iniziare la fase di elaborazione del programma. esempio: il contatore inizialmente contiene l'indirizzo 0000: Indirizzo 0000 0001 0002 0003 0004 0005 0006 0007 –

–

Contenuto Leggi il dato contenuto in 0005 Leggi il dato contenuto in 0006 Somma i due dati Scrivi il risultato in 0007 Fine programma 3500 2300 ­­­­ La CPU va all'indirizzo 0000 dove trova una istruzione che consiste nella lettura del dato (3500) che si trova in memoria all'indirizzo 0005; mentre la CPU esegue questa istruzione, il contatore viene incrementato di 1 e il suo contenuto diventa quindi 0001.

La CPU va all'indirizzo 0001 dove trova una istruzione che consiste nella lettura del dato (2300) che si trova in memoria all'indirizzo 0006; mentre la CPU esegue questa istruzione, il contatore viene –

–

–

incrementato di 1 e il suo contenuto diventa quindi 0002. La CPU va all'indirizzo 0002 dove trova una istruzione che consiste nel calcolo della somma dei due dati appena letti dalla memoria; mentre la CPU esegue questa istruzione, il contatore viene incrementato di 1 e il suo contenuto diventa quindi 0003. La CPU va all'indirizzo 0003 dove trova una istruzione che consiste nel salvare il risultato della somma (5800) nella cella di memoria 0007; la cella 0007 è inizialmente vuota ed è destinata a contenere il risultato delle elaborazioni effettuate dalla CPU. Mentre la CPU esegue questa istruzione, il contatore viene incrementato di 1 e il suo contenuto diventa quindi 0004. La CPU va all'indirizzo 0004 dove trova una istruzione che segnala la fine delle elaborazioni; a questo punto la CPU entra in pausa in attesa di ulteriori richieste di elaborazione. elevatissima flessibilità! le varie istruzioni devono appartenere ad un insieme riconosciuto dalla CPU; questo insieme viene definito set di istruzioni della CPU. ! logica programmabile ⇒ poter svolgere praticamente un numero illimitato di compiti differenti; ingrandimento della struttura interna della CPU Intel Pentium I: integra al suo interno circa 3100000 transistor! principio di funzionamento di una CPU: –

–

–

ciascuna istruzione appartenente al programma da eseguire, viene codificata attraverso il relativo codice macchina.

L'esecuzione di una determinata istruzione consiste nell'invio alla CPU della sequenza di segnali logici che codificano l'istruzione stessa; questi segnali selezionano all'interno della CPU l'apposita R.C. che esegue l'istruzione desiderata. l'unico linguaggio capito dalla CPU è il codice macchina

la CPU ha la necessità di comunicare con tutti gli altri dispositivi del computer, che vengono chiamati periferiche: la più importante di tutte è la memoria Tutte le altre periferiche vengono trattate come secondarie e vengono anche chiamate dispositivi di I/O (input/output); tra i vari dispositivi di I/O che usualmente risultano collegati al computer si possono citare: tastiere, mouse, monitor, stampanti, plotter, scanner, schede audio, schede video, joystick, hard disk, lettori di floppy disk, lettori CD, etc. Esistono dispositivi accessibili, sia in lettura che in scrittura (memoria centrale, hard disk, floppy disk), altri accessibili solo in lettura (mouse, joystick) e altri ancora accessibili solo in scrittura (stampanti, plotter). ­ Affinché sia possibile l'interscambio di dati, la CPU viene connessa a tutte le periferiche attraverso una serie di linee elettriche che nel loro insieme formano il cosiddetto Data Bus (bus dei dati); su ciascuna linea elettrica del Data Bus transita uno dei bit del dato da trasferire. –

–

–

–

la CPU per poter dialogare con una periferica deve conoscerne l'indirizzo!

nel caso della memoria le varie celle vengono identificate attraverso un indirizzo rappresentato da un numero intero. per tutte le altre periferiche si utilizza lo stesso procedimento; ad ogni periferica viene associato quindi un determinato numero intero che rappresenta l'indirizzo che identifica in modo univoco la periferica stessa. questo indirizzo deve essere rappresentato sotto forma di segnali logici e cioè, sotto forma di codice binario. –

–

la CPU viene connessa a tutte le periferiche attraverso una serie di linee elettriche che nel loro insieme formano il cosiddetto Address Bus (bus degli indirizzi); su ciascuna linea elettrica dell'Address Bus transita uno dei bit del numero binario che rappresenta l'indirizzo a cui la CPU vuole accedere. Tutto il sistema viene coordinato da un apposito circuito di controllo

la CPU viene connessa a tutte le periferiche attraverso una serie di linee elettriche che nel loro insieme formano il cosiddetto Control Bus (bus di controllo); sul Control Bus transitano dei valori binari che codificano i vari segnali di controllo necessari per il coordinamento di tutto il sistema. l'ampiezza dell'Address Bus, il numero di linee da cui è composto, determina la quantità massima di memoria fisicamente indirizzabile dalla CPU. Complessivamente quindi possiamo specificare gli indirizzi relativi a 2n celle di memoria distinte

CPU Address Bus (bit) Memoria fisica (byte) 8080 16 65536 8086 20 1048576 80286 24 16777216 80386 32 4294967296 80486 32 4294967296 80586 32 4294967296 –

–

–

–

–

anche i vari dispositivi di I/O vengono indirizzati con la stessa tecnica utilizzata per la memoria centrale;

ad ogni dispositivo di I/O viene assegnato un numero intero che ne rappresenta in modo univoco l'indirizzo. la CU fare in modo che l'indirizzo di una periferica secondaria non venga confuso con l'indirizzo di una cella della memoria centrale. Ciascuna periferica secondaria è dotata di una memoria propria che nella gran parte dei casi ammonta a pochi byte; questa piccola area di memoria viene chiamata porta hardware

Per indirizzare questa categoria di periferiche secondarie la CPU utilizza una parte delle linee dell'Address Bus; –

–

–

–

–

nell vecchie CPU come l'8086 venivano utilizzate solo le prime 8 linee dell'Address Bus (da A0 a A7) con la possibilità quindi di gestire sino a 28=256 periferiche differenti. A partire dalle CPU 80386 vengono, invece, utilizzate le prime 16 linee dell'Address Bus (da A0 a A15); in questo caso è possibile gestire sino a 216=65536 periferiche differenti

L'ampiezza del Data Bus e cioè, il numero di linee da cui è composto, determina l'ampiezza massima in bit che possono avere i dati gestiti via hardware dalla CPU; osserviamo, infatti, che su un Data Bus formato, ad esempio, da 16 linee possono transitare numeri binari formati al massimo da 16 bit.

l'ampiezza del Data Bus definisce la cosiddetta architettura della CPU; una CPU con architettura a n bit (cioè con Data Bus a n linee) è dotata di R.C. in grado di eseguire via hardware operazioni logico aritmetiche su numeri binari a n bit. influisce sulle caratteristiche dei vari tipi di dati che possiamo simulare via hardware con la CPU;

con n bit possiamo rappresentare, tutti i numeri interi senza segno compresi tra: 0 e 2n­1 e tutti i numeri interi con segno compresi tra: ­(2n­1) e +(2n­1­1) CPU Data Bus(bit) Numeri Senza Segno Numeri Con Segno min. max. 8080 8 8086 16 80286 16 80386 32 80486 32 80586 64 0 255 0 65535 0 65535 0 4294967295 0 4294967295 –

–

–

­128 +127 ­32768 +32767 ­32768 +32767 ­2147483648 +2147483647 ­2147483648 +2147483647 0 18446744073709551615 ­9223372036854775808 +9223372036854775807 notevole aumento della complessità circuitale: una CPU con Data Bus a n linee deve essere in grado di manipolare numeri binari a n bit, eseguire operazioni logico aritmetiche su numeri binari a n bit;

aumentano in modo considerevole le porte logiche delle R.C. che eseguono queste operazioni.

la CPU AMD Athlon, ad esempio, integra al suo interno circa 22000000 di transistor! la CPU Intel 8080

esempio: l'8080 è una CPU con architettura a 8 bit e dispone di un Address Bus a 16 linee con la possibilità quindi di indirizzare fino a 216=65536 byte di RAM fisica; Data Bus (da D0 a D7) ­ Address Bus (da A0 a A15). –

–

–

–

chip 8228 (System Control) ⇒ presenza del Control Bus a 5 linee: su queste 5 linee transitano i segnali di controllo chiamati INTA, MEMR, MEMW, I/OR e I/OW. CLK1 e CLK2 vengono generati dal chip 8224 ed hanno la funzione di segnali di riferimento

CLKe rappresenta il cosiddetto intervallo di tempo elementare della CPU; si tratta cioè dell'intervallo di tempo minimo, necessario alla CPU per eseguire le operazioni hardware di base come l'abilitazione della memoria, l'abilitazione di un bus etc

l'8086 ha una frequenza di clock di circa 5 MHz ed esegue una moltiplicazione tra numeri interi in oltre 100 cicli di clock pari a: 100 / 5000000 = 0.00002 secondi = 20000 nanosecondi L'80486 ha una frequenza di clock di 33 MHz e per la stessa operazione richiede poco più di 10 cicli di clock: 10 / 33000000 = 0.0000003 secondi = 300 nanosecondi MEMORIA

–

–

–

–

–

–

La CPU vede la memoria di lavoro come un vettore di celle, cioè come una sequenza di celle consecutive e contigue; ciascuna cella ha una ampiezza pari a 8 bit

ogni cella viene individuata univocamente dal relativo indice che coincide esattamente con l'indirizzo fisico della cella stessa; se la CPU vuole accedere ad una di queste celle, deve specificare il relativo indirizzo che viene poi caricato sull'Address Bus

le memorie di lavoro vengono organizzate sotto forma di matrice di celle

l'organizzazione a matrice permette alla CPU di accedere a qualsiasi cella di memoria in un intervallo di tempo costante; la CPU non deve fare altro che specificare l'indice di riga e di colonna della cella es: suddividiamo le 5 linee dell'Address Bus in due gruppi; log28=3 linee (A2, A3 e A4), e log24=2 linee (A0 e A1). La parte di indirizzo contenuta nelle linee A2, A3 e A4, raggiunge il circuito chiamato Decodifica Riga; questo circuito provvede a ricavare l'indice di riga della cella da abilitare. La parte di indirizzo contenuta nelle linee A0 e A1, raggiunge il circuito chiamato Decodifica Colonna;

il Data Bus viene connesso alla cella abilitata rendendo così possibile il trasferimento dati tra la cella stessa e la CPU

Reti sequenziali

­ circuito logico capace di ricordare gli stati assunti in precedenza ⇒ retroazione

la porta NAND produce in uscita un livello logico 0 solo quando tutti gli ingressi sono a livello logico 1; in tutti gli altri casi, si otterrà in uscita un livello logico 1. ingresso S=1, R=1, Q e Q' assumono una configurazione del tutto casuale: le due uniche possibilità (stabili) sono Q=0, Q'=1, oppure Q=1, Q'=0.

Partiamo da R=1, S=1 e tenendo R=1 portiamo l'ingresso S a 0; la porta A, avendo un ingresso a 0, produrrà in uscita un 1. La porta B produrrà in uscita 0; a questo punto, qualsiasi modifica apportata a S (purché R resti a 1) non modificherà l'uscita Q che resterà1. il FF­SR memorizza un bit che vale 1 ed è disponibile sull'uscita Q; questa situazione permane inalterata finché R continua a valere 1. R = 0, S=1: la porta B produrrà in uscita 1, la porta A produrrà in uscita 0; finché S rimane a 1 qualsiasi modifica apportata all'ingresso R non altera l'uscita Q che continuerà a valere 0. il FF­SR memorizza un bit che vale 0 ed è disponibile sull'uscita Q. il FF­SR rappresenta una unità elementare di memoria capace di memorizzare un solo bit; infatti: * Attraverso l'ingresso S è possibile scrivere un 1 (set) nel FF­SR

•

Attraverso l'ingresso R è possibile scrivere uno 0 (reset) nel FF­SR

•

Attraverso l'uscita Q è possibile leggere il bit memorizzato nel FF­SR.

Il flip­flop data ( FF­D)

finché l'ingresso CKI è a 0, la porta AND a sinistra produrrà in uscita un livello logico 0 che andrà a raggiungere entrambe le porte NAND A e B, che a loro volta produrranno in uscita un livello logico 1; le due porte NAND A' e B' costituiscono un FF­SR che si troverà di conseguenza nella configurazione iniziale S=1, R=1. Partendo da questa configurazione iniziale e abilitando l'ingresso CKI, il segnale di clock può giungere alle due porte A e B e in un ciclo completo il bit che arriva dall'ingresso D verrà copiato sull'uscita Q; riportando ora a livello logico 0 l'ingresso CKI, il bit appena copiato sull'uscita Q resterà "imprigionato" indipendentemente dal valore dell'ingresso D (per questo motivo il FF­D viene anche chiamato latch, che in inglese significa lucchetto). Registri paralleli in fase di scrittura, i bit arrivano in parallelo (e tutti nello stesso istante) sugli ingressi D, mentre in fase di lettura, i bit vengono letti sempre in parallelo (e tutti nello stesso istante) dalle uscite Q. basta inviare un solo ciclo di clock per copiare in un colpo solo i 4 bit sulle rispettive uscite. Per leggere il dato appena memorizzato, basta leggere direttamente le 4 uscite Q3, Q2, Q1, Q0; la lettura avviene senza distruggere il dato stesso. si hanno n linee di ingresso e n linee di uscita

Memorie RAM statiche (SRAM) se le varie celle vengono realizzate con i FF, otteniamo una memoria di lavoro organizzata sotto forma di matrice di registri

le informazioni memorizzate in una RAM di questo tipo, si conservano inalterate senza la necessità di ulteriori interventi esterni (Power On!!) ⇒ conserva staticamente le informazioni ­ SRAM. –

–

–

tempi di accesso estremamente ridotti, mediamente dell'ordine di una decina di nanosecondi (1 nanosecondo = un miliardesimo di secondo = 10­9 secondi)

questo aspetto è fondamentale per le prestazioni del computer in quanto buona parte del lavoro svolto dalla CPU consiste proprio nell'accedere alla memoria.

necessità di realizzare memorie di lavoro di grosse dimensioni! (centinaia di Mb): circuiti eccessivamente complessi, con centinaia di milioni di porte logiche, centinaia di milioni di linee di collegamento, elevato ingombro, costo eccessivo, etc. tutti i moderni PC sono dotati di memoria centrale di tipo dinamico

Memorie RAM dinamiche (DRAM) condensatore: possiamo associare il livello logico 0 al condensatore scarico (0V) e il livello logico 1 al condensatore carico

–

–

–

–

–

–

–

memorie di lavoro di notevoli dimensioni

elevatissima densità di integrazione costo di produzione estremamente ridotto organizzazione interna: le DRAM vengono strutturate sotto forma di matrice rettangolare di celle esattamente come avviene per le SRAM.

a causa degli inevitabili fenomeni di dispersione elettrica, un condensatore si scarica nel giro di poche decine di millisecondi.

tutte le memorie DRAM necessitano di un apposito dispositivo esterno che provvede ad effettuare periodicamente una operazione refreshing delle celle le operazioni di carica e scarica dei condensatori richiedono tempi relativamente elevati: le DRAM presentano mediamente tempi di accesso pari a 60, 70 nanosecondi (da confrontare con CPU)

Memorie ROM

Read Only Memory (memoria a sola lettura): memorie accessibili solo in lettura per conservare dati e istruzioni la cui modifica potrebbe compromettere il funzionamento del computer.

In realtà la memoria ROM non contiene nessuna informazione al suo interno: queste informazioni si vengono a creare automaticamente nel momento in cui la ROM viene alimentata e indirizzata. PROM o Programmable ROM (ROM programmabili): sono molto simili alle ROM ma si differenziano per il fatto di contenere al loro interno dei microfusibili (uno per ogni transistor): attraverso una apposita apparecchiatura è possibile far bruciare alcuni di questi microfusibili in modo da impostare la struttura interna della PROM a seconda delle proprie esigenze. le PROM possono essere programmate una sola volta

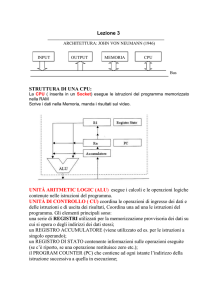

EPROM o Erasable Programmable ROM (ROM programmabili e cancellabili). NOVRAM o Non Volatile RAM (RAM non volatili): vengono ottenute associando una RAM con una EPROM aventi la stessa capacità di memorizzazione in byte. In fase operativa, tutte le operazioni di I/O vengono effettuate ad alta velocità sulla RAM; nel momento in cui si vuole spegnere l'apparecchiatura su cui è installata la NOVRAM, tutto il contenuto della RAM viene copiato in modo permanente nella EPROM. Architettura generale della CPU

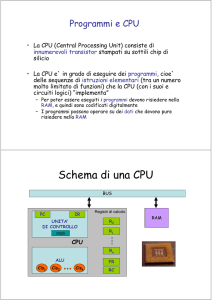

La struttura interna di una CPU varia enormemente da modello a modello; in generale però alcune parti sono sempre presenti secondo lo schema a blocchi:

lo scambio di dati tra i vari blocchi della CPU avviene attraverso un apposito bus chiamato Internal Bus (bus interno), dotato di un numero di linee che nel caso generale rispecchia l'architettura della stessa CPU La ALU mette a disposizione una serie di operazioni basilari: addizione, sottrazione, moltiplicazione, divisione, shift a destra e a sinistra, complementazione dei bit, operatori logici AND, OR, EX­OR ........

La ALU deve essere in grado di operare su dati la cui dimensione in bit rispecchia l'architettura della CPU; La ALU non è dotata di memoria propria per cui deve servirsi di apposite memorie esterne: Registri temporanei, Registri generali e Flags (registro dei flags). I registri temporanei hanno il compito di memorizzare temporaneamente i dati (operandi) sui quali la ALU deve eseguire una determinata operazione logico aritmetica; ogni volta che arrivano nuovi dati da elaborare, il vecchio contenuto dei registri temporanei viene sovrascritto. I registri generali rappresentano una vera e propria memoria RAM interna velocissima, che viene utilizzata per svolgere svariate funzioni: contengono dati in arrivo dalle periferiche (cioè dalla RAM o dai dispositivi di I/O), dati destinati alle periferiche, risultati di operazioni appena eseguite dalla ALU...

la ALU è collegata direttamente ai registri generali della CPU che hanno tempi di accesso nettamente inferiori rispetto alle locazioni della RAM

tutte le operazioni che coinvolgono dati presenti nei registri, vengono svolte dalla ALU molto più velocemente rispetto al caso in cui i dati si trovino, invece, in RAM. alcuni linguaggi di programmazione di alto livello danno la possibilità al programmatore di richiedere l'inserimento di determinati dati del programma, direttamente nei registri della CPU; il linguaggio C, ad esempio, mette a disposizione la parola chiave register che applicata ad un dato (intero), indica al compilatore C di inserire, se è possibile, quel dato in un registro libero della CPU

la Control Logic o CL (logica di controllo) ha il compito di gestire tutto il funzionamento della CPU:

stabilisce quale dei dispositivi deve ricevere il controllo, che compito deve eseguire questo dispositivo, quali dispositivi devono essere, invece, inibiti

l'8086: registri interni (tutti a 16 bit) CS è destinato a contenere la componente Seg del Code Segment;

DS è destinato a contenere la componente Seg del Data Segment;

SS è destinato a contenere la componente Seg dello Stack Segment. ES permette di gestire la componente Seg di un secondo Data Segment (possibilità di gestire contemporaneamente due Data Segment distinti): I registri speciali sono tutti registri puntatori; il loro scopo quindi è quello di gestire componenti Offset relative ai vari segmenti di programma. IP fa coppia con CS: è destinato a contenere la componente Offset dell'indirizzo della prossima istruzione da eseguire

Il compito di inizializzare la coppia CS:IP spetta al linker

In fase di esecuzione di un programma, la gestione di CS:IP passa alla CPU che provvede ad aggiornare istante per istante IP (e se necessario anche CS) SP e BP fanno coppia normalmente con SS e sono quindi destinati a contenere componenti Offset relative allo Stack Segment del programma. SP rappresenta il TOS dello stack. Il registro BP può essere utilizzato per muoversi all'interno dello stack: nei linguaggi di alto livello ha il compito di indirizzare le variabili locali e la lista dei parametri dei sottoprogrammi

Registri generali: AX, BX, CX e DX

contengono dati che devono essere velocemente elaborati dalla ALU

AX : accumulatore, viene utilizzato dalla CPU come registro predefinito per numerose operazioni:

moltiplicazioni, divisioni, comparazioni, etc. Un altro impiego predefinito di AX è quello di registro destinazione o sorgente per lo scambio di dati con le periferiche di I/O;

BX può essere usato, sia come registro generale, sia come registro puntatore

CX viene chiamato contatore in quanto la CPU lo utilizza in diverse istruzioni come registro predefinito per effettuare dei conteggi

DX, viene chiamato registro dati in quanto il suo ruolo predefinito è quello di contenere dati da impiegare come operandi in varie operazioni logico aritmetiche; questo registro viene anche impiegato per contenere l'indirizzo di una porta hardware che deve comunicare con la CPU. RAM ROM

la ram contiene anche il MAR e il MDR:

Memory Address Register: contiene l'indirizzo della cella da cui leggere o su cui scrivere e lo passa al decoder

Memory Data Register: contiene temporaneamente i dati – stessa dimensione delle celle di memoria

•

•

•

•

•

•

FASE DI SCRITTURA

si trasferisce il dato in MDR e l'indirizzo in MAR

si attiva la scrittura si scrive al segnale di CLOCK

FASE DI LETTURA

si trasferisce in MAR l'indirizzo della cella

si attiva la lettura

si trasferisce il dato in MDR al CLOCK L' unita' di controllo gestisce l'hardware:

trasmette i segnali di controllo a tutte le altre componenti permettendo lo scambio di dati e di istruzioni. Essa contiene:

•

•

•

•

Il Program Counter: tiene il segno della posizione dell'istruzione da prelvare

Il Registro di Istruzione (IR): prende il dato da MDR e separa il Codice Operativo (in linguaggio macchina) dall' indirizzo dell'operando. Il Decodificatore delle istruzioni: controlla il codice operativo e determina le istruzioni da eseguire. Ha tante uscite quanti sono i tipi di istruzione. Invia il segnale al generatore dei segnali di controllo Il Generatore dei segnali di controllo: in base all'istruzione ricevuta emette i corrispondenti segnali

SCHEMA DI HARD DISK

Tracce :: Settori :: Cilindri

settore: 512 byte + preambolo + ECC

tracce: 800­2000/cm larghe 5­10 micron

Prestazioni: seek time (radiale) 5­15 ms, di rotazione

3600­5400­7200­10800 RPM :: 4­8ms

Trasferimento: 5­20 MB/s << del seek time