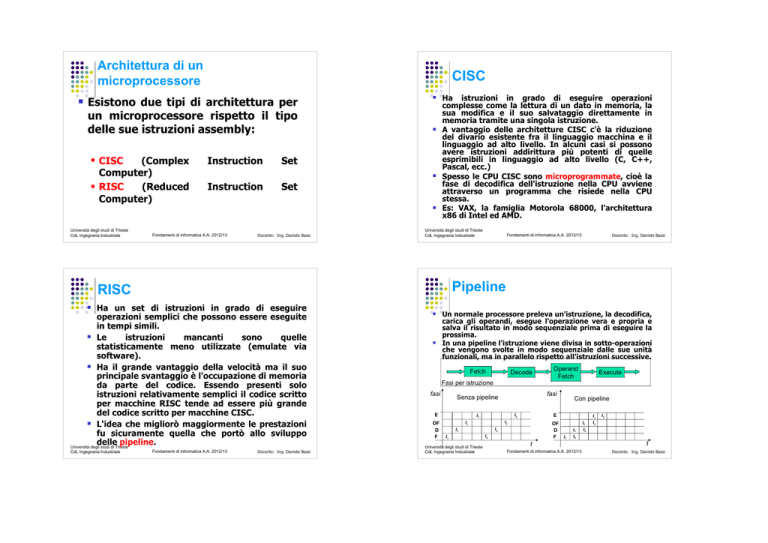

Architettura di un

microprocessore

CISC

Ha istruzioni in grado di eseguire operazioni

complesse come la lettura di un dato in memoria, la

sua modifica e il suo salvataggio direttamente in

memoria tramite una singola istruzione.

A vantaggio delle architetture CISC c'è la riduzione

del divario esistente fra il linguaggio macchina e il

linguaggio ad alto livello. In alcuni casi si possono

avere istruzioni addirittura più potenti di quelle

esprimibili in linguaggio ad alto livello (C, C++,

Pascal, ecc.)

Spesso le CPU CISC sono microprogrammate, cioè la

fase di decodifica dell'istruzione nella CPU avviene

attraverso un programma che risiede nella CPU

stessa.

Es: VAX, la famiglia Motorola 68000, l'architettura

x86 di Intel ed AMD.

Esistono due tipi di architettura per

un microprocessore rispetto il tipo

delle sue istruzioni assembly:

CISC

(Complex

Computer)

RISC

(Reduced

Computer)

Università degli studi di Trieste

CdL Ingegneria Industriale

Instruction

Set

Instruction

Set

Fondamenti di informatica A.A. 2012/13

Docente: Ing. Daniele Bassi

Università degli studi di Trieste

CdL Ingegneria Industriale

Docente: Ing. Daniele Bassi

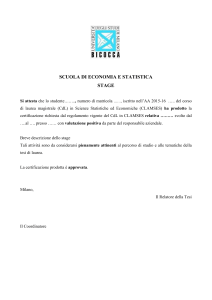

Pipeline

RISC

Ha un set di istruzioni in grado di eseguire

operazioni semplici che possono essere eseguite

in tempi simili.

Le

istruzioni

mancanti

sono

quelle

statisticamente meno utilizzate (emulate via

software).

Ha il grande vantaggio della velocità ma il suo

principale svantaggio è l'occupazione di memoria

da parte del codice. Essendo presenti solo

istruzioni relativamente semplici il codice scritto

per macchine RISC tende ad essere più grande

del codice scritto per macchine CISC.

L'idea che migliorò maggiormente le prestazioni

fu sicuramente quella che portò allo sviluppo

delle pipeline.

Università degli studi di Trieste

CdL Ingegneria Industriale

Fondamenti di informatica A.A. 2012/13

Fondamenti di informatica A.A. 2012/13

Docente: Ing. Daniele Bassi

Un normale processore preleva un'istruzione, la decodifica,

carica gli operandi, esegue l'operazione vera e propria e

salva il risultato in modo sequenziale prima di eseguire la

prossima.

In una pipeline l'istruzione viene divisa in sotto-operazioni

che vengono svolte in modo sequenziale dalle sue unità

funzionali, ma in parallelo rispetto all’istruzioni successive.

Fetch

Decode

Operand

Fetch

Execute

Fasi per istruzione

fasi

E

OF

D

F

fasi

Senza pipeline

I2

I1

Università degli studi di Trieste

CdL Ingegneria Industriale

OF

D

F I1

I2

I1

I1

E

I2

I1

Con pipeline

I2

I1

I1

I1

I2

I2

I2

I2

t

Fondamenti di informatica A.A. 2012/13

t

Docente: Ing. Daniele Bassi

Processori superscalari

Un'altra

strategia

per

incrementare

le

prestazioni prevedeva la creazione di più unità

funzionali che lavorassero in parallelo. Per

esempio un processore con due unità aritmetiche

può lavorare in parallelo su sue istruzioni di

somma raddoppiando le prestazioni.

Questa replicazione delle unità funzionali

combinate con le pipeline portarono alla

realizzazione di processori superscalari in grado

di eseguire più di un'operazione per ciclo di

clock.

I processori di nuova generazione adottano

questa tecnologia (es: Intel Pentium)

Università degli studi di Trieste

CdL Ingegneria Industriale

Fondamenti di informatica A.A. 2012/13

Docente: Ing. Daniele Bassi