Processore

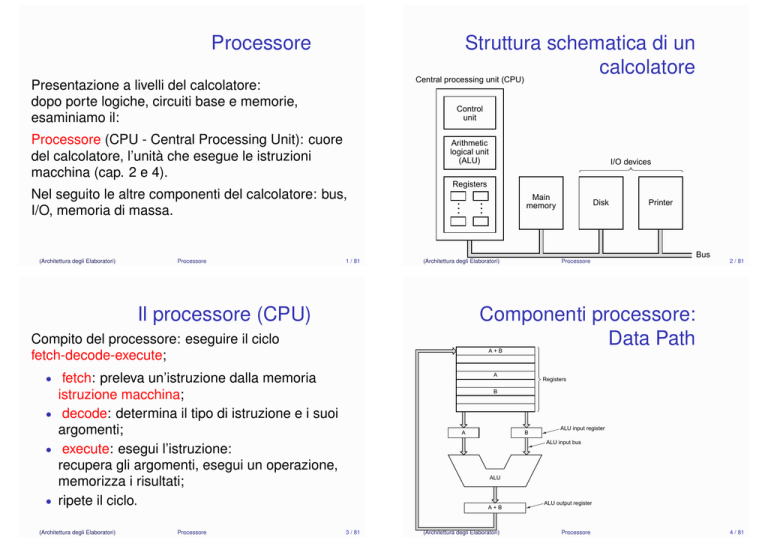

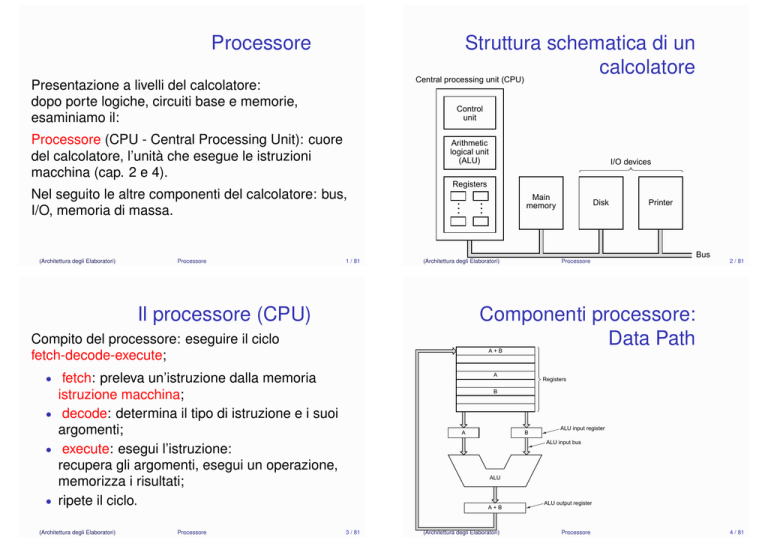

Struttura schematica di un

calcolatore

Central processing unit (CPU)

Presentazione a livelli del calcolatore:

dopo porte logiche, circuiti base e memorie,

esaminiamo il:

Control

unit

Processore (CPU - Central Processing Unit): cuore

del calcolatore, l’unità che esegue le istruzioni

macchina (cap. 2 e 4).

Arithmetic

logical unit

(ALU)

I/O devices

Registers

Processore

1 / 81

Main

memory

…

(Architettura degli Elaboratori)

…

Nel seguito le altre componenti del calcolatore: bus,

I/O, memoria di massa.

(Architettura degli Elaboratori)

Il processore (CPU)

Processore

Bus

2 / 81

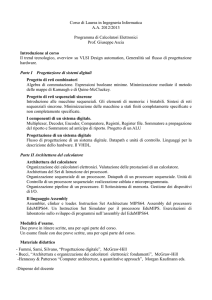

A+B

• fetch: preleva un’istruzione dalla memoria

A

istruzione macchina;

• decode: determina il tipo di istruzione e i suoi

argomenti;

• execute: esegui l’istruzione:

recupera gli argomenti, esegui un operazione,

memorizza i risultati;

• ripete il ciclo.

B

Processore

Printer

Componenti processore:

Data Path

Compito del processore: eseguire il ciclo

fetch-decode-execute;

(Architettura degli Elaboratori)

Disk

A

Registers

B

ALU input register

ALU input bus

ALU

A+B

3 / 81

(Architettura degli Elaboratori)

ALU output register

Processore

4 / 81

Data Path

Micro-operazione

L’operazione eseguibile dal data path in un singolo

ciclo di clock.

Formata da:

Azioni eseguibili da una micro-operazione:

• una singola operazione aritmetica-logica (i cui

argomenti e risultato risiedono nei registri).

• una comunicare con la memoria (richiesta di

lettura o scrittura di una locazione)

Un’istruzione macchina viene eseguita mediante

una o più micro-operazioni.

• una serie di registri (memorie),

• un’unità aritmetica e logica (ALU),

• dei bus di collegamento.

Può eseguire micro-operazioni.

(Architettura degli Elaboratori)

Processore

5 / 81

(Architettura degli Elaboratori)

Unità di controllo

• Esamina l’istruzione corrente, contenuta

Instruction Register (IR).

• Invia segnali di lettura e scrittura ai registri.

• Invia segnali di controllo alla ALU.

• Gestisce la comunicazione con la memoria

principale.

Processore

6 / 81

Realizzazione

Il funzionamento del data path viene regolato,

mediante segnali, dall’unità di controllo.

Circuito sequenziale che regola il funzionamento del

processore.

(Architettura degli Elaboratori)

Processore

7 / 81

Due alternative:

• cablata: si realizza un circuito sequenziale

classico;

• micro-programmata: il controllo è un piccolo

calcolatore capace di eseguire un

micro-programma.

(Architettura degli Elaboratori)

Processore

8 / 81

Dicotomia: cablata programmata

Un po’ di storia

I primi processori: poche istruzioni, logica cablata.

Le stessa funzionalità possono essere implementate

mediante:

• hardware (logica cablata): più complicata e

costosa da realizzare, ma offre prestazioni

migliori;

• software (logica programmata): più semplice e

flessibile, ma più lenta.

Diversi esempi di questa dicotomia: le istruzioni

grafiche, l’elaborazione dei segnali, . . .

(Architettura degli Elaboratori)

Processore

9 / 81

Anni 70

Processore

(Architettura degli Elaboratori)

Processore

10 / 81

Anni 80, processori RISC

Le potenzialità della micro-programmazione vengo

sfruttate al massimo.

• Linguaggi macchina sempre più sofisticati, vicini

ai linguaggi di programmazione standard.

• Il calcolatore apice di questa filosofia: VAX

(Digital DEC).

• Motivazioni tecnologiche: all’epoca i

control-store (la memoria micro-programma)

sono molti più veloci della memoria principale

(RAM).

(Architettura degli Elaboratori)

Anni 50:

• prime unità di controllo micro-programmato,

permette la costruzione di calcolatori economici

ma con un ricco insieme di istruzioni.

• calcolatori con maggiori presazioni usano la

logica cablata.

• Si costruiscono calcolatori molto diversi per

prestazioni e costi con lo stesso insieme di

istruzioni. (IBM 360)

11 / 81

Si cambia rotta: poche istruzioni, logica cablata

• le istruzioni complesse non sono così utili

• istruzioni semplici molto più veloci;

• si possono utilizzare controlli cablati;

• la velocità della RAM si avvicina a quella del

control-store

(Architettura degli Elaboratori)

Processore

12 / 81

I primi RISC

Anni 90, diatriba: RISC –

CISC

Reduced Instruction Set Computer

• 801 (IBM),

• CPU-RISC (Patterson - Berkley) ⇒ Sparc,

• MIPS (Hennesey - Stanford),

• Alpha (Digital), PowerPC (Motorola, IBM), ARM,

(Architettura degli Elaboratori)

Processore

13 / 81

Complex Instruction Set Computer.

• Tutti i processori di nuova concezione sono

RISC.

• Ma i processori usati nei PC: architettura Intel

x86, (IA-32), sono CISC.

• Motivi: compatibilità con il software preesistente,

non si vogliono riscrivere i programmi (il codice).

(Architettura degli Elaboratori)

Attualmente

Processore

14 / 81

RISC – CISC

La contrapposizione RISC – CISC è più sfumata.

• La legge di Moore ha portato alla creazione di

processori RISC con insiemi di istruzioni

sempre più ampi.

• Il processori CISC (IA-32) usano al loro interno

un cuore RISC,

istruzioni semplici, più comuni: eseguite

direttamente,

• istruzioni più complesse: scomposte in più istruzioni

semplici,

• istruzioni sofisticate: eseguite mediante

micro-programma.

•

(Architettura degli Elaboratori)

Processore

15 / 81

• In linea di principio, i processori RISC sono

preferibili,

• le architetture CISC hanno uno svantaggio del

(20-30%),

• per i processori x86, lo svantaggio è

compensato dalle economie di scala (vengono

prodotti in gran numero).

(Architettura degli Elaboratori)

Processore

16 / 81

I processori nel libro di

testo

I processori nel libro di

testo

Per illustrare con maggior dettaglio il funzionamento

dei processori,

si mostra un esempio concreto di progettazione di

un processore.

Più precisamente: si mostra come costruire

processore (Mic)

che eseguire istruzioni del Java bytecode:

si realizza la Java Virtual Machine (JVM)

Approccio per esempi e bottom-up: prima

descrizione delle componenti, poi quadro di insieme.

(Architettura degli Elaboratori)

Processore

17 / 81

• Pro: un esempio pratico, consistente con il

resto.

• Contro: presentazione lunga, molti dettagli

tecnici, difficile comprensione, linguaggio

macchina non standard.

• A lezione presentazione più superficiale:

descrizione dei principi, pochi dettagli.

Argomenti affrontati in un ordine diverso.

• Problema: meno correlazione col libro di testo,

non esiste un insieme di pagine che sia

completo, autosufficiente e non sovrabbondante

(Architettura degli Elaboratori)

Processore

18 / 81

(molti più argomenti di quelli presentati a

lezione).

Premessa: i compilatori

Java

Un programma ad alto livello (Java, C, C++,

Scheme, Pascal, . . . ) deve essere tradotto in

linguaggio macchina (istruzioni eseguibili dal

calcolatore).

Java si propone come il linguaggio per le

applicazioni in rete.

I programmi Java devono poter migrare nella rete:

• codice compilato non ha questa possibilità, è

specifico ad una particolare architettura

(processore – sistema operativo),

inoltre: problemi di sicurezza;

• il codice sorgente non può essere spostato in

maniera efficiente.

Due alternative:

• compilatore: programma traduttore, dal

programma sorgente genere un programma

macchina equivalente.

• interprete: programma interprete, legge il

programma sorgente e lo esegue direttamente

(non genera codice intermedio).

(Architettura degli Elaboratori)

Processore

19 / 81

(Architettura degli Elaboratori)

Processore

20 / 81

Java Virtual Machine, JVM

Java bytecode

Soluzione:

• viene definito un codice intermedio (tra Java e il

linguaggio macchina): Java bytecode,

• viene definita un macchina virtuale la Java

Virtual Machine (JVM),

capace di eseguire programmi scritti in Java

bytecode,

macchina virtuale: implementata, via software,

su diverse piattaforme (processore, sistema

operativo),

livello Java bytecode

(Architettura degli Elaboratori)

Processore

21 / 81

Programmi Java compilati in Java bytecode,

eseguibile da ogni calcolatore mediante la

Java Runtime Environment (JRE), composto da:

• JVM (programma interpretare il Java bytecode);

• librerie.

Vantaggi, svantaggi,

• vantaggi: codice universale, compatto, con

meccanismi di protezione;

• svantaggi: minore efficienza rispetto alla

compilazione diretta

(mitigata dai compilatori just-in-time).

(Architettura degli Elaboratori)

Processori Mic (1,2,3,4)

Simili, per molti aspetti, ai linguaggi macchina.

Alcune differenze importanti:

• meccanismi di protezione contro codice

malevolo;

• compatto, istruzioni lunghe un byte (+ un

eventuale argomento di 1-2 byte);

• primitive object-oriented (chiamate dei metodi).

Esistono delle vere implementazioni, de

• picoJava (Sun Microsystems),

• ARM926EJ-S, (architettura ARM estesa con il

Java bytecode),

Processore

22 / 81

Java bytecode

Implementazione hardware, cablata (non virtuale o

programmata) della JVM.

Mic è un processore capace di eseguire un

sottoinsieme del Java bytecode.

Progetto didattico, non esistono implementazioni.

(Architettura degli Elaboratori)

Processore

Per semplicità, i processori Mic implementano un

piccolo sottoinsieme del Java bytecode.

23 / 81

(Architettura degli Elaboratori)

Processore

24 / 81

Il modello di memoria

Il modello di memoria

Memoria standard processori, monolitica, uno

stesso spazio per programmi e dati.

Memoria della JVM è divisa in quattro parti.

• area del codice (programmi)

• area delle costanti (dati utilizza dai programmi)

• stack delle variabili locali

• stack degli operandi (dati su cui eseguire

operazioni)

(Architettura degli Elaboratori)

Processore

25 / 81

(Architettura degli Elaboratori)

Stack delle variabili

Processore

26 / 81

Stack degli operandi

• Usato per gestire le chiamate di procedura

• JVM non è una macchina a registri (come quasi

(metodi).

• Ogni procedura ha le sue variabili, spazio di

memoria.

• Questi spazi gestiti come una pila.

Ad ogni chiamata di procedura si alloca uno

spazio.

Spazio recuperato quando la procedura termina.

tutti i processori).

Le operazioni aritmetiche logiche non fanno

riferimento ai registri interni, ma ad uno:

• Stack degli operandi. Pila su cui:

(Architettura degli Elaboratori)

Processore

27 / 81

•

•

inserire o prelevare word, (sequenze di 32 bit)

eseguire operazioni sugli ultimi dati inseriti.

Esempio la JVM valuta l’espressione

(3 + 5) × (4 + 2) in ...

(Architettura degli Elaboratori)

Processore

28 / 81

I-Java bytecode

Il processore Mic-1

• Operazioni aritmetiche e logiche: IADD, IAND,

Un semplice processore per il Java bytecode.

Funzionamento:

• ad ogni ciclo di clock il data path può eseguire

semplici operazioni, o spostare dati

(micro-istruzione)

• un’istruzione del Java bytecode viene realizzata

mediante una sequenza di micro-istruzioni,

• sequenza composta da diverse parti:

fetch-decode-execute.

IOR, ISUB, IINC vn con.

• Operazioni trasferimento dati, da e per la

memoria: ILOAD vn, ISTORE vn, LDC_W i,

(DUP, POP, SWAP, BIPUSH b).

• Operazioni per il controllo del flusso

dell’esecuzione:

GOTO, IFEQ os, IFLT os, IF_ICMEQ os,

Chiamate di metodi: INVOKEVIRTUAL d,

IRETURN,

• Altro: NOP, WIDE

(Architettura degli Elaboratori)

Processore

29 / 81

(Architettura degli Elaboratori)

Mic-1: data path

Processore

30 / 81

Unità aritmetica-logica

(ALU)

Componente di ogni processore,

può eseguire le operazioni aritmetiche e logiche:

• Ingressi:

•

•

due argomenti: 32, 64 bit;

codifica operazione da eseguire.

• Uscite:

• risultato: 32, 64 bit;

• bit di condizione: segno, zero, overflow.

(Architettura degli Elaboratori)

Processore

31 / 81

(Architettura degli Elaboratori)

Processore

32 / 81

Unità aritmetica-logica

(ALU)

ALU da un bit

Logical unit

MIC1 usa una semplice ALU:

• implementa poche operazioni: AND, OR, NOT,

somma, sottrazione, incremento, decremento 1,

opposto.

• Operazioni eseguite bit per bit (locali): ALU

scomposta in unità elementari, ciascuna

operante su una coppia di bit.

• segnali di controllo: selezionano l’operazione da

svolgere, abilitano o meno gli ingressi,

forniscono il riporto per le cifre meno

significative.

(Architettura degli Elaboratori)

Processore

33 / 81

ALU da 8-32 bit

A7 B7

A6 B6

A5 B5

A4 B4

A3 B3

A2 B2

A1 B1

A0 B0

1-bit

ALU

1-bit

ALU

1-bit

ALU

1-bit

ALU

1-bit

ALU

1-bit

ALU

1-bit

ALU

1-bit

ALU

O7

O6

O5

O4

O3

O2

O1

O0

Carry

in

A+B

Output

B

Sum

Enable

lines

F0

Full

adder

F1

Decoder

Carry out

(Architettura degli Elaboratori)

Processore

34 / 81

Oltre alle ovvie:

• A + B + 1, somma con Carry in = 1

INC

• A + 1, somma con ENB = 0, Carry in = 1

• B − A, somma con INVA = 1, Carry in = 1

• B − 1, somma con ENA = 0, INVA = 1

Carry

out

• −A, somma con ENB = 0, INVA = 1,

Mic 1 contiene una ALU a 32 bit.

(Architettura degli Elaboratori)

AB

INVA

A

ENA

B

ENB

Funzione calcolabili dalla

ALU

ALU completa formata da un sequenza di ALU a 1

bit

F1 F0

Carry in

Processore

Carry in = 1

35 / 81

(Architettura degli Elaboratori)

Processore

36 / 81

Registri (specializzati)

Esempio di

implementazione

• MAR: Memory Address Register,

•

•

•

•

•

MDR: Memory Data Register;

comunicazione memoria dati;

PC: Program Counter,

MBR: Memory Bytecode Register;

comunicazione memoria codice;

SP: Stack Pointer, TOS: Top Of Stack;

stack degli operandi;

LV: Local Variable; puntatore stack variabili;

CPP: Constant Pool Pointer; punt. costanti;

OPC, H: registri ausiliari.

(Architettura degli Elaboratori)

Processore

L’istruzione IADD viene realizzata dalla sequenza di

micro-istruzioni:

• Main1: PC = PC + 1; fetch; goto (MBR)

• iadd1: MAR=SP=SP-1; rd

• iadd2: H = TOS

• iadd3: MDR=TOS=MDR+H; wr; goto Main1

Le altre istruzioni implementate in maniera analoga.

37 / 81

(Architettura degli Elaboratori)

Processore

Circuito di controllo

38 / 81

Circuito di controllo

Memory control signals (rd, wr, fetch)

3

4

Micro-programmato. Formata da memoria ROM

(contiene il micro-codice), 2 registri, un multiplexer.

4-to-16

Decoder

MAR

MDR

MPC

• semplice sia il circuito che la progettazione

O

8

MBR

SP

512 × 36-Bit

control store

for holding

the microprogram

9

LV

• relativamente lento

JMPC

CPP

Processore

Addr

J

ALU

C

MIR

M B

TOS

Micro-istruzioni di 36 bit

• in parte segnali di controllo,

• in parte determinano la prossima

micro-istruzione,

(Architettura degli Elaboratori)

9

PC

JAMN/JAMZ

OPC

H

B bus

2

1-bit flip–flop

N

6

ALU

control

High

bit

ALU

Control

signals

Enable

onto

B bus

Z

Shifter

C bus

39 / 81

(Architettura degli Elaboratori)

2

Write

C bus

to register

Processore

40 / 81

Circuito di controllo:

Control store

(Architettura degli Elaboratori)

Processore

Circuito di controllo

Invia:

• ai registri i segnali di lettura e scrittura;

• alla memoria le istruzioni: read, write, fetch;

• alla ALU il codice dell’istruzione da eseguire.

Determina micro-istruzione successiva via:

• MBR (prima micro-istruzione nelle esecuzione

di un istruzione macchina);

• la micro-istruzione corrente (micro-istruzioni

successive);

• in alcuni casi, il primo bit dell’indirizzo

determinato dall’uscita della ALU (per poter

implementare i salti condizionati).

41 / 81

(Architettura degli Elaboratori)

Prestazioni

Processore

42 / 81

Miglioramento delle

prestazioni

Due metodi:

• Utilizzare istruzioni macchina più potenti, e

flessibili.

Esempi:

MIC-1, processore (relativamente) completo ma

inefficiente (molto più semplice dei processori

attuali).

Processori Intel x86: 8086 (1978) – 80286 – 386

(1985) – MMX — 3DNow — x86-64 (2000) — AVX;

• ARM: ARMv1 — . . . — ARMv8;

• MIPS: R2000 — R3000 — R4000;

• IJVM → JVM.

•

Prestazioni: computazione eseguibile nell’unita di

tempo.

• Eseguire più istruzione nell’unità di tempo

(Architettura degli Elaboratori)

Processore

43 / 81

(Architettura degli Elaboratori)

Processore

44 / 81

Più istruzioni al secondo

Più computazione per ciclo

di clock

Il funzionamento della CPU scandito da un clock,

• diminuire il numero di micro-istruzioni (cicli di

clock) necessari per eseguire un’istruzione

macchina;

aumentare la computazione svolta nel ciclo di

clock:

• ridurre il ciclo di clock.

(Architettura degli Elaboratori)

Processore

Aumentare la potenza di calcolo del data path,

micro-istruzioni più potenti.

• ALU con più operazioni,

• più registri disponibili,

• più possibilità di scambio dati (3 bus distinti)

• un’unità separata per il caricamento delle

istruzioni: Instruction Fetch Unit (IFU)

45 / 81

(Architettura degli Elaboratori)

Secondo progetto MIC-2

Segnale di clock abilita la scrittura dei registri.

Periodo di clock dato dalla somma dei ritardi.

MDR

Registers loaded

instantaneously from

C bus and memory on

rising edge of clock

PC

Instruction

fetch unit

(IFU)

46 / 81

Ridurre il ciclo di clock

Memory

control

registers

MAR

To

and

from

main

memory

Processore

Shifter

output

stable

MBR

MBR2

Cycle 1

starts

here

SP

LV

Control signals

Clock cycle 1

Clock cycle 2

CPP

Enable onto B bus

New MPC used to

load MIR with next

microinstruction here

TOS

Write C bus to register

C bus

∆w

OPC

∆x

∆y

∆z

B bus

H

A bus

ALU

control

6

ALU

Set up

signals

to drive

data path

N

Z

Shifter

ALU

and

shifter

Drive H

(Architettura degli Elaboratori)

Processore

47 / 81

(Architettura degli

Elaboratori)

and

Propagation

from shifter

MPC

available

here

Processore

48 / 81

Ridurre il ciclo di clock

Architettura più veloce

Velocizzare il data-path:

• circuito di controllo cablato,

Due modi:

• migliorare la tecnologici nei circuiti integrati:

transistor più veloci,

• migliorare la strutture dei circuiti: realizzare

circuiti con meno ritardi (a parità di tipo di

transistor impiegati).

(Architettura degli Elaboratori)

Processore

• ALU e circuiti combinatori più veloci, (un intero

settore di ricerca):

l’ALU presentata nel testo particolarmente

inefficiente.

• esecuzione parallela, spezzare l’esecuzione

della micro-operazione in più stadi: la tecnica

della pipeline

49 / 81

(Architettura degli Elaboratori)

Terzo progetto: Mic-3

50 / 81

Mic-3 – Pipeline

Memory

control

registers

MAR

To

and

from

main

memory

Processore

MDR

PC

Instruction

fetch unit

(IFU)

Pipeline:

• l’esecuzione della micro-operazione viene divisa

in più stadi

• ogni stadi eseguito più rapidamente

• i diversi stadi eseguiti in contemporanea su più

istruzioni

MBR1

MBR2

SP

LV

Control signals

CPP

Enable onto B bus

TOS

Write C bus to register

OPC

C bus

B bus

H

A bus

C latch

A latch

ALU

control

B latch

6

ALU

N

Z

Shifter

(Architettura degli Elaboratori)

Processore

51 / 81

(Architettura degli Elaboratori)

Processore

52 / 81

Pipeline – Paragoni

La pipeline, secondo

paragone.

Possibile paragone preso dalla vita comune, una

lavanderia:

vestiti da lavare

micro-operazioni

lavaggio

acquisire i dati di ingresso

asciugatura

calcolo del risultato

stiratura

memorizzazione del risultato

Le varie fasi di lavoro sono portata avanti in parallelo.

(Architettura degli Elaboratori)

Processore

53 / 81

La catena di montaggio:

il lavoro viene scomposto in fasi, ognuna eseguita da

un dispositivo specifico,

si svolgono le diverse fasi, su componenti diverse, in

parallelo.

In un processore si parallelizza l’esecuzione delle

micro-operazioni, (ciclo di clock);

si migliora la banda passante ma non i tempi di

risposta.

Tecnica

in tutti Processore

i processori. In ambito Intel:54 / 81

(Architettura degliutilizzata

Elaboratori)

dal 486 in poi (1989).

Esempio di scomposizione:

Altro esempio:

S1

S2

S3

S4

S5

Instruction

fetch

unit

Instruction

decode

unit

Operand

fetch

unit

Instruction

execution

unit

Write

back

unit

(a)

S1:

1

S2:

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

1

2

3

4

5

6

1

2

3

4

5

6

7

8

9

S3:

S4:

S5:

1

(Architettura degli Elaboratori)

2

3

4

5

Time

(b)

Processore

1

2

3

4

5

6

7

IFU

Decoder

Queue

Operands

Exec

Write

back

Memory

Processori diversi usano scomposizioni, strutture

della pipeline, diverse.

Lunghezza tipica di una pipeline: 7–14 stadi.

Caso limite Pentium IV: 20 stadi di pipeline (guerra

dei GHz).

…

55 / 81

(Architettura degli Elaboratori)

Processore

56 / 81

Processori superscalari

Processori superscalari

Aumentano ulteriormente il parallelismo:

istruzioni

si migliora il rapporto cicli

di clock ,

• I primi stadi (singoli) prelevano più istruzioni

Iniziano contemporaneamente l’esecuzione di più

istruzioni: più pipeline operanti in parallelo.

S1

Instruction

fetch

unit

S2

S3

S4

S5

Instruction

decode

unit

Operand

fetch

unit

Instruction

execution

unit

Write

back

unit

Instruction

decode

unit

Operand

fetch

unit

Instruction

execution

unit

Write

back

unit

(Architettura degli Elaboratori)

Processore

57 / 81

Esempio: processore

SPARC

Fetch

Decode

N1

N2

Group

N3

Register

X1

Processore

58 / 81

Processori superscalari possono, potenzialmente,

eseguire decine di istruzioni contemporaneamente.

Integer pipeline

Cache

(Architettura degli Elaboratori)

Problemi del parallelismo

Pipeline specializzate.

Execute

dalla memoria, e le decodificano.

• Le istruzioni smistate su stadi successivi

multipli.

• Spesso, uno stadio finale singolo che termina, in

ordine, le istruzioni.

X2

Write

Due fenomeni impediscono un completo

sfruttamento del parallelismo.

• Dipendenza tra istruzioni.

X3

• Istruzioni di salto.

Floating-point/graphics pipeline

Attualmente processori con 4-15 pipeline, decine di

micro-istruzione in contemporanea.

(Architettura degli Elaboratori)

Processore

59 / 81

(Architettura degli Elaboratori)

Processore

60 / 81

Dipendenza tra istruzioni:

Dipendenza tra istruzioni

In un programma le istruzioni sono stato pensate per

essere eseguite in ordine.

Un’esecuzione parallela, senza controlli, può portare

a risultati scorretti. Tre casi:

• RAW Read After Write:

R0 = R1

R2 = R0 + 1

• WAR Write After Read:

R1 = R0 +1

R0 = R2

• WAW Write After Write:

R0 = R1

(Architettura degli Elaboratori)

Processore

61 / 81

R0 = R2 + 1

Gestire la dipendenza tra

istruzioni

Processore

Le istruzioni dipendenti devono essere sospese:

decadimento delle prestazioni, eseguiamo meno

operazioni di quelle teoricamente possibili.

Si creano bolle, zone inattive, nella pipeline.

(Architettura degli Elaboratori)

Processore

62 / 81

Istruzioni di salto

condizionato

Tecniche per recuperare le prestazioni perse:

• esecuzione fuori ordine: si mandano in

esecuzione le istruzioni non dipendenti;

• registri ombra: si usano copie di registri su cui

memorizzare temporaneamente i dati;

• register renaming: si usano nuovi registri, non

specificati dal codice.

• multi-threading (hyper-threading): si eseguono

più programmi contemporaneamente,

necessario duplicare i registri. Primo passo

verso processori multicore.

(Architettura degli Elaboratori)

Le dipendenze vengono rilevate mediante una

tabella delle dipendenze (scoreboard):

memoria interna al processore che conta

per ogni registro,

le operazioni, di lettura e scrittura, in sospeso su

quel registro.

63 / 81

Problematiche per i processori con pipeline:

• il processore impiega alcuni cicli di clock per

valutare la condizione,

• nel frattempo, non sa quali istruzioni eseguire.

Due possibili soluzioni:

• stall non si inizia alcuna istruzione: corretta ma

con decadimento delle prestazioni;

• si fa una predizione di salto: taken, not taken, si

inizia l’esecuzione condizionata di alcune

istruzioni:

esecuzione annullata

se la previsione si rivela 64 / 81

(Architettura degli Elaboratori)

Processore

Tecniche per la predizione

di salto

Esecuzione Speculativa:

Due classi:

• predizione statica, sul codice:

•

•

semplice: si eseguono i salti indietro,

suggerite dal compilatore, programmatore: istruzioni

di salto con suggerimento,

• predizione dinamica, sull’esecuzione:

viene usata una history table (ricorda il

comportamento passato di alcune istruzioni di

salto, poche istruzioni, pochi bit),

In un programma numerose istruzioni di salto: una

buona predizione di salto è fondamentale per le

prestazioni.

(Architettura degli Elaboratori)

Processore

65 / 81

nel caso di salto condizionato,

non si tenta la predizione ma

si eseguono entrambe le possibili continuazioni del

programma.

Pur di alimentare il processore, si eseguono anche

alcune istruzioni che sicuramente verranno scartate.

Problemi:

• l’esecuzione deve essere reversibile: registri

ombra, istruzioni che generano trap,

• evitare l’esecuzione di istruzioni costose:

SPECULATIVE LOAD.

(Architettura degli Elaboratori)

Esecuzione Speculativa

evensum = 0;

evensum = 0;

oddsum = 0;

oddsum = 0;

i = 0;

while (i < limit) {

La differenza di velocità tra processore e memoria è

aumenta col tempo.

while (i < limit)

k = i * i * i;

k = i * i * i;

if ((i/2) * 2) = = 0)

if ((i/2) * 2) == 0)

T

evensum = evensum + k;

L’accesso in memoria operazione costosa:

il processore deve attendere il dato

per più di una decina di cicli di clock.

F

evensum = evensum + k;

else

66 / 81

La memoria principale

troppo lenta

i = 0;

i >= limit

Processore

oddsum = oddsum + k;

oddsum = oddsum + k;

i = i + 1;

i = i + 1;

Memoria Cache: memoria piccola e veloce:

contiene i dati utilizzati più frequentemente.

}

(a)

(Architettura degli Elaboratori)

(b)

Processore

67 / 81

(Architettura degli Elaboratori)

Processore

68 / 81

La memoria cache

Cache a più livelli

Aumenta il divario di velocità tra CPU RAM;

per evitare cache miss troppe costose, un secondo

livello di cache:

• più ampio

• tecnologia meno costosa

• più lento

• contiene un sovrainsieme della memoria di

primo livello

Spesso sono presenti 3 livelli di cache.

Funzionamento:

• prima si cerca il dato in cache (cache hit),

• in caso di fallimento (cache miss): si carica il

dato in cache dalla memoria principale.

Migliori prestazioni solo con numerosi cache hit.

Esempio - Sandy Bridge: livello 1: 32KB; livello 2:

256KB, livello 3: 1–20MB;

(Architettura degli Elaboratori)

Processore

69 / 81

(Architettura degli Elaboratori)

Split cache

l’IFU accede alle istruzioni

l’unità Dispatch/Execute accede ai dati

CPU

package

CPU chip

L1-I

Processor

board

L1-D

Unified

L2

cache

Keyboard

controller

Unified

L3 cache

Graphics

controller

Split L1 instruction and data caches

(Architettura degli Elaboratori)

Processore

70 / 81

Esempio di configurazione

cache divisa in due parti: dati e istruzioni

• normalmente cache L1 (di primo livello)

• permette di parallelizzare l’accesso in memoria

•

•

Processore

71 / 81

(Architettura degli Elaboratori)

Processore

Main

memory

(DRAM)

Disk

controller

Board-level cache (SRAM)

72 / 81

Valutazione delle

prestazioni

CPU Corei-7, Architett.

Sandy-Bridge

Le velocità di un calcolatore con processore

superscalare dipende fortemente da quanto viene

sfruttato il potenziale parallelismo:

• percentuale delle istruzioni non bloccate per

dipendenze,

• percentuale di predizioni di salto corrette,

• percentuale cache hit.

Queste percentuali difficilmente valutabili a tavolino,

dipendono dal tipo di programmi eseguiti.

Una corretta valutazione delle prestazione può

essere

fatto solo tramiteProcessore

test.

(Architettura degli Elaboratori)

73 / 81

Architettura Sandy Bridge

(Architettura degli Elaboratori)

Processore

• multicore, hyper-threading;

• processore CISC con cuore RISC;

• i primi stadi della pipeline traducono codice

CISC in istruzioni RISC,

• depositate nella cache L0;

• più simile al Pentium II (P6) che al Pentium 4;

• risparmio energetico;

• predizione di salto sofisticata (algoritmo segreto)

• controllore memoria, cache L3 (condivisa) e

processore grafico integrati nello stesso chip;

• nuove istruzioni grafiche AVX (Advanced Vector

(Architettura degli Elaboratori)

Processore

74 / 81

Extensions);

Sandy Bridge, pipeline

75 / 81

(Architettura degli Elaboratori)

Processore

76 / 81

Sandy bridge, chip

Architettura Cortex A9

• Progettata ARM ltd, realizzata da vari

•

•

•

•

(Architettura degli Elaboratori)

Processore

77 / 81

costruttori;

core che viene integrato in SoC (System on

Chip), (calcolatori su un singolo chip)

implemeta istruzione ARMv7

strutturalmente abbastanza simile al Sandy

Bridge,

manca lo stadio iniziale di traduzione istruzioni

CISC -> RISC.

(Architettura degli Elaboratori)

Architettura Cortex A9

(Architettura degli Elaboratori)

Processore

Processore

78 / 81

Architettura Cortex A9

79 / 81

(Architettura degli Elaboratori)

Processore

80 / 81

Architettura Cortex A9

(Architettura degli Elaboratori)

Processore

81 / 81