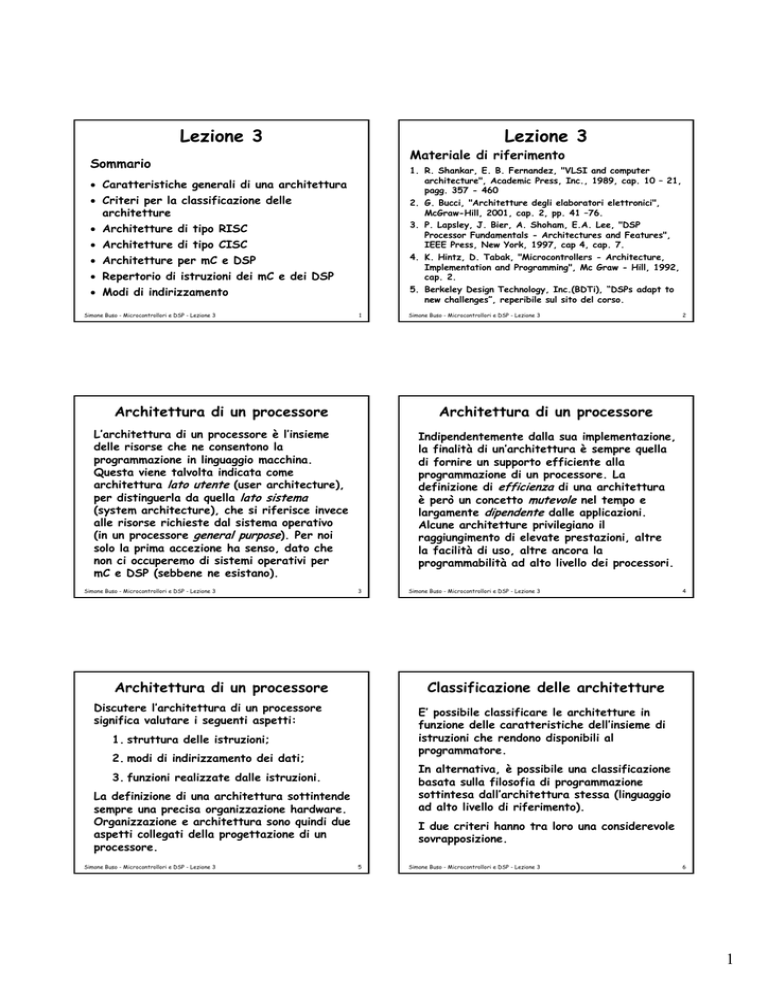

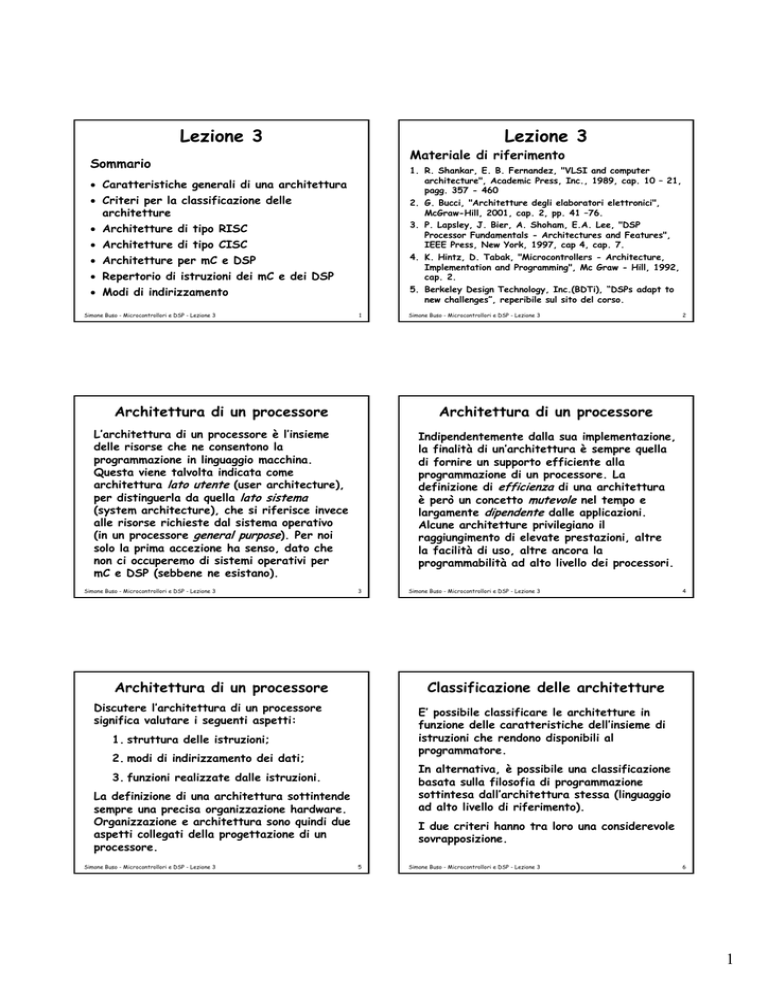

Lezione 3

Lezione 3

Materiale di riferimento

Sommario

1. R. Shankar, E. B. Fernandez, "VLSI and computer

architecture", Academic Press, Inc., 1989, cap. 10 – 21,

pagg. 357 - 460

2. G. Bucci, "Architetture degli elaboratori elettronici",

McGraw-Hill, 2001, cap. 2, pp. 41 –76.

3. P. Lapsley, J. Bier, A. Shoham, E.A. Lee, "DSP

Processor Fundamentals - Architectures and Features",

IEEE Press, New York, 1997, cap 4, cap. 7.

4. K. Hintz, D. Tabak, "Microcontrollers - Architecture,

Implementation and Programming", Mc Graw - Hill, 1992,

cap. 2.

5. Berkeley Design Technology, Inc.(BDTi), “DSPs adapt to

new challenges”, reperibile sul sito del corso.

• Caratteristiche generali di una architettura

• Criteri per la classificazione delle

architetture

• Architetture di tipo RISC

• Architetture di tipo CISC

• Architetture per mC e DSP

• Repertorio di istruzioni dei mC e dei DSP

• Modi di indirizzamento

Simone Buso - Microcontrollori e DSP - Lezione 3

1

Simone Buso - Microcontrollori e DSP - Lezione 3

Architettura di un processore

Architettura di un processore

L’architettura di un processore è l’insieme

delle risorse che ne consentono la

programmazione in linguaggio macchina.

Questa viene talvolta indicata come

architettura lato utente (user architecture),

per distinguerla da quella lato sistema

(system architecture), che si riferisce invece

alle risorse richieste dal sistema operativo

(in un processore general purpose). Per noi

solo la prima accezione ha senso, dato che

non ci occuperemo di sistemi operativi per

mC e DSP (sebbene ne esistano).

Indipendentemente dalla sua implementazione,

la finalità di un’architettura è sempre quella

di fornire un supporto efficiente alla

programmazione di un processore. La

definizione di efficienza di una architettura

è però un concetto mutevole nel tempo e

largamente dipendente dalle applicazioni.

Alcune architetture privilegiano il

raggiungimento di elevate prestazioni, altre

la facilità di uso, altre ancora la

programmabilità ad alto livello dei processori.

Simone Buso - Microcontrollori e DSP - Lezione 3

3

Architettura di un processore

4

Classificazione delle architetture

Discutere l’architettura di un processore

significa valutare i seguenti aspetti:

E’ possibile classificare le architetture in

funzione delle caratteristiche dell’insieme di

istruzioni che rendono disponibili al

programmatore.

1. struttura delle istruzioni;

2. modi di indirizzamento dei dati;

In alternativa, è possibile una classificazione

basata sulla filosofia di programmazione

sottintesa dall’architettura stessa (linguaggio

ad alto livello di riferimento).

3. funzioni realizzate dalle istruzioni.

La definizione di una architettura sottintende

sempre una precisa organizzazione hardware.

Organizzazione e architettura sono quindi due

aspetti collegati della progettazione di un

processore.

Simone Buso - Microcontrollori e DSP - Lezione 3

Simone Buso - Microcontrollori e DSP - Lezione 3

2

I due criteri hanno tra loro una considerevole

sovrapposizione.

5

Simone Buso - Microcontrollori e DSP - Lezione 3

6

1

Classificazione delle architetture

Classificazione delle architetture

Le caratteristiche di maggiore interesse per

un insieme di istruzioni sono le seguenti:

La simmetria di un insieme di istruzioni

indica il grado di uniformità dei modi di

indirizzamento tra le diverse istruzioni. Un

insieme di istruzioni si dice simmetrico

quando esistono poche differenze nei modi

di indirizzamento possibili per le varie

istruzioni e quindi quando tutti gli operatori

possono essere applicati a tutti i tipi di

dati. Un set di istruzioni simmetrico implica

quindi una maggiore uniformità nei formati

delle istruzioni.

•

•

•

•

•

•

•

•

Simmetria

Ortogonalità

Compattezza

Flessibilità

Velocità di esecuzione

Costo

Facilità di debugging

Corrispondenza con linguaggi di alto livello

Simone Buso - Microcontrollori e DSP - Lezione 3

7

Classificazione delle architetture

La compattezza delle istruzioni indica la

dimensione del codice macchina che viene

generato nella compilazione di un dato

programma. Alcune architetture favoriscono

la compattezza più di altre (relazione con la

complessità delle istruzioni).

La flessibilità indica invece la facilità con la

quale è possibile modificare l’insieme di

istruzioni, e.g. aggiungendone di nuove in

una successiva versione del processore.

Questo consente di avere un formato di

istruzioni unico e costante, favorendo

l’allineamento delle stesse in memoria e

quindi la velocità del processore.

9

Classificazione delle architetture

Simone Buso - Microcontrollori e DSP - Lezione 3

10

Classificazione delle architetture

La facilità di debugging indica la leggibilità

del codice generato dalla

compilazione/scrittura di un programma.

Questa è importante per la ri-usabilità e

portabilità del codice.

La velocità di esecuzione è chiaramente un

parametro fondamentale per una

architettura. Questa è sempre in relazione

con il costo del processore.

Si parla di costo di una architettura

intendendo il costo del processore che la

pone in atto. Questo a sua volta è funzione

della tecnologia impiegata, della complessità

dei circuiti da realizzare (area di silicio

richiesta) e del volume di produzione atteso.

Simone Buso - Microcontrollori e DSP - Lezione 3

8

Classificazione delle architetture

L’ortogonalità delle istruzioni indica

direttamente la regolarità nella struttura

della parola che rappresenta un’istruzione.

Un set di istruzioni ortogonali presenta

parole della stessa lunghezza, in cui le

dimensioni dei campi associati alle specifiche

funzioni (e.g OPCODE) sono sempre le

stesse.

Simone Buso - Microcontrollori e DSP - Lezione 3

Simone Buso - Microcontrollori e DSP - Lezione 3

E’ anche associata alla maggiore o minore

somiglianza del codice macchina con un

linguaggio di alto livello (corrispondenza).

Alcune architetture rendono disponibili

costrutti tipici dei linguaggi ad alto livello

(cicli for, repeat, etc.).

11

Simone Buso - Microcontrollori e DSP - Lezione 3

12

2

Classificazione delle architetture

Architetture RISC

Sulla base dei parametri appena discussi una

possibile classificazione delle architetture è

la seguente:

Le architetture RISC sono quelle nelle quali

le istruzioni sono meno numerose (poche

decine) e più semplici possibile. La semplicità

è relativa sia al formato che alle

funzionalità delle istruzioni.

Queste hanno tutte le stesse dimensioni (es.

16 bit) e struttura di parola identica.

• Architetture RISC

Basate su registri

Basate su accumulatore/stack (obsolete)

• Architetture di tipo CISC

Von Neumann estese

Orientate ad oggetti/linguaggi

Siccome la decodifica (quasi sempre cablata)

risulta molto semplice, le architetture RISC

permettono spesso l’esecuzione di tutte le

istruzioni in un solo ciclo macchina.

Orientate alla sicurezza (poco diffuse)

Simone Buso - Microcontrollori e DSP - Lezione 3

13

Architetture RISC

Architetture RISC

L’area risparmiata consente la realizzazione

di strutture come banchi di registri o

memorie cache, che accelerano

ulteriormente l’esecuzione dei programmi.

L’organizzazione della CPU è quindi quasi

sempre del tipo a molti registri.

15

Simone Buso - Microcontrollori e DSP - Lezione 3

Architetture CISC

Architetture CISC

Le architetture di tipo CISC sono

caratterizzate da insiemi molto numerosi di

istruzioni (anche centinaia), di struttura

variabile ed, in genere, piuttosto complessa.

La decodifica è in questo caso spesso

microprogrammata, per semplificare la

realizzazione dell’unità di controllo.

Inoltre l’esecuzione delle istruzioni richiede

quasi sempre più cicli macchina.

Architetture CISC sono comuni a molti

processori per uso generico (fino ai primi

anni ‘90), piuttosto rare nei mC e DSP.

Le architetture di tipo CISC sono realizzate

in diverse varianti. La versione più comune

sottende un’organizzazione hardware di tipo

Von Neumann, con eventuali potenziamenti

(si parla di architetture Von Neumann

estese). I principali interventi di

miglioramento consistono nell’introduzione di:

1. memorie cache;

2. coprocessori;

Simone Buso - Microcontrollori e DSP - Lezione 3

14

Le prime realizzazioni di processori RISC

avevano una organizzazione della CPU basata

su un accumulatore e/o un piccolo stack.

Queste avevano istruzioni senza operandi,

quindi di massima semplicità, ma

comportavano un intenso traffico di dati da

e per la memoria.

Le prestazioni delle CPU sono aumentate nel

tempo molto più rapidamente di quelle delle

memorie che sono il “collo di bottiglia” di un

processore. Le organizzazioni a stack sono

quindi state progressivamente abbandonate.

La semplificazione dell’unità di controllo

prodotta dalle architetture RISC comporta

un considerevole risparmio di area di silicio

(riduzione dei costi).

Simone Buso - Microcontrollori e DSP - Lezione 3

Simone Buso - Microcontrollori e DSP - Lezione 3

16

3. blocchi di debugging (funzioni di

“program tracing”).

17

Simone Buso - Microcontrollori e DSP - Lezione 3

18

3

Architetture CISC

Architetture per mC e DSP

Specialmente nel passato (anni ‘80), si sono

avute realizzazioni di processori orientate ai

linguaggi o agli oggetti. I primi miravano ad

interpretare direttamente a livello hardware

le istruzioni di qualche linguaggio ad alto

livello (LISP, FORTH, ..).

I processori orientati agli oggetti tentavano

invece di rendere astratta l’organizzazione a

basso livello del processore, lasciando

all’utente la possibilità di creare oggetti di

varie classi (es. istruzioni) con una

struttura predefinita a livello hardware.

Le architetture di alcuni mC di progettazione

più datata (anni ’70) sono di tipo CISC (es.

Intel 8XC196, Renesas H8S, …). Si tratta

di processori estremamente diffusi, ma

raramente utilizzati in prodotti di nuova

concezione.

Simone Buso - Microcontrollori e DSP - Lezione 3

Più recentemente si sono andate affermando

architetture di tipo RISC, specialmente per i

dispositivi destinati ad usi intensivi (controllo

real-time). Le caratteristiche di questi

processori sono spesso equivalenti a quelle di

un DSP (a virgola fissa).

19

Simone Buso - Microcontrollori e DSP - Lezione 3

20

Architetture per mC e DSP

Architetture per mC e DSP

Le architetture per DSP sono normalmente

ispirate alla filosofia RISC, quindi sono

sostenute da CPU che prevedono un notevole

numero di registri e sistemi di controllo

cablati.

I DSP presentano tuttavia caratteristiche

che li differenziano notevolmente dai

processori RISC di tipo general-purpose.

Il formato delle istruzioni è compatto, ma

include numerosi campi, per aumentare la

potenza delle singole istruzioni.

Questo approccio tende a rendere il

repertorio di istruzioni asimmetrico e non

ortogonale, con conseguenti difficoltà nella

programmazione e successivo debugging.

Specialmente le prime realizzazioni su larga

scala (Texas Instruments, Motorola), si

caratterizzavano per la complessità del

linguaggio assembly e la impossibilità

materiale di ottenere una efficiente

programmazione ad alto livello (scarsa qualità

dei compilatori).

Simone Buso - Microcontrollori e DSP - Lezione 3

21

Architetture per mC e DSP

Simone Buso - Microcontrollori e DSP - Lezione 3

Architetture per mC e DSP

L’aumento della complessità degli algoritmi

usati nelle applicazioni più recenti (anni ‘90)

dei DSP (e.g. telefonia mobile) ha spinto

verso la realizzazione di architetture più

facilmente programmabili.

DSP convenzionale: una

istruzione complessa è

ripetuta ntaps volte.

DSP con architettura

VLIW: molte semplici

istruzioni vengono

eseguite in parallelo.

All’atto della creazione

del codice macchina,

sono collocate all’interno

di una singola VLIW.

Una soluzione molto utilizzata è denominata

VLIW (Very Long Instruction Word). Questa

architettura combina molte (4, 8) istruzioni

semplici in una sola macro-istruzione, che

viene letta tutta in una volta dalla CPU. Le

istruzioni componenti vengono eseguite in

parallelo, quindi in un solo ciclo (risc → cisc).

Simone Buso - Microcontrollori e DSP - Lezione 3

22

23

Simone Buso - Microcontrollori e DSP - Lezione 3

24

4

Architetture per mC e DSP

Architetture per mC e DSP

Il fatto che le istruzioni base siano molto

semplici rende più facile la realizzazione di

compilatori efficienti. Il fatto che la

potenza delle singole istruzioni si riduca,

richiede però più memoria per il codice

compilato. Questo si traduce in un aumento

di costo.

Sono stati tentati approcci differenti:

a) istruzioni a lunghezza variabile;

b) approccio SIMD;

Alcuni DSP presentano architetture con

istruzioni a lunghezza variabile.

Le istruzioni di tipo aritmetico, usate

all’interno di algoritmi di calcolo, sono di tipo

VLIW, per favorire il parallelismo e

flessibilità nell’indirizzamento dei dati.

Invece, istruzioni di tipo diverso (e.g.

istruzioni di controllo, manipolazione di bit)

sono di formato più compatto, per favorire

una minore occupazione di memoria.

c) processori “su misura”.

Simone Buso - Microcontrollori e DSP - Lezione 3

25

Architetture per mC e DSP

Simone Buso - Microcontrollori e DSP - Lezione 3

26

Architetture per mC e DSP

Altri DSP fanno uso di architetture SIMD

(Single Instruction, Multiple Data). Queste

consentono l’esecuzione in parallelo della

stessa istruzione su dati differenti,

incrementando così le prestazioni.

Questo approccio, in alcuni casi (serie Texas

C64, AD Blackfin o Tiger SHARC) viene

combinato con il VLIW. L’obiettivo in questo

caso è l’incremento massimo della potenza di

calcolo.

Benchmark: occupazione di memoria

Simone Buso - Microcontrollori e DSP - Lezione 3

27

Architetture per mC e DSP

28

Repertorio delle istruzioni nei DSP

Il repertorio delle istruzioni di un DSP, è

fortemente orientato al calcolo e include una

ampia gamma di funzioni aritmetiche, logiche

e matematiche.

Infine, per alcuni prodotti vengono utilizzati

DSP su misura (licensable cores). In questo

caso l’utilizzatore può definire un repertorio

di istruzioni ottimizzato per la sua specifica

applicazione, arrivando anche a personalizzare

l’organizzazione hardware del chip.

Per velocizzare l’esecuzione di alcuni tipici

algoritmi (DFT, filtri FIR,…), vengono inoltre

offerti modi di indirizzamento specifici.

Benchè questo approccio porti a realizzazioni

estremamente ottimizzate (nessuna risorsa

viene sprecata) introduce tempi di sviluppo

molto lunghi, costi elevati e scarsa

flessibilità.

Simone Buso - Microcontrollori e DSP - Lezione 3

Simone Buso - Microcontrollori e DSP - Lezione 3

Tra una famiglia di DSP e un’altra, possono

esserci differenze anche notevoli nel

repertorio delle istruzioni: alcuni elementi

sono però molto comuni.

29

Simone Buso - Microcontrollori e DSP - Lezione 3

30

5

Istruzioni aritmetiche nei DSP

Istruzioni aritmetiche nei DSP

La moltiplicazione è sempre presente e viene

eseguita in un solo ciclo, spesso in diverse

modalità (intera, frazionaria, con o senza

segno). E’ possibile far seguire alla

moltiplicazione una operazione di shift e/o

somma sull’accumulatore, che vengono eseguiti

nello stesso ciclo macchina. Alla

moltiplicazione è dedicato un apposito circuito

esterno alla ALU e denominato MAC.

In alcune unità è disponibile anche l’istruzione

di divisione, ma, di norma, questa non è

presente a livello hardware.

Alcuni DSP presentano la possibilità di

operare in aritmetica saturata, mettendo al

riparo da effetti indesiderati dovuti a

overflow dell’accumulatore, causati ad es. da

ripetute istruzioni di moltiplicazione e somma

(MAC).

Sempre per agevolare lo sviluppo di algoritmi

di calcolo, anche le istruzioni di shift logico

e aritmetico sono molto flessibili. Fanno

spesso uso di un circuito apposito detto

barrel shifter. Esso rende possibile scalare

agevolmente i dati durante l’elaborazione.

Simone Buso - Microcontrollori e DSP - Lezione 3

31

Istruzioni aritmetiche nei DSP

32

Istruzioni aritmetiche nei DSP

a7 a6 a5 a4 a3 a2 a1 a0 Operando a 8 bit

Molti DSP consentono al programmatore la

scelta della strategia con cui gestire le

operazioni che comportano la riduzione del

numero di bit dedicati alla rappresentazione

di un dato (es: right shift). Le opzioni

sono:

1. troncamento;

b3 b2 b1 b0

Scalo su 4 bit

b3b2b1b0 = a7a6a5a4

b3b2b1b0 = a7a6a5a4 + a3

2. arrotondamento (elimina l’errore

sistematico introdotto dalle operazioni

di troncamento);

3. arrotondamento convergente.

Simone Buso - Microcontrollori e DSP - Lezione 3

Simone Buso - Microcontrollori e DSP - Lezione 3

troncamento

arrotondamento

Arrotondamento convergente

b3b2b1b0 = a7a6a5a4 + a3

b3b2b1b0 = a7a6a5a4 + a4

33

se a3a2a1a0 <> 10002

se a3a2a1a0 = 10002

Simone Buso - Microcontrollori e DSP - Lezione 3

Istruzioni aritmetiche nei DSP

Repertorio delle istruzioni nei DSP

Nel repertorio delle istruzioni aritmetiche

sono talvolta presenti funzioni come:

a) radice quadrata;

b) funzioni trigonometriche (sinx, cosx).

Queste non sono però mai realizzate a livello

hardware e quindi richiedono molti cicli

macchina per essere calcolate.

In aggiunta alle istruzioni che realizzano le

operazioni aritmetiche fondamentali, tutti i

DSP dispongono di ulteriori istruzioni che

consentono ad esempio:

1. spostamento di dati;

2. confronto rapido di dati;

3. manipolazione di bit;

4. ripetizione di segmenti di codice;

5. salti, chiamate a subroutine;

6. emulazione di aritmetica a virgola mobile

(per i DSP a virgola fissa).

Risulta alle volte più conveniente ricorrere ad

approssimazioni polinomiali delle funzioni

suddette, che possono essere calcolate in

modo molto efficiente.

Simone Buso - Microcontrollori e DSP - Lezione 3

35

Simone Buso - Microcontrollori e DSP - Lezione 3

34

36

6

Repertorio delle istruzioni nei mC

Repertorio delle istruzioni nei mC

Storicamente, i mC hanno sempre avuto un

repertorio di istruzioni orientato al controllo

di processi più che al calcolo (elaborazione

numerica di segnali).

Molto spesso le funzioni aritmetiche più

avanzate (e.g. moltiplicazione) erano

presenti solo a livello di istruzione (i.e. non

c’era il moltiplicatore hardware).

L’esecuzione di queste istruzioni richiedeva

quindi numerosi cicli macchina.

Questo rendeva spesso problematica la

realizzazione di controlli real-time.

Attualmente, l’organizzazione dei mC (di alta

gamma) ricalca quella dei DSP a virgola fissa

di una decina di anni fa.

Il repertorio delle istruzioni di questi

dispositivi è quindi simile a quello di un DSP

(filosofia RISC, elevata regolarità,

programmabilità ad alto livello, …) e spesso

è presente il moltiplicatore hardware.

Gli accorgimenti descritti in precedenza per

l’incremento delle prestazioni (parallelismo)

non sono però riprodotti nei mC,

essenzialmente per questioni di costo.

Simone Buso - Microcontrollori e DSP - Lezione 3

37

Simone Buso - Microcontrollori e DSP - Lezione 3

Repertorio delle istruzioni nei mC

Struttura delle istruzioni

Per le applicazioni in tempo reale e

comunque in ambito industriale, spesso i mC

vengono preferiti ai DSP perché includono al

loro interno tutte le periferiche necessarie

all’interfacciamento con i tipici sistemi da

controllare (azionamenti, convertitori di

potenza, etc.).

Inoltre sono spesso più economici, dissipano

minore potenza (adatti alle applicazioni

embedded), e sono assai meno suscettibili ai

disturbi elettromagnetici tipici dell’ambiente

industriale.

Tanto nei mC che nei DSP le istruzioni hanno

strutture abbastanza regolari.

Simone Buso - Microcontrollori e DSP - Lezione 3

Tipicamente sono disponibili istruzioni fino a

tre operandi. La struttura della instruction

word (IW) è spesso funzione dell’opcode (si

riduce però la velocità di decodifica).

Il campo OPCODE è suddiviso in sotto-campi

con funzioni specifiche.

OPCODE

39

operando #2

operando #1

operando #3

Simone Buso - Microcontrollori e DSP - Lezione 3

Struttura delle istruzioni

Modi di indirizzamento

E’ possibile sviluppare architetture con

istruzioni senza operandi (macchine a stack).

Esse risultano però poco efficienti e sono

ormai state abbandonate.

Le istruzioni con un solo operando del tipo:

ADD X

sottintendono la presenza di un registro

accumulatore.

Nelle organizzazioni delle CPU a molti

registri diventano possibili istruzioni come:

ADD X, Y, Z

I più comuni modi di indirizzamento dei dati

sono:

Simone Buso - Microcontrollori e DSP - Lezione 3

38

40

• immediato: l’operando è esplicitamente

inserito nell’IW;

• a registro: l’operando è in un registro

della CPU (specificato nella IW);

• diretto o assoluto: l’istruzione contiene

l’indirizzo in memoria dell’operando;

• indiretto: l’istruzione contiene l’indirizzo

in memoria dell’indirizzo dell’operando

(puntatore).

41

Simone Buso - Microcontrollori e DSP - Lezione 3

42

7

Modi di indirizzamento

Modi di indirizzamento

DSP e mC spesso utilizzano unità per la

generazione degli indirizzi (AGU) che sono

esterne all’ALU e lavorano in background.

Ciò rende possibili modi di indirizzamento

anche più sofisticati e efficienti:

• indiretto su registro: l’indirizzo del

puntatore è contenuto in un registro

(sono possibili incrementi, offset, …);

Altri modi di indirizzamento, molto comuni

nei mC e nei DSP sono:

• indiretto con auto-incremento: l’IW

contiene l’indirizzo di un puntatore, cui

viene automaticamente sommato ±1

(talora ±2);

• indiretto con offset (indicizzato): il

puntatore viene sommato ad una costante

inclusa nell’IW per formare l’indirizzo del

dato.

• circolare: facilita la gestione di vettori di

dati (tipico dei DSP);

• a bit rovesciati: per la DFT (solo DSP).

Simone Buso - Microcontrollori e DSP - Lezione 3

43

Simone Buso - Microcontrollori e DSP - Lezione 3

Indirizzamento circolare

X0 X1 X2 X3

r

w

puntatore puntatore di

di lettura scrittura

r

X1 X2

X0

X3

w

Indirizzamento a bit rovesciati

Quando uno dei

puntatori (r o w)

raggiunge la fine

del vettore deve

essere resettato.

Quando uno dei puntatori

(r o w) raggiunge la fine

del vettore passa in modo

automatico alla posizione di

partenza.

Simone Buso - Microcontrollori e DSP - Lezione 3

44

45

x0

x1

x2

x3

x4

x5

x6

x7

Y0

Y1

Y2

Y3

Y4

Y5

Y6

y7

0

1

2

DFT

3

4

5

6

7

=

=

=

=

=

=

=

=

X[000]

X[100]

X[010]

X[110]

X[001]

X[101]

X[011]

X[111]

=

=

=

=

=

=

=

=

X0

X4

X2

X6

X1

X5

X3

X7

X0

X1

X2

X3

X4

X5

X6

X7

La lettura a bit

rovesciati di una

sequenza ordinata

produce proprio

la sequenza di

uscita X della

DFT: è allora

immediato creare

il vettore

ordinato Y.

Simone Buso - Microcontrollori e DSP - Lezione 3

000

001

010

011

100

101

110

111

=

=

=

=

=

=

=

=

0

1

2

3

4

5

6

7

000

100

010

110

001

101

011

111

=

=

=

=

=

=

=

=

0

4

2

6

1

5

3

7

46

8