Memorie a semiconduttore

I dispositivi per l’immagazzinamento dell’informazione

sono necessari in tutti i sistemi elettronici.

PC, Workstation, Mainframe.

Sistemi Embedded.

Si prevede un incremento del mercato delle memorie

2002

47 Miliardi di $

2007

86,7 Miliardi di $

Classificazione

Varie modalità di classificazione:

Dimensione: Circuito ------------------ Celle di memoria.

Chip ---------------------- Byte e multipli.

Sistema ------------------ Word.

Tempi d’accesso: In lettura, In scrittura e Tempi di ciclo.

Funzionalità: Solo Lettura, Lettura/Scrittura.

Modalità d’accesso: Casuale, Ordinato.

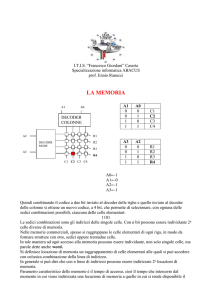

Architettura

Memoria di N-word

ciascuna composta da M-bit.

Decoder di riga a K=log2(N)

ingressi

# connessioni troppo elevato

considerandone una per ogni

word.

Struttura molto lunga e

stretta. Layout difficile.

Decoder di colonna e più

word per riga.

Struttura regolare.

Memoria di grandi dimensioni

Partizionamento in blocchi.

ROM

Memorie che mantengono l’informazione “per sempre”.

Programmabili una sola volta.

Mask-Programmed ROM:

Programmable ROM:

Programmate in fase di realiazzazione

dell’integrato attraverso maschere.

Programmabile con opportuni

segnali elettrici attraverso

kit-programmer.

Memorizzazione dell’informazione

nella topologia del circuito (presenza o Memorizzazione dell’informazione

assenza di diodi o transistori).

nella topologia del circuito

(bruciatura o no di fusibili).

NVRWM (1)

EPROM

Fa uso del transistor a Floating Gate

Normalmente nel floating-gate non

c’è carica.

WL=1, la BL si

scarica

“0” in

uscita

Iniezione elettroni nel floating gate e

innalzamento della soglia logica del

transistor. (AHEI)

WL=1, la BL

non si scarica

“1” in

uscita

Rimozione degli elettroni esponendo il chip per

qualche decina di minuti a raggi UV.

Cancellazione

NVRWM (2)

EEPROM

Fa uso di un transistor a Floating Gate modificato (FLOTOX).

Programmabili e cancellabili elettricamente per Fowler-Nordheim Tunneling.

VANTAGGI

SVANTAGGI

Cancellabili elettricamente.

Soglia logica molto variabile.

Cancellazione on-system.

Dimensione cella grande.

Cancellazione byte per byte.

NVRWM (3)

FLASH

Fa uso di un transistor a Floating Gate modificato (ETOX).

Programmazione per AHEI e cancellazione per Fowler-Nordheim Tunneling.

Unisce i vantaggi delle EPROM e delle EEPROM:

Elettricamente programmabili.

Dimensione cella ridotta.

Cancellazione di pagine o anche singoli byte.

NWRWM (4)

Riassumendo….

EPROM

EEPROM

FLASH

Write Time

> 10 ms

> 1ms

1-100 µs

Erase Time

> 10 min

> 100 ms

> 100 ms

Data Retention 10 years

> 40 years

> 100 years

VRWM (1)

Memorie a lettura/scrittura volatili.

• Mantengono l’informazione fintanto che è presente

l’alimentazione.

• A differenza delle NVRWM hanno tempi di scrittura

paragonabili a quelli di lettura.

Accesso Casuale

Accesso Ordinato

• SRAM

• LIFO, FIFO, Shift Register

• DRAM

• CAM

VRWM (2)

SRAM

• L’ informazione è memorizzata in circuiti bistabili.

Lettura:

Scrittura:

Attivazione della WL

e dato disponibile

sulla bitline (anche il

dato negato).

Attivazione della WL

e forzatura del dato

nel bistabile.

Per ridurre l’occupazione di area i PMOS possono essere sostituiti da:

• Resistori.

• Transistor Thin-Film.

VRWM (3)

Async SRAM: Segnali di indirizzamento non coordinati

con il clock di sistema. Tempi d’attesa dei dati molto

lunghi.

Sync SRAM: Segnali sincronizzati con il clock.

Funzionamento più affidabile e veloce

Pipeline Burst SRAM: Sincrona con trasferimento dati

veloce attraverso cicli burst.

Dual Port SRAM: Doppia porta d’accesso con capacità

di lettura e scrittura indipendenti.

VRWM (4)

DRAM

• L’ informazione è memorizzata in condensatori che necessitano di

refresh periodico della carica.

Lettura:

Attivazione della

RWL (WL) e dato

disponibile sulla BL2

(BL).

Scrittura:

Attivazione della

WWL (WL) e carica

della C di gate di 2

(semplice

condensatore).

Sforzo notevole nella riduzione della dimensione delle celle (es. Trench

Capacitor) con tempi d’accesso e consumi però maggiori rispetto le SRAM.

VRWM (5)

FPM DRAM: Ogni riga della memoria è vista come

pagina. Si accede consecutivamnte alle word della riga.

EDO RAM: Si accede alle colonne successive mentre si

sta ancora prelevando il dato dalla colonna precedente.

Sync DRAM: Sincrona a banchi multipli per permettere

accessi, relativi a diverse righe, più veloci.

DRDRAM: Sviluppata da Rambus si discosta dalle

comuni DRAM per la particolare architettura adottata

che permette performance molto elevate.

Double Data Rate Sync DRAM: Garantisce rispetto le

SDRAM il trasporto dei dati su entrambi i fronti del

clock.

VRWM (6)

CAM

Memoria volatile ad accesso non casuale.

LETTURA

Scrittura dato da

ricercare nell’input

register.

Bit che costituiscono

la chiave di ricerca.

Segnale di match

per le parole che

soddisfano la chiave

Selezione della

parole per cui c’è

corrispondenza e

trasferimento

nell'Output Register

SCRITTURA

Due comportamenti

possibili:

1. Accesso casuale

2. Tag Register che

indica se la

locazione è

piena o vuota

Gerarchia delle memorie

Divario di prestazioni tra CPU e Memoria.

CPU attende molto tempo prima che arrivino i dati dalla memoria.

Con la gerarchia delle memorie si cerca di minimizzare gli accessi

alla memoria centrale.

Cache

Memoria on-chip alla quale la CPU accede con un unico ciclo di clock.

Tempo medio d’accesso = HIT-RATE • HIT-TIME + MISS-RATE • MISS-TIME

A) CORRISPONDENZA CACHE-MEMORIA PRINCIPALE

- Mapping Completamente Associativo: Ogni dato della memoria

principale può essere memorizzato in una qualsiasi linea della Cache.

- Mapping Diretto: Ogni dato della memoria principale è messo in

corrispondenza fissa (funzione di trasformazione) una linea della Cache.

- Mapping Associativo Ad N Vie: La cache è divisa in set ciscuno contenente N

linee (2-4-8). Ogni blocco della memoria principale può essere memorizzato in una

delle N linee di un set.

B) STRATEGIE DI SCRITTURA

- Write Through: Aggiornamento memoria non appena modifico il dato in Cache.

- Write Back: Aggiornamento memoria solo quando elimino la linea.

C) POLITICA DI SOSTITUZIONE DELLE LINEE

Random, FIFO, LRU...

Conclusioni

Stretta corrispondenza tra tecnologia e

archittettura nello sviluppo delle memorie.

Fondamentale per un buon sistema la scelta

della memoria adeguata.

Continuo aumento del mercato delle memorie.

Nuove tecnologie alla ribalta differnti dal silicio

(magnetomemorie, nanotubi in carbonio…).